STM32H7实现BootLoader内SDRAM的初始化注意事项

电子说

描述

Bootloader

Board:STM32H750_ArtPi

Function Implementation:在 ArtPi 的环境下,实现一个简单的 BootLoader,该 BootLoader 实现了 QSPI 和 SDRAM 功能的初始化,使 App 可以运行在 QSPI 中,并且可以将 SDRAM 当做普通的内部 RAM 使用(但需要注意,仍需要添加 SCB_InvalidateDCache 和 SCB_CleanDCache 等函数来更新缓存,类似于对 AXI SRAM 的操作)。

BootLoader和App实现教程:安富莱_STM32-V7开发板_用户手册,含BSP驱动包设计(V3.5)

注意事项

在 BootLoader 中进行了 MPU 的配置,在 App 中,就无需重复配置;

在 BootLoader 中,最好禁用 I-Cache 和 D-Cache(实际上,我看了一下硬汉的部分代码,实际上,并不强求一定要禁用 I-Cache 和 D-Cache,应该还是根据自己的需求来决定是开启还是关闭);

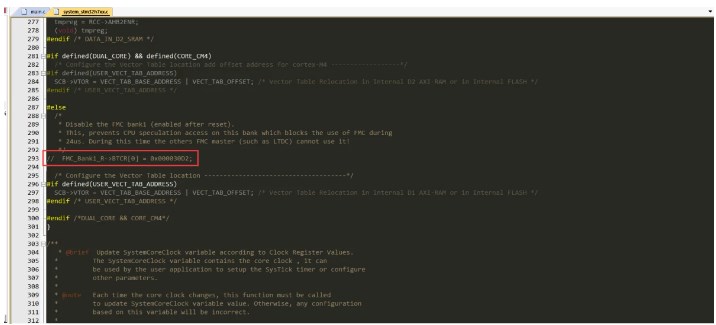

在 BootLoader 中,配置了 FMC,在 App 中,需要注释以下这段代码:

/*

Disable the FMC bank1 (enabled after reset).

This, prevents CPU speculation access on this bank which blocks the use of FMC during

24us. During this time the others FMC master (such as LTDC) cannot use it!

*/

// FMC_Bank1_R->BTCR[0] = 0x000030D2;

此段代码位于 system_stm32h7xx.h 中,在进入 main 函数前执行,因此在 main 函数中进行 Debug 可能无法发现此问题。(群友发现的问题)

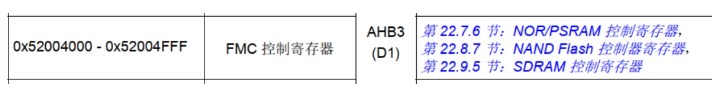

此寄存器地址为 0x52004000,对应 SRAM/NOR-Flash 片选控制寄存器 1(FMC_BCR1)。

#define PERIPH_BASE (0x40000000UL) /*!< Base address of : AHB/APB Peripherals */

#define D1_AHB1PERIPH_BASE (PERIPH_BASE + 0x12000000UL)

#define FMC_R_BASE (D1_AHB1PERIPH_BASE + 0x4000UL)

/* !< FMC Banks registers base address */

#define FMC_Bank1_R_BASE (FMC_R_BASE + 0x0000UL)

#define FMC_Bank1_R ((FMC_Bank1_TypeDef *) FMC_Bank1_R_BASE)

FMC_BCR1 = 0x000030D2; 的作用可以参考 RM0433 22.7.6 节,我们主要关注以下内容:

FMCEN = 0:禁止 FMC 控制器,FMC_BCR2..4 寄存器的 FMCEN 位为“无关”位,只能通过 FMC_BCR1 寄存器使能 ;

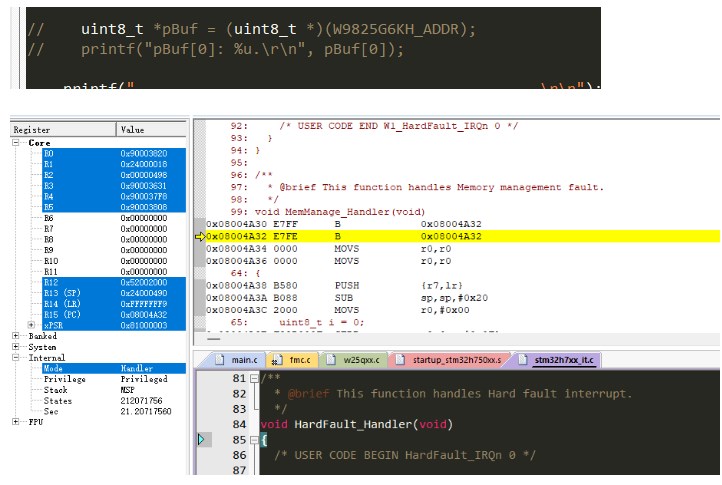

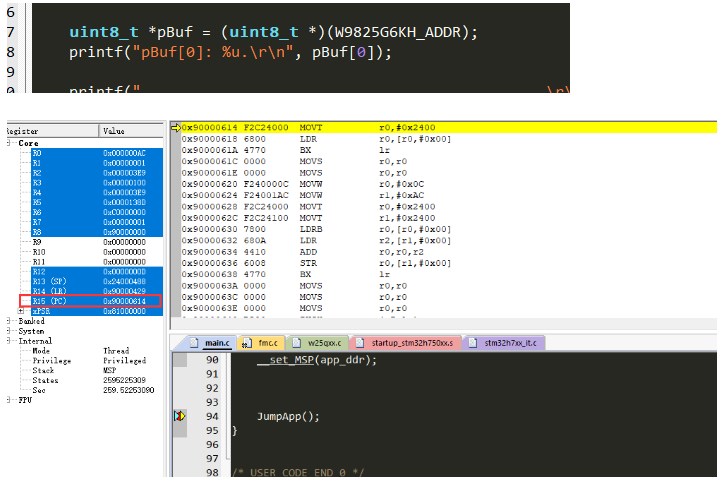

在未注释此行代码时,FMC Bank1会被关闭(复位后启用),阻止 24 \\mu s24μs 内的 FMC 的使用,这会导致 MemMange 错误,导致程序进入 MemMange_Handler(可能会被误认为是 BootLoader 未成功跳转,但其实是跳转了,然后立即产生总线错误)。有趣的是,如果在 BootLoader 内,对 SDRAM 进行一次读或写操作,则不会产生该报警错误。

未进行读写操作,App 进入 MemMange_Handler

进行读写操作,App 不进入MemMange_Handler

在完成以上配置后,就可以在 App 中,像内置 RAM 一样使用 SDRAM。

先在 LinkerScript 内添加以下内容(UNINIT 确保该内存区域不会被初始化为 0):

RW_IRAM7 0xC0000000 UNINIT 0x02000000 { ; RW data - 32MB SDRAM(0xC0000000)

*(.RAM_SDRAM)

}

使用如下:

uint32_t testValue attribute ((section(".RAM_SDRAM")));

-

i坏蛋

2023-07-05

0 回复 举报神来之笔,神来之笔,神来之笔,神来之笔,神来之笔.卡了我好几天的问题一下子解决了// FMC_Bank1_R->BTCR[0] = 0x000030D2;这么关键的东西竟然没个文档 收起回复

i坏蛋

2023-07-05

0 回复 举报神来之笔,神来之笔,神来之笔,神来之笔,神来之笔.卡了我好几天的问题一下子解决了// FMC_Bank1_R->BTCR[0] = 0x000030D2;这么关键的东西竟然没个文档 收起回复

-

STM32H7双核CM4作为Master初始化系统2023-09-20 547

-

不能连接上STM32H7芯片2023-09-18 3020

-

STM32H7技术详解2023-08-01 857

-

STM32H750_FMC_SDRAM初始化流程是怎样的?2022-02-22 1262

-

STM32H750_FMC_SDRAM 初始化流程总结2021-12-29 1337

-

【STM32H7教程】第14章 STM32H7的电源,复位和时钟系统2021-12-09 1369

-

"STM32H7学习继续(STM32H7系列5)第十七章比较实用,以后写程序的时候会用到"2021-12-05 977

-

【STM32H7教程】第21章 STM32H7的NVIC中断分组和配置(重要)2021-12-04 1416

-

STM32H7学习之路继续(stm32H7系列3) GPIO2021-11-30 1264

-

【STM32H7教程】第19章 STM32H7的GPIO应用之按键FIFO2021-11-23 1320

-

Stm32的bootloader和App的编写注意事项有哪些?2021-10-29 2626

-

STM32H7系列芯片及bootloader引导程序2021-08-13 2019

-

介绍STM32H7内置的系统bootloader的基础知识2021-08-11 1756

-

STM32H7演示:意法半导体2018-07-02 7504

全部0条评论

快来发表一下你的评论吧 !