系统芯片与晶片测试

描述

系统芯片 (Sxstem on Chip,SoC)通过软硬件结合的设计和验证方法,利用芯核复用及先进制造工艺,将多个原本独立的功能(如逻辑电路、存储器、混合信号和微处理器等)集成到单一芯片上,具有高集成度、高速度、体积小、成本低、功耗低等优点。系统级封装( System in Package, SiP)与SoC 不同的是,SiP 是采用不同芯片进行并排或叠加的封裝方式,而 SoC 则是将多个功能模块集成在单芯片上。

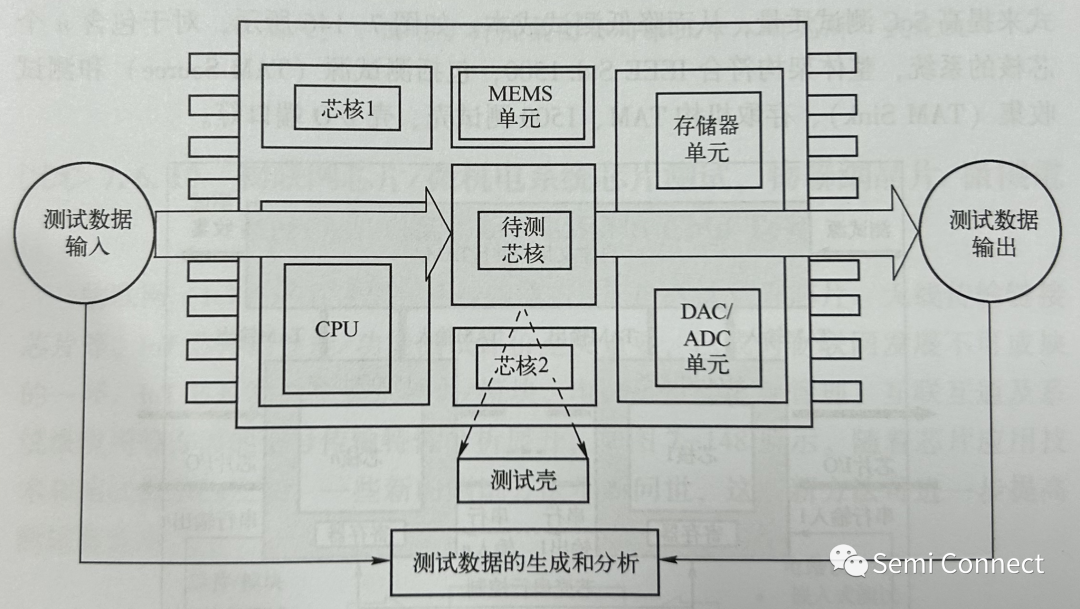

SoC 设计是一种基于嵌人式芯核的设计,其测试的关键是核复用带来的核测试复用问题。另外,SoC 集成了不同来源、不同类型、不同设计的芯核,测试时还需要解决测试数据输人和输出的有效传输、嵌人式芯核互异性等问题;此外在内核测试的基础上,还要完成芯核互连和系统级测试。图所示的是 SoC 内嵌芯核测试访问机制。由图可见,它是通过访问测试壳实现对芯核的测试存取的。

为了解决基于核的SoC 测试问题,必须建立 SoC 测试隔离、测试存取、测试控制和测试观察的规范和标准,如IEEE制定的 IEEE Std. 1149.1 (Test AccessPort and Boundary - Scan Architecture , IEEE Std. 1500 ( Testability Method forEmbedded Core - based Integrated Circuits) F IEEE Std. 1450 ( Test Interface Language ( STIL) for Digital Test Vector Data)等一系列的标准。

TEEE Std. 1149. 1 标准自1990年公布以来,边界扫描技术已被广泛接受和重视。扫描链将逻辑测试存取端子整合到电路内部,通过扫描操作提供可控制性和可观测性的人口,使电路的物理测试存取端子得以简化。在此基础上,JTAC还推出了 IBEE Std. 1149.4(用于数模混合电路)和IEEE Std. 1149.7(减少了测试引脚)等标准。

IEEE Std. 1450 标准旨在提供一个通用的测试向量图形描述语言,该语言在EDA 仿真工具和 ATE 上不需要转换即可使用. 建立了 EDA 和 ATE 之间的无缝链接。其中,IEEE Std. P1450.1 提出了标准测试接口语言(Standard TestInterface Language),该语言将替代传统 BDA 仿真的 VCD、WGL波形文件等。

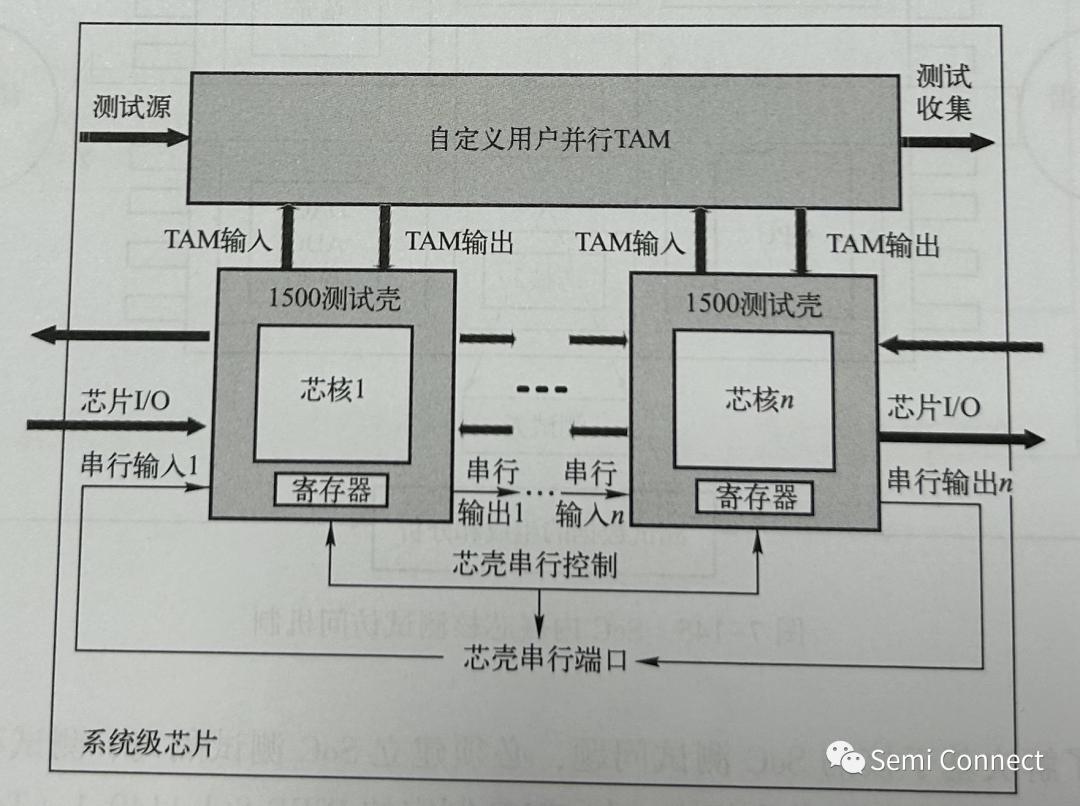

IEEE Std. 1500 提出了一种可扩展的标准架构,适用于实现嵌人式内核和相关电路的测试复用和集成。IEEE Std. 1500 提出的标准架构具有串行和并行测试访问机制(Test Access Mechanism),以及丰富的指令集,可用于 SoC 内核互连和系统测试。此外,IBBE Std. 1500 定义丁支持内核隔离和保护的特性,通过改进设计文件自动转化效率,促进可测性测试设计 (DFT)技术,以区通过改进访问方式来提高 SoC 测试质量,从而降低测试成本。如图所示,对于包含几个芯核的系统,整体架构符合 IEEE Std. 1500,包括测试源(TAM Source)和测试收集(TAM Sink)、存取机构TAM、1500 测试壳、壳V/0端口等。

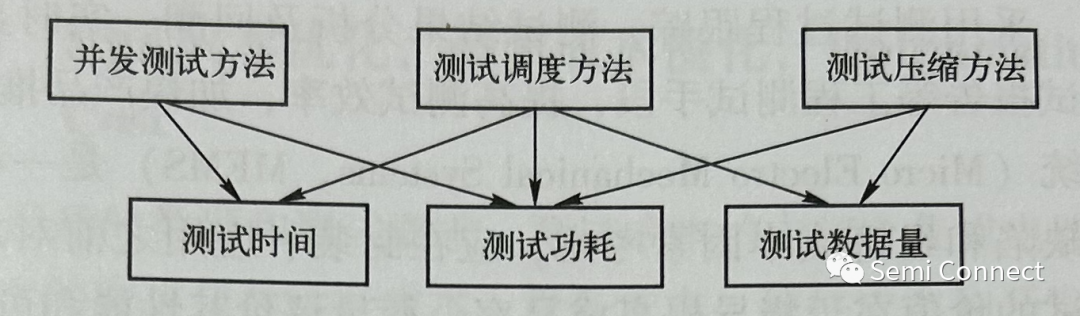

IEEE 标准可有效地解决 SoC 的测试实现。SoC测试的另一个问题是测试成本。降低SoC测试成本的有效方法是减少测试时间,这一点可采用并发测试测试调度和测试压缩等方法得以实现。并发测试通过同时对被测 SOC 中的多个功能模块进行测试,从而将测试时间减少到最长单路径时间。

测试调度通过合理分配嵌人式芯核的测试集和测试存取机制,从而达到多核测试、减少总线冗余时间和避免测试冲突的目的。SoC 集成度和复杂度的日益提高,以及高故障覆盖率的需求,导致测试数据日益剧增,测试压缩通过设计优化测试激励响应压缩方法和测试策略,达到减少测试存储通道数据量、降低测试功耗和缩短测试时间的效果。图所示的是测试优化方法和目标。

审核编辑:刘清

-

Smiths Interconnect正式推出高性能Volta系列探针头,用于晶片级芯片封装测试2017-12-08 7307

-

VirtualLab:用于微结构晶片检测的光学系统2025-05-28 421

-

[VirtualLab] 用于微结构晶片检测的光学系统2026-04-07 409

-

基于干涉的光学测试系统2026-04-08 80

-

223 暴力拆解芯片,看看里面的晶片长啥样暴力拆解芯片,看看里面的晶片长啥样车同轨,书同文,行同伦 2022-08-03

-

旋转拉力测试仪晶片推拉力测试机力标精密设备 2023-10-31

-

芯片推力测试机晶片推拉力测试机力标精密设备 2023-11-13

-

晶片推拉力测试机设备焊接强度推拉力测试仪#晶片推力测试 #焊接强度 #推拉力博森源推拉力机 2024-01-05

-

晶片验证测试及失效分析pdf2011-11-29 74690

-

晶片验证测试及失效分析2012-07-18 2354

-

晶片边缘蚀刻机及其蚀刻方法2018-03-16 3477

-

倒装芯片和晶片级封装技术及其应用2018-08-27 3272

-

半导体工艺—晶片清洗工艺评估2022-03-04 3481

-

LED封装晶片便携式推拉力测试机2023-05-31 1785

-

如何用集成电路芯片测试系统测试芯片老化?2023-11-10 2584

全部0条评论

快来发表一下你的评论吧 !