RISC-V未对齐导致问题案例

RISC-V未对齐导致问题案例

描述

前言

本文以一个实例,讲解RISC-V未对齐访问导致的问题.

未对齐导致的问题很常见,本文以实例分享调试分析过程。

过程

现象是程序进入了异常中断函数exception()

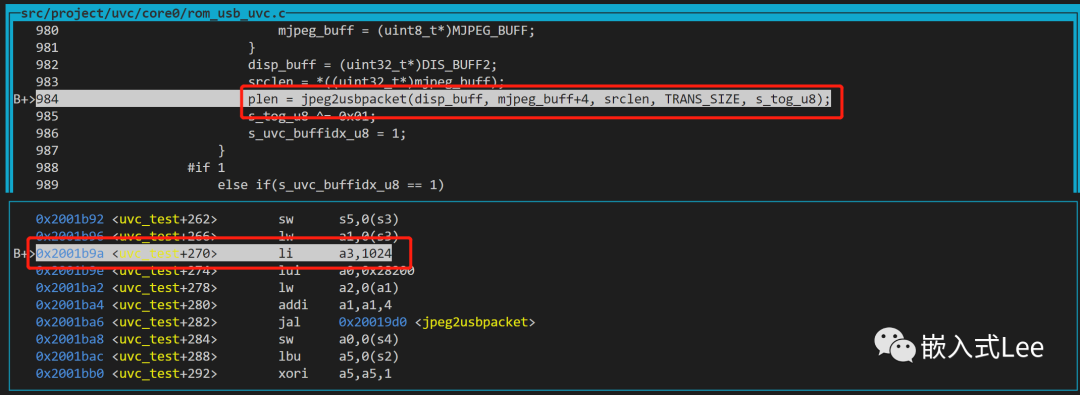

先分部打端点,结合step单步运行,确认执行哪个函数的哪一句执行后异常。

这里已经确认是rom_usb_uvc.c的984行执行后异常。

在执行异常的语句前打断点

b rom_usb_uvc.c:984

再重新运行到该处

显示汇编界面layout split

stepi按照汇编单步执行

最终确认执行汇编指令

lw a2,0(a1)后异常

查看此时寄存器a1的值。

(gdb) info reg a1

a1 0x28429ddd 675454429

stepi执行完`lw a2,0(a1)``后进入异常处理函数

查看此时mcause寄存器

(gdb) info reg mcause

mcause 0x4 4

见 对应 即 所以修改缓冲区按照WORD对齐。<的<>.Load address misaligned。正是lw指令寄存器a1间接寻址非WORD对齐地址0x28429ddd导致。

jpeg2usbpacket函数传入的指向缓冲区的指针参数非WORD对齐导致。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未来 !2024-09-10 1529

-

RISC-V Summit China 2024 青稞RISC-V+接口PHY,赋能RISC-V高效落地2024-08-30 3664

-

rIsc-v的缺的是什么?2024-07-29 1206

-

什么是RISC-V2024-02-02 1637

-

RISC-V设计支持工具,支持RISC-V技术的基础2023-07-14 827

-

RISC-V未对齐访问导致问题案例2023-05-06 913

-

RISC-V 发展2023-04-14 1067

-

openEuler加入RISC-V Landscape2023-03-13 2144

-

RISC-V学习笔记【1】RISC-V概述2022-11-24 3427

-

RISC-V的挑战分析2022-02-25 3917

-

什么是RISC-V? RISC-V指令具有哪些特点应用?2021-10-14 3122

-

第一届RISC-V中国峰会看点 risc-v开发要怎么优化risc-v指令集架构代码密度2021-06-23 10438

-

RISC-V规范的演进 RISC-V何时爆发?2021-02-11 4383

-

RISC-V在物联网的封闭性系统的应用2019-02-05 4030

全部0条评论

快来发表一下你的评论吧 !