如何减少PCB板内的串扰?

PCB设计

描述

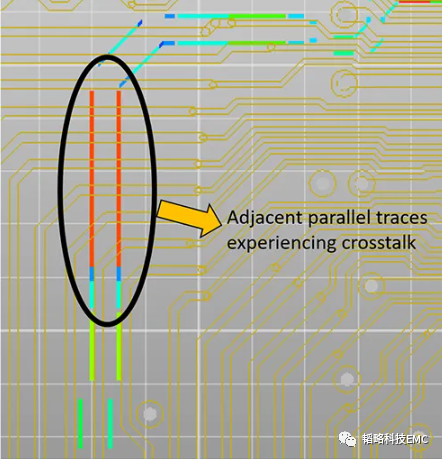

随着科技发展和人们消费需求,现今电子设备小型化的趋势越来越突出,印制电路板(PCB)越做越小。这导致PCB板内信号走线之间容易产生无意间耦合,这种耦合现象被称为串扰(如图1)。

图1.平行走线相互串扰

以下列举一些减少串扰的PCB布线规则。

规则 1:关键信号远离I/O信号

需要重点关注I/O连接口附近的关键布线,因为噪声很容易通过这些 I/O 口以辐射或者传导的形式离开或进入电路板。如I/O口直连的信号线与关键信号线靠太近,会产生耦合效应(见图 2)。

图2.关键信号与I/O口走线图示

噪声会通过I/O连接线进入,并通过PCB内部I/O连接线耦合到关键信号上(时钟或敏感信号),模型如图3a。同样的,关键信号(时钟或高速信号)会将噪声耦合到PCB内部的I/O信号走线,并通过I/O连接线往外辐射,模型如图3b示:

图3.关键信号与I/O信号靠太近会引起潜在的EMC问题

规则2:高速信号走线尽量短

在高速PCB(> 100MHz)上,高频信号波长较短,辐射效率高,以至高速信号本身走线形成天线效应,特别是当走线放在顶层或底层时。这种不必要的辐射可以耦合到相邻的走线甚至是附近接口连接线。

我们建议将高速信号走线画在PCB中间层,如图4b所示。这有助于控制来高速信号产生的电磁场,避免出现串扰或电磁干扰形式的非预期耦合。如果高速走线走在表层,则应使走线尽量短,当走线小于电小尺寸(1/10波长)时,天线效应会大大减少。如图4所示:

图4. a.信号走表层 b.信号走中间层

规则3:差分网络匹配

理论上,差分对传输的信号大小相等,极性相反,因此差分对产生的EMI会相互抵消或者忽略。但是,只有在差分对走线长度相等并且尽可能对称地靠近彼此时才有效。图5展示了几种不同情况的差分对走线。

图5.差分走线优劣对比图

为了对比差分信号走线好坏的辐射情况,作如下电路仿真,图6a和图6b分别是两组对称和非对称走线,走线左端输入高频差分信号,右端端接负载。

图6. a.对称走线 b.非对称走线

我们对以上两种情况做近场分析,噪声仿真如图7:

图7.a对称差分走线仿真图 b非对称差分走线仿真图

在1m距离情况下,对比测试辐射发射情况。30MHz-1GHz的频段下,对称走线比非对称走线噪声值小8-10db,如图8所示。

图8. 1m距离辐射对比数据

总的来说,在电子设备的设计中,电路前期设计的重要性不容忽视。良好的EMC设计可以确保设备的正常运行,避免电磁干扰对其他设备的影响,并提高产品自身的可靠性。

-

减少串扰的方法有哪些2024-01-17 3206

-

PCB布线减少高频信号串扰的措施都有哪些?2023-10-19 2484

-

什么是串扰?PCB走线串扰详解2023-09-11 2319

-

如何减少PCB设计中的串扰问题 PCB串扰的机制和原因2023-07-20 3901

-

什么是串扰?如何减少串扰?2023-05-22 5545

-

如何减少PCB板内的串扰2023-05-16 999

-

在设计fpga的pcb时可以减少串扰的方法有哪些呢?2023-04-11 1425

-

如何降低串扰对PCB板的影响2022-07-07 1280

-

如何解决PCB布局中的串扰问题2021-01-13 3377

-

如何减少PCB布局中的串扰2020-09-19 3274

-

如何解决PCB串扰问题2020-07-19 2808

-

如何减少电路板设计中的串扰2020-03-07 4371

-

高速PCB设计中如何消除串扰?2019-07-25 3949

全部0条评论

快来发表一下你的评论吧 !