MOS管驱动电路原理图

应用电子电路

描述

MOS----MOS管驱动电路

引言:MOS管开关电路在分立设计里面应用非常广泛,包括逻辑控制,电源切换,负载开关等,在一些电路巧妙设计上具有非常大的创新性。以下电路均以使用增强型MOS为示例。MOS驱动电路的基本要求包括:对栅极施加足够高于Vth的电压的能力,以及对输入电容进行足够充电的驱动能力,本节介绍MOS的驱动电路示例。

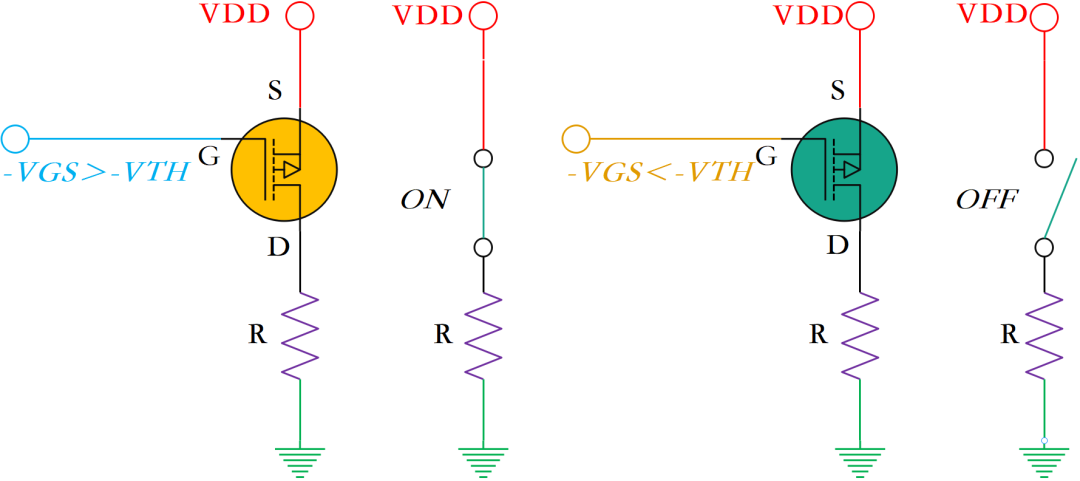

1. NMOS/PMOS的基本驱动电路

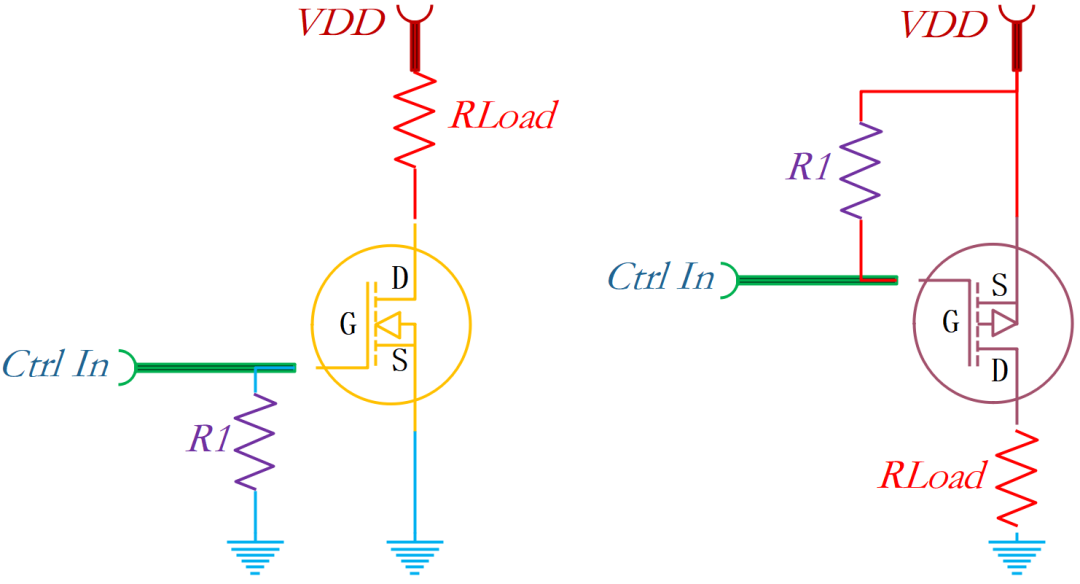

如图2-1所示,左边为NMOS基本驱动电路,右边为PMOS基本驱动电路,对于NMOS来说,Ctrl In为低电平时,NMOS不导通,Ctrl In为高电平(高于Vth)时,NMOS导通。对于PMOS来说,Ctrl In为低电平(VDD-Ctrl In

图2-1:NMOS/PMOS基本驱动电路

图2-1中的R1并非是必要的电阻,当没有R1时,实际不影响MOS的导通与关闭,但是通常都会加上R1,作为一个偏置。对于NMOS,下拉R1到GND,当Ctrl In脚从高电平到低电平时,栅极能够被更快拉低,并且牢牢固定在GND,更可靠的关闭。对于PMOS,上拉R1到VDD,当Ctrl In脚从低电平到高电平时,栅极能够被更快拉高,并且牢牢固定在VDD,更可靠的关闭。

栅极偏置电阻R1是在Ctrl In端低电平时将栅极固定在GND(NMOS),避免额外的干扰浮动,所以它的值取值比较自由,通常R1的选值在10K-100K,如果想提高输入阻抗,可以将R1取的比较大(1M),推荐阻值10K,47K,100K。另外静电效应容易从栅极击穿MOS,所以R1也有一定程度的静电吸收保护作用。实际上偏置电阻R1是非必须的,但为了电路的鲁棒性,要求都必须有。

2. NMOS/PMOS基本驱动电路升级

我们知道MOSFET的栅极到源极充当电容器(回顾:MOS-1:MOS的寄生模型)。电容器的工作原理是这样的:当电容器充电时,电流流过它,开始很多,后来越来越少,当电容器充满电时,没有电流流过它(参阅Capacitor-2:电容的充放电)。

当你的MOS处于开启稳态时,其栅源电容器已充满电,所以没有电流流过栅极。但是当你的MOSFET处于被打开的动态过程中时,会有一个电流给这个栅源电容充电。因此在一小段时间内,栅极Gate可能会有大量电流流动。

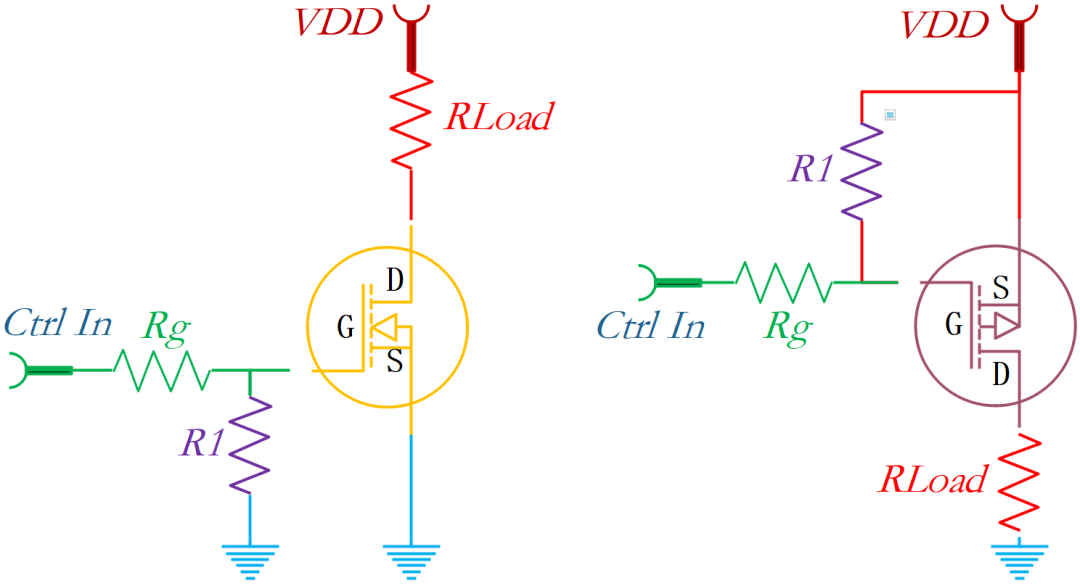

为了确保这个短暂的电流对于器件来说不会太高,如图2-2所示需要在输出引脚和MOSFET栅极之间串联一个电阻器Rg(栅极串联电阻):通常1000Ω或者100Ω是一个足够大的值。但这取决于你的电路。可以使用欧姆定律计算从电阻器获得的最大电流:I=V/R,当使用的电阻越高,MOSFET开启/关闭的速度就越慢,如果你想快速打开和关闭输出,Rg取值就要考虑减小(3.3Ω-10Ω)甚至取消。

图2-2:带Rg的MOS驱动电路

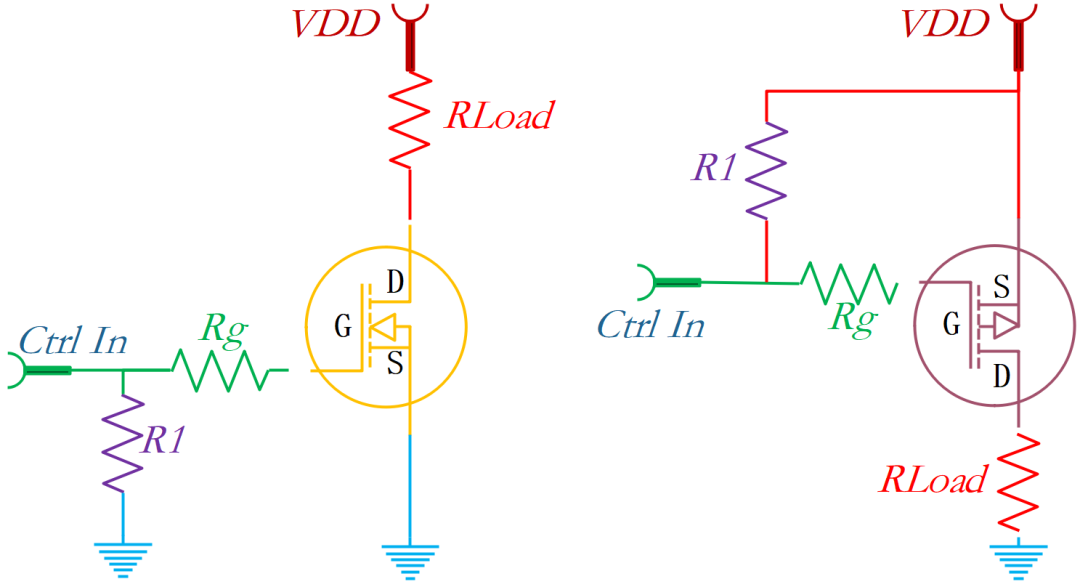

图2-3:不正确的Rg放置方式

如图2-3所示,如果栅极电阻器Rg放置在下拉电阻器的左侧,则会得到一个分压器电路,该电路将降低栅极电压,如果你选择了一个至少比下拉电阻小100倍的栅极电阻,那么电压的降低很小,可以忽略不计。但是如果它们的值更接近一点,则栅极上的电压将低于Ctrl in电压,影响MOS的开启,所以最佳位置Rg放置在R1的左边。

3.选驱动MOS管的考虑项

1:使用MOS时和JFET不同,漏极电流不受IDSS的限制,所以不需要过于在意漏极电流的设定值。

2:作为电路中使用的MOS,应该选择漏极-源极间电压VDSS(最大额定值)大于VDD,栅-源电压VGSS(最大额定值)大于VDD。

3:导通条件则是外部施加的VGS大于1.5倍VGSTH(称为过驱动)。电路的直通电流小于MOS的漏极电流ID的最大额定值。耗尽型器件在VGS=0V时也有漏极电流流过,是正常导通器件,所以不太适合在开关电路中使用。

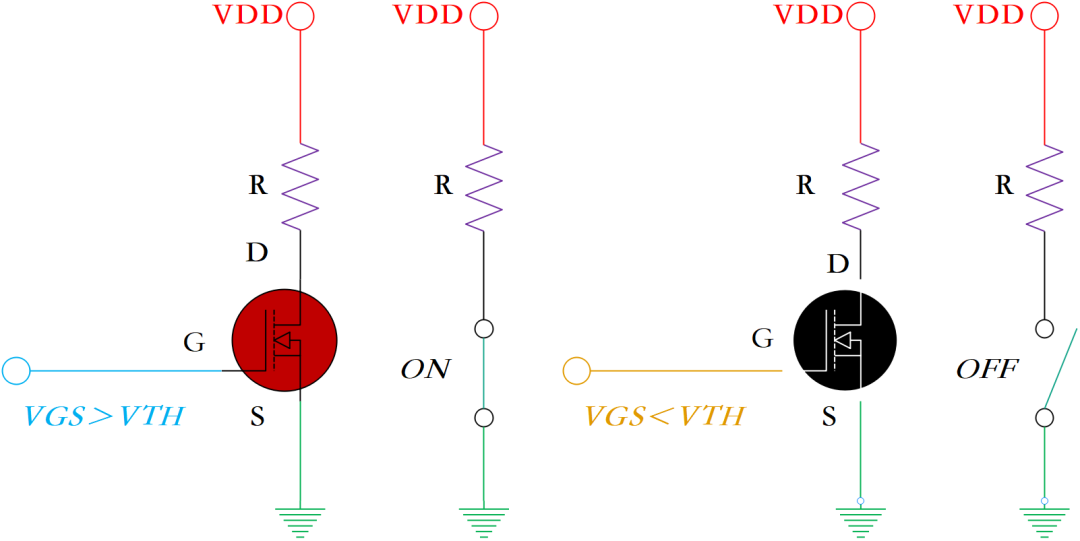

图2-4:NMOS驱动等效

如图2-4所示,建议负载R放在高侧,避免负载产生显著压降(开通时,S极电位接近VDD),影响GS的电平,导致NMOS开启关闭受影响,这在后面SCD系列里面会再次讲到。

图2-5:PMOS驱动等效

如图2-5所示,建议负载R放在低侧,避免开通时,S极电位接近于GND,那么G极就要施加负电压,导致PMOS开关出现问题,这在后面SCD系列里面会再次讲到。

-

MOS管驱动电路的基础总结2017-08-01 33270

-

开关电源MOS管驱动电路的设计2022-09-15 5840

-

单片机驱动mos管电路图2022-11-25 10494

-

mos管驱动内部图2020-08-10 2324

-

MOS管驱动变压器隔离电路分析和应用2012-10-26 15952

-

MOS motor driving module V3.0_原理图2016-08-29 1087

-

mos管开关电路_pwm驱动mos管开关电路图分享2018-01-04 63066

-

mos管开关电路图大全(八款mos管开关电路设计原理图详解)2018-03-06 375639

-

MIG250 MOS管整机电路原理图免费下载2019-04-22 2454

-

MOS管驱动电路_单片机如何驱动MOS管2020-06-26 84480

-

几种常用的MOS管栅极驱动电路2022-03-31 13826

-

常用MOS管驱动电路分享2022-07-10 6400

-

常用MOS管驱动电路说明2022-07-12 5826

-

MOS管常用的驱动电路分享2023-01-26 3510

-

mos管驱动电路原理图怎么设计2023-12-20 2855

全部0条评论

快来发表一下你的评论吧 !