边缘处理如何实现下一代毫米波扫描仪

描述

毫米波 (mmWave) 成像已成为机场、公共建筑和体育场馆安防扫描系统的重要组成部分。毫米波扫描仪优于传统金属探测器,因为它们可以识别和定位金属和非金属威胁。本文 介绍 了 毫米波 成像 硬件 的 工作 原理, 并 将 介绍 一种 芯片 组, 该 芯片 组 使用 边缘 处理 来 管理 大量 数据 负载, 从而 支持 漫游 安全 扫描 系统 的 开发。

毫米波成像的工作原理

图 1 说明 了 毫米波 扫描 器 的 工作 原理。该系统由连接到空间分散天线阵列的发射器和接收器阵列组成。该系统类似于测量回波损耗或S11的网络分析仪。在任何时候,阵列中的一个天线都在以单个频率发射低功率信号。该信号从目标反射并产生反向散射(插图显示了目标上单个点的反射,但实际上传输的信号是全向的,因此目标上的多个点会有反射)。

反向散射的相位和幅度由阵列中的所有接收天线测量。发射天线和接收天线之间可以使用极化,以减少直接发射到接收泄漏。测量完成后,从另一个发射天线(以相同频率工作)发射相同的信号,并重复测量过程。

由于RF信号的穿透深度和反射的性质随频率而变化,因此前面描述的扫描通常在多个频率下在宽带上重复。由此产生的矢量矩阵形成一个多维数组(相对于频率和空间位置),用于创建可以识别隐藏在衣服层之间和下方的金属和非金属物体的图像。

完成此类扫描所需的硬件必须是多通道的,并且具有较宽的工作频率范围。10 GHz 至 40 GHz 的频率范围足够宽,足以区分典型安全扫描场景中的对象(衣服、背包、武器和爆炸物)。较高的通道数系统往往具有更高的分辨率,使它们能够识别小物体。例如,虽然检测剃须刀片在机场扫描仪中至关重要,但保护公共建筑和体育场更侧重于检测较大的物品,如武器或爆炸物。在这些应用中,通常使用较少的通道数。

这些系统中的另一个关键组件是快速切换时间。这使得扫描系统得以实现,其中被扫描者只需在短时间内(通常为一秒或更短)摆姿势。下一代演练系统需要更快的切换时间,以便人不必停下来摆姿势。

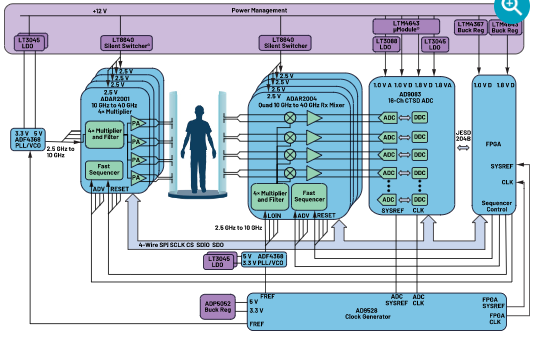

图2显示了如何使用ADI公司的毫米波成像芯片组实现完整的毫米波扫描仪。发射器阵列(ADAR2001)由中央捷变频率源驱动。接收器阵列(ADAR2004)检测反射信号,并将其下变频至低中频,在该频率下,多通道连续时间Σ-Δ(CTSD)转换器(AD9083)对其进行中频采样。

现在,我们将仔细研究这些组件以及它们的功能如何优化整体系统性能。

发射机

如前所述,发射器由大量空间分散天线组成,每个天线由功率放大器驱动。ADAR2001是一款4通道发射器,直接连接到天线,输出频率范围为10 GHz至40 GHz。由于在大型阵列中分配10 GHz至40 GHz信号存在困难,ADAR2001集成了4×乘法器。因此,发射器 IC 前面的所有管道和信号分配都在 2.5 GHz 至 10 GHz 频率范围内进行。

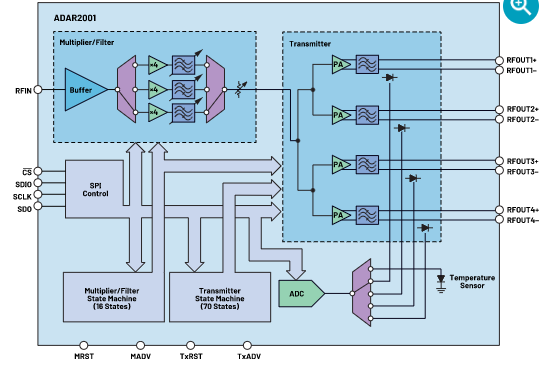

ADAR2001发射器的主要RF元件包括RF输入缓冲器、带集成可切换谐波滤波器的4×倍频器、1:4信号分配器和2001个差分输出功率放大器,用于驱动偶极子或螺旋天线等差分天线结构。ADAR3的详细框图如图<>所示。

RFIN 端口施加 2.5 GHz 至 10 GHz 之间的 CW RF 输入信号,功率电平至少为 –20 dBm。宽带倍频器由三个并联子电路组成。每个子电路(低频段、中频段、高频段)都经过优化,可乘以和滤波总频率范围的一部分。乘法器块输入端和输出端的开关用于选择所需工作频率的子电路。

乘法器输出通过可编程衰减器,然后分成四个并施加到四个功率放大器。除了乘法器模块中的可配置滤波外,每个PA还包含一个可以启用或禁用的低通/陷波滤波器。对于高达 20 GHz 的输出频率,应启用此滤波器。高于 20 GHz,应禁用它。

可编程衰减器用于帮助确保输出功率与频率的关系相对平坦。该衰减器具有大约15 dB的数字步进衰减范围。当输出频率从10 GHz扫描到40 GHz时,应减小此衰减,以保持所需的输出功率平坦度与频率的关系。这使得每个差分PA输出的标称PA输出功率为+5 dBm,谐波抑制范围为–20 dBc至–30 dBc。

要进行完整的 10 GHz 至 40 GHz 频率扫描,必须将乘法器/滤波器模块设置调整七次,以确保最佳的谐波抑制和输出功率。此外,当系统以一个频率驻留时,每个频率

图2.完整的毫米波成像系统。

图3.ADAR2001 10 GHz至40 GHz发射器。

发射机通道必须依次打开和关闭。为了避免造成SPI命令瓶颈,ADAR2001包括两个状态机,可以预编程多达70种状态。一旦器件的RAM被编程,就可以通过简单的脉冲到器件的MADV(前进)引脚来实现状态推进。这些特性相结合,可确保2 ns通道切换时间。在IC之间切换时也可以实现此切换时间(例如,器件A的通道4在器件B的通道1接通时关闭)。由于全扫描涉及多个频率的全通道扫描,因此切换时间至关重要。例如,如果阵列有 500 个晶片,并且要以 10 MHz 的步长从 40 GHz 扫描到 50 GHz,则它必须执行总共 300,000 个通道切换才能完成完全扫描。

每个通道上的RF输出功率可以使用单独的片上RF检波器进行监控。芯片温度也可以通过片上温度传感器监控。这些传感器馈入 5:1 模拟多路复用器,该多路复用器将所需信号传递到片内 8 位 ADC。

ADF4368 PLL/VCO为发射器网络提供激励。其输出信号将根据发射通道的数量多次分离。ADF4368的输出功率相对较高(+9 dBm)和ADAR2001的最小输入阈值(–20 dBm)确保ADF4368的输出在需要放大器缓冲之前可以多次无源分离。

接收器

来自传输的反射被接收器拾取,接收器是多通道混频器和ADC阵列。ADAR2004是一款四通道混频器和ADC驱动器,内置数字编程增益放大器(DGA)。LO输入也具有一个内部4×乘法器,由第二个PLL驱动,其输出频率与射频偏移,因此混频器产生真正的IF输出。然后,混频器的IF输出由AD9083采样,AD16是一款集成数字下变频的<>通道连续时间Σ-Δ型ADC。选择中频采样架构而不是零中频架构,以避免接收器中LO泄漏引起的直流偏移,以及LO正交分路器中不完美的正交平衡引起的I/Q误差。虽然这些缺陷可以通过校准来缓解,但每个输入频率都需要校准,因为LO泄漏和正交误差往往随频率变化。

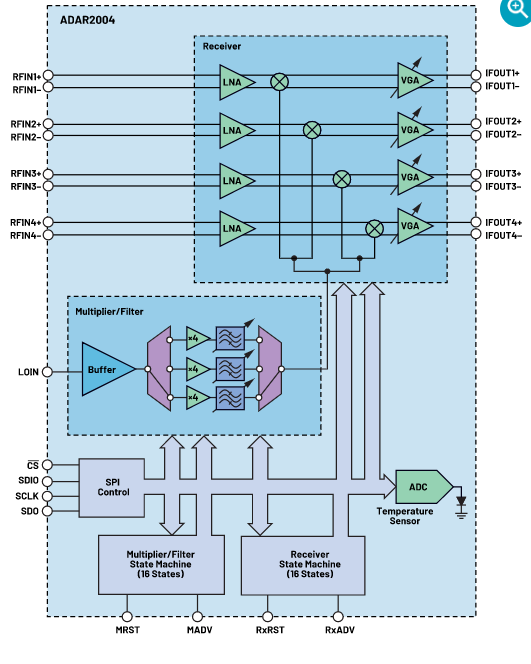

图4所示为四通道混频器ADAR2004的框图。LO输入由2.5 GHz至10 GHz正弦波驱动,在乘法器输出端产生10 GHz至40 GHz的正弦波。乘法器输出馈送到四个混频器,这些混频器的IF输出具有可编程增益。与ADAR2001发射器一样,ADAR2004接收器也具有两个可预编程的片内状态机。

多通道模数转换器

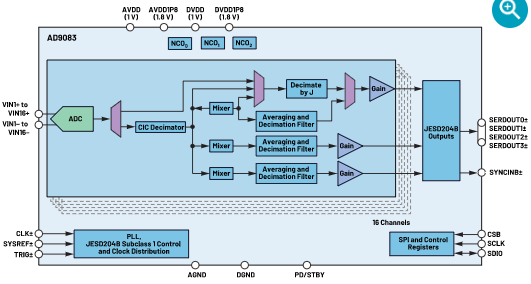

图5所示为9083通道CTSD ADC AD16的框图。ADC输入设计为具有与ADAR2004的IF输出相同的共模电压。这允许混频器输出和ADC输入直接连接。由于没有交流耦合电容,可确保当混频器输出突然切换时(例如,在混频器输入端的频率阶跃期间),不会出现充电/放电瞬变。

使用集成单极点滤波器的一阶CTSD ADC架构,最大限度地减少外部滤波,从而节省PCB空间。与奈奎斯特速率转换器的建立时间相比,该架构还具有较快的信号建立时间,奈奎斯特速率转换器需要高选择性抗混叠滤波器来消除噪声折叠。快速建立时间是本应用的关键要求,因为ADC建立时间必须能够跟上发射侧的快速通道开关。

图4.ADAR2004 10 GHz至40 GHz接收器框图。

每个ADC都有一个信号处理模块,用于滤除来自Σ-Δ ADC的带外整形噪声并降低采样速率。每个模块包含一个级联积分梳(CIC)滤波器、一个具有多个有限输入响应(FIR)抽取滤波器(由J块抽取)的正交数字下变频器(DDC),或多达三个带平均抽取滤波器的正交DDC通道,用于数据门控应用。三个正交DDC通道的存在可以同时解调多达三个频率。稍后我们将看到如何使用它来显着加快扫描时间。

系统设置和操作

ADAR2001和ADAR2004专为在大型阵列中高效工作而设计。特别强调减少布线开销。ADAR2001和ADAR2004的RFIN和LO输入端口可在低至–20 dBm的输入电平下工作。由于需要从公共LO源(本例中为ADF4368)驱动这些输入,因此这种低输入灵敏度允许在需要放大之前进行大量无源扇出。例如,假设威尔金森功率分配器的净损耗为1 dB,则ADF4368的9 dBm输出功率可以无源扇出128次,可以驱动512个器件(<>个通道)。

驱动ADAR2001和ADAR2004片内时序控制器的进阶和复位引脚也设计为并行驱动,以最大限度地减少处理器或FPGA必须提供的GPIO数量。通过在时序控制器中提供足够的深度和复杂性,可以使用一组前进和复位脉冲驱动多达16个ADAR2001器件。

在工作之前,必须对ADAR2001和ADAR2004的时序控制器进行编程。虽然可以使用SPI命令访问两个设备的所有功能,但相关的延迟将导致不可接受的总扫描时间。

让我们考虑如何为基于通道的扫描设置一个 64 通道系统(64 发射器、64 接收器),也就是说,我们在增加频率并重复扫描之前以单个频率循环遍历所有传输通道。

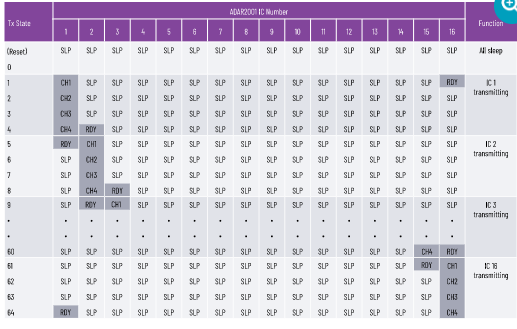

图6显示了如何对16个ADAR2001器件中的状态机进行编程以启用此扫描。该架构的一个关键目标是能够对从公共控制线执行不同操作的多个设备进行排序。

请注意,在图6中,虽然每个IC有65种状态,但大多数IC大部分时间都设置为休眠模式(SLP)。例如,IC 1仅在前四种状态下完全处于活动状态,因为该IC的通道1、2、3和4按顺序传输。在这四种状态下,所有其他IC都处于SLP或就绪(RDY)模式。

图5.AD9083原理框图

同样,IC 2仅在状态5至8期间完全激活,因为所有其他IC都处于SLP或RDY模式。通过以这种方式配置16个状态机,它们的导通周期彼此偏移,可以用并行脉冲驱动所有16个器件的前进和复位线路。

RDY模式是开发用于优化开关时间同时节省功耗的中间状态。由于大多数发射器大部分时间处于非活动状态,因此SLP模式是降低功耗的关键。但是,从系统角度来看,从SLP模式切换到传输模式(50 ns)所需的时间过长,会导致扫描期间出现延迟。RDY模式是一种中间状态,可以在IC准备传输时调用。请注意,在图7中,在状态4中,IC 4的通道1正在传输,而IC 2通过将IC 4置于RDY模式来准备传输。在从发射器状态 5 过渡到 1 的过程中,IC 2 从发射模式转换到 RDY 模式,IC 10 从 RDY 模式转换到发射模式。此转换需要 1 ns。随后的片内通道开关(即,从IC2上的通道3到通道4到通道2到通道2)的切换时间为1024 ns。对于以 10.40 GHz 步长从 0 GHz 扫描到 1 GHz 的 20 元素阵列,完整的扫描时间将小于 50 毫秒。这假设PLL锁定时间为5 μs。如果使用两个以乒乓模式运行的PLL来实现更快的频率建立,则扫描时间将远低于<> ms。

图6.对16个ADAR2001发送器进行编程,用于由单个提前脉冲驱动的通道扫描。

ADAR2004接收器的操作和时序不太复杂,因为通常的做法是将所有接收器通道配置为始终接收。状态机仍必须排序,以便在接收器与发射器一起扫描时选择正确的乘法器路径和滤波器设置。

如前所述,每个AD9083 ADC通道最多可以访问三个正交DDC通道。这意味着它可以同时解调三个频率,假设所有三个频率都在ADC模拟输入带宽(125 MHz)的输入频率范围内。例如,通过将三个IF音调定位在50 MHz、75 MHz和100 MHz,可以将这三个音调同时解调为I和Q基带数据。

为了在发射端促进这种方法,必须使用三个发射PLL,而不是一个。三个发射频率必须始终指向不同的物理发射IC(ADAR2001中的乘法器不能传导多音信号)。这三个频率必须始终不同,但在扫描时必须保持彼此接近的频率。例如,如果其中一个ADAR2001器件上的一个通道以10 GHz的频率传输,则另外两个器件将以10.025 GHz和10.050 GHz的频率发射,以支持50 MHz、75 MHz和100 MHz的IF输出。此方案在传输路径中需要更多的硬件和交换基础设施,但具有将整体扫描时间减少 3 倍的好处。

结论

该芯片组由四通道发送器ADAR2001、四通道接收器ADAR2004、9083通道ADCAD16和PLL/VCOADF4368组成,具有实现下一代漫游毫米波安全扫描器所需的高集成度和功能。集成状态机和片上数字下变频可显著卸载传统的集中式处理,并将其转移到智能边缘。最终结果是,中央处理器在扫描期间不必担心控制系统,并且它接收的数据已经被解调和抽取。虽然该芯片组专为毫米波安全成像应用而开发,但ADAR2001发射器和ADAR2004接收器的宽频率范围以及AD9083 16通道ADC的集成度,使该芯片组适用于需要高通道密度和快速开关的其他应用。

审核编辑:郭婷

-

毫米波人体扫描仪市场:过去、现在和未来2023-11-22 722

-

毫米波人体扫描仪市场: 过去、现在和未来2023-06-14 2121

-

毫米波人体扫描仪市场:过去、现在和未来2022-12-13 1882

-

毫米波传感器实现边缘智能的方法2022-11-10 932

-

毫米波技术如何为自主机器人提供边缘智能2022-11-09 1060

-

毫米波传感器实现边缘智能2022-11-01 695

-

毫米波技术基础2022-07-29 2724

-

毫米波传感器是如何实现边缘智能的?2021-06-17 3217

-

毫米波传感器如何实现边缘智能2020-08-07 2609

-

毫米波雷达(一)2019-12-16 14899

-

单片光学实现下一代设计2019-09-20 3599

-

毫米波人体扫描仪市场 过去和现在以及未来2019-05-13 6205

-

恩智浦与吉利汽车开展合作,定义下一代毫米波雷达2018-09-05 7973

-

实现下一代高密度电源转换2016-01-06 713

全部0条评论

快来发表一下你的评论吧 !