浅析ADC的参数含义

电子说

描述

- 位宽

即前一节提到的量化位数,常见的有8bit,10bit,12bit,16bit,24bit。比较少见的部分高速ADC有6bit~8bit。

- 分辨率

ADC所能分辨的最小量化信号的能力,最小分辨能力Δ=输入满量程电压/2^N。分辨率主要由ADC的位数(输出数字量的位数)决定,也与输入满量程有一定的关系。如一个输出满量程为0~5V的ADC、8位的ADC,其最小变化量为5V/2^8,约为19.5mV。若将ADC的位宽增加为10位,则ADC的最小变化量为5V/2^10,约为4.88mV。

- 量化误差Σ

在量化过程中由于所采样的电压不一定能被Δ(最小量化单位)整除,所以量化前后存在一定误差,此误差称为量化误差。量化误差属于原理误差,无法消除,理论上转换器的位数越高,各离散电平之间的差值越小,量化误差就越小。

- INL

INL (IntergerNonLinear, 积分非线性),指ADC实际转换曲线与理想曲线在纵轴方向的差值,单位LSB,用于表示实际转换曲线与理想的偏差程度。

- DNL

DNL (DifferentialNonLinear, 微分非线性),指ADC的实际量化台阶与对应于1LSB的理想值之间的差异。理想ADC偏差为0LSB。若DNL<1LSB,意味着传输函数具有单调性,没有丢码。

- SNR

SNR (Signal NoiseRatio,信噪比), ADC输出信号功耗和噪声功耗的比值,用dB表示。SNR=10*log(P_signal/P_noise),其中信号频谱图中基波分量有效值,噪声=总能量-信号能量和谐波能量。理想ADC的噪声主要来自量化噪声。

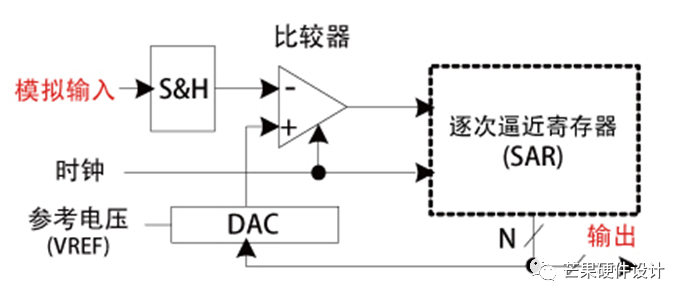

1.3 SAR型ADC原理

SAR(Successive Approximation, 逐次比较型), 包括一个比较器,一个数模转换器、一个逐次逼近寄存器(SAR)和控制逻辑单元。将输入的模拟信号与已知电压(DAC,数模转换)不断进行比较,一个时钟周期完成一次转换,N位的ADC需要N个时钟周期完成转换,转换完成后输出二进制。

从上面描述可以看出,此种ADC有个问题,位宽越宽,转换需要的时钟周期越多,即如果想提高ADC分辨率,会限制采样速率。所有此种ADC一般用在低速场景。

1.4 Σ-Δ型ADC原理

Σ-Δ型(Sigma-Delta-Converter, Σ-Δ型模数转换器), 又称为过采样转换器,它采用增量编码方式,根据前一量值与后一量值的差值的大小进行量化和编码。Σ-Δ型ADC主要由Σ-Δ型调制器和数字滤波器组成。调制器主要完成信号抽样和增量编码,给数字滤波器提供增量编码。数字滤波器完成对Σ-Δ码的抽取滤波,把增量码转换成高分辨率的线性脉冲码调制的数字信号,因此抽取滤波器实际上相当于一个码型变化器。

-

请问ADC12MCTLx的最高位EOS代表的含义是什么?2025-02-14 498

-

功率分析仪参数及含义2025-01-28 2735

-

ADC10321引脚VD和VDIO之间有一个扼流圈,有什么特殊的含义和使用方法吗?2025-01-06 374

-

vlookup函数的四个参数含义2023-12-01 9924

-

微波网络中S参数是什么, 有什么含义2022-12-08 5503

-

MOS管各项参数分别是什么含义2022-09-01 7490

-

浅析巴伦的功能原理、性能参数、基本类型2022-01-21 1105

-

orcad的DRC检测参数设置的含义是什么2021-10-28 8466

-

请问电机参数的含义及测量方法是什么?2021-10-19 4902

-

步进电机的参数有哪些含义?2021-07-08 1609

-

ADC的最低有效位LSB参数的含义是什么?2021-04-08 3464

-

常用基础元器件的参数测量方法及标注含义2018-04-02 1509

-

S参数的物理含义2009-08-18 7974

-

移动WiMax参数指标及射频测试浅析2008-10-13 999

全部0条评论

快来发表一下你的评论吧 !