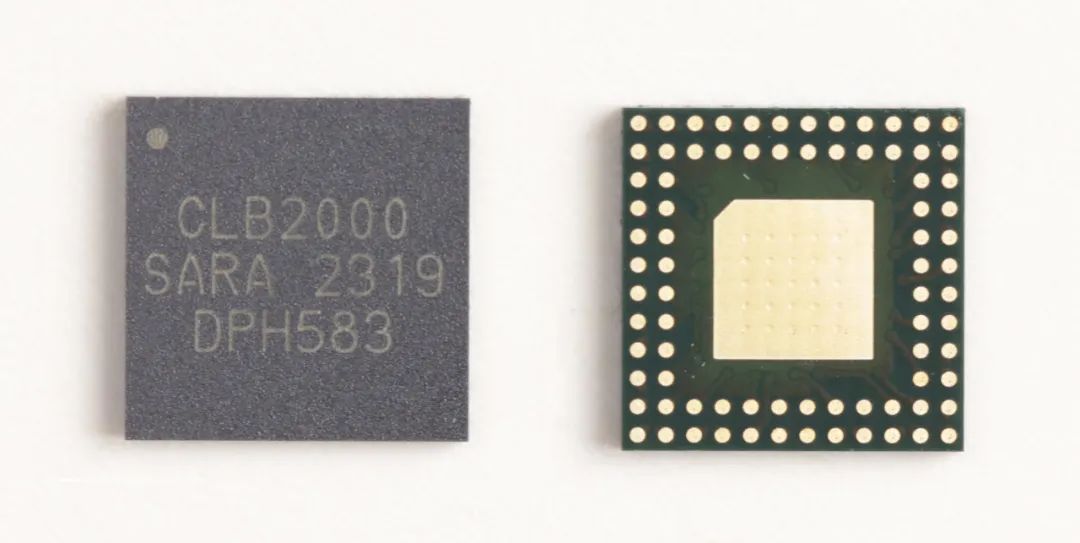

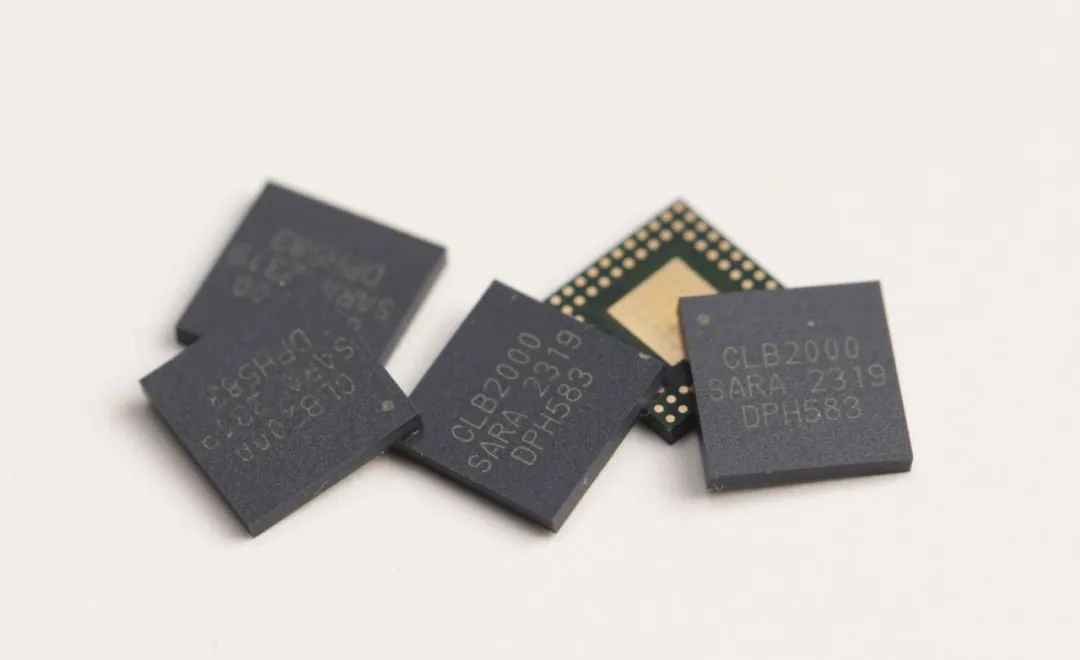

核芯互联推出全新20路LP-HCSL差分时钟缓冲器CLB2000

接口/总线/驱动

1163人已加入

描述

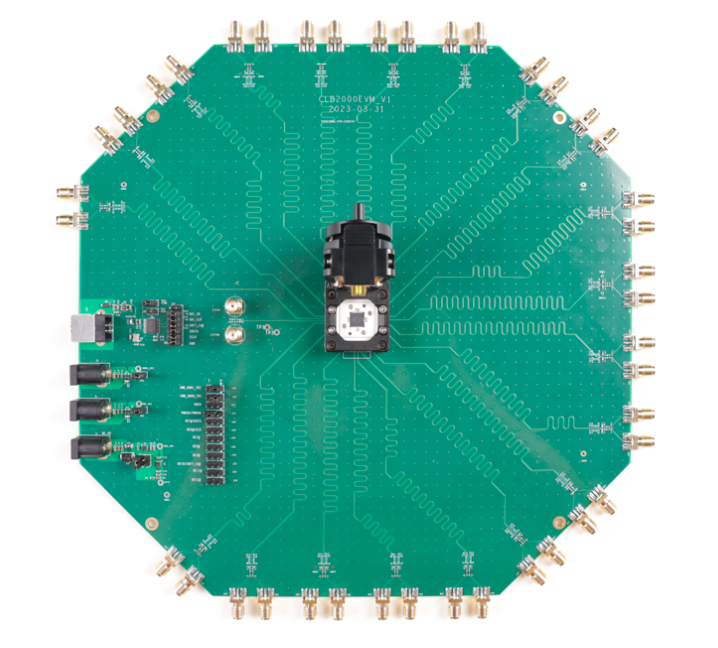

高性能的时钟器件是高带宽、高速率、高算力、大模型的基础。核芯互联近日推出面向下一代数据中心应用的超低抖动全新20路LP-HCSL差分时钟缓冲器CLB2000,其业界领先的附加抖动性能远超PCIe Gen 5和PCIe Gen 6的标准。

1简介

高性能的时钟器件是高带宽、高速率、高算力、大模型的基础。核芯互联近日推出面向下一代数据中心应用的超低抖动全新20路LP-HCSL差分时钟缓冲器CLB2000,其业界领先的附加抖动性能远超PCIe Gen 5和PCIe Gen 6的标准。

新推出的CLB2000符合最新的DB2000Q设计规范,可适用于下一代服务器、数据中心、存储设备及其他PCIe应用,且同时满足PCIe Gen1/2/3/4/5/6的规格。

2典型性能

输出时钟偏斜:<50ps;

输出延迟:<3ns;

附加抖动DB2000QL:< 8fs;

附加抖动PCIe Gen 4:< 10fs;

附加抖动PCIe Gen 5:< 5fs;

附加抖动PCIe Gen 6:< 3fs;

符合英特尔DB2000QL规范;

3.3V电源供电;

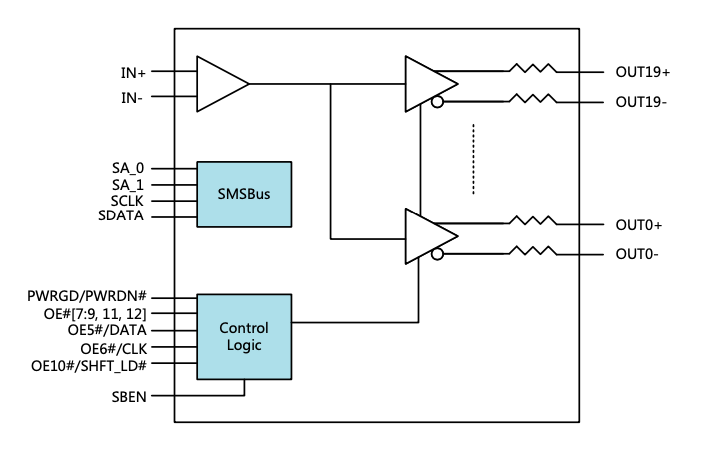

20路LP-HCSL输出;

支持I2C/SMSBus控制接口;

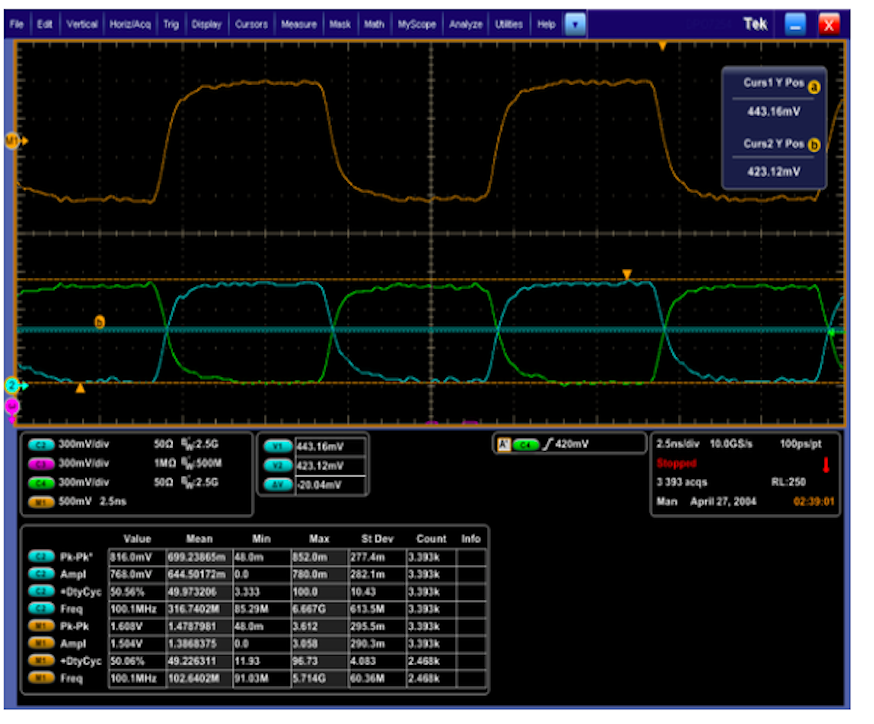

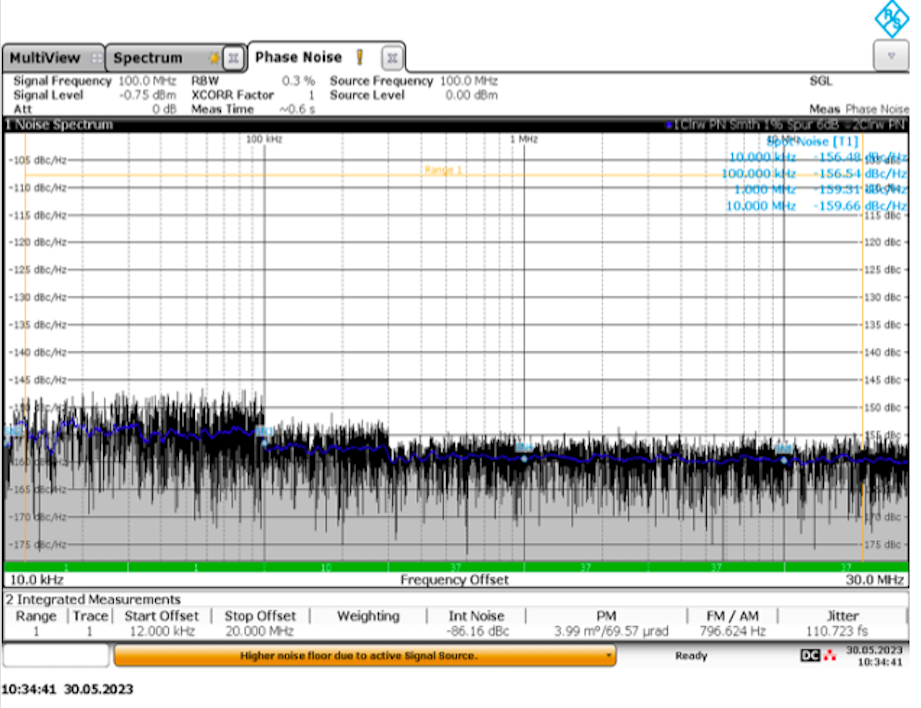

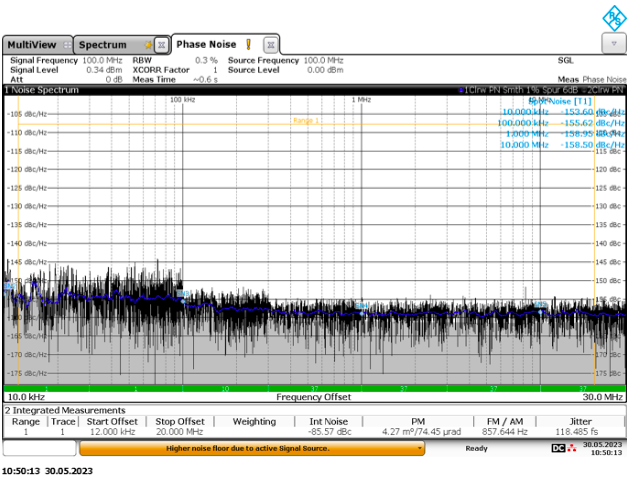

100M输出波形

100M输入Jitter

100M输出Jitter

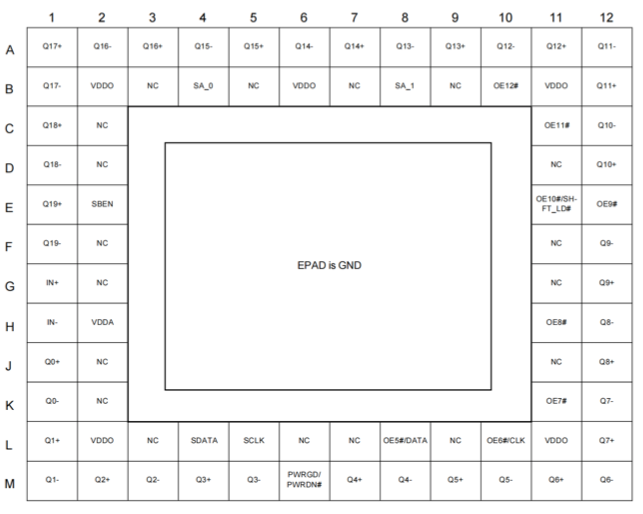

3管脚定义

4送样

CLB2000已经开放送样,请广大客户联系对口销售。

编辑:黄飞

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

核芯互联正式发布国产高性能时钟缓冲器芯片CLB70432026-02-25 1360

-

CDCDB2000:PCIe时钟缓冲器的卓越之选2026-02-08 299

-

CDCDB2000 20输出时钟缓冲器技术文档总结2025-09-12 915

-

LMKDB1104 用于 PCIe Gen 1 至 Gen 7 的 4 输出 LP-HCSL 时钟缓冲器技术手册2025-09-10 907

-

HAC00304QN型低抖动差分时钟缓冲器发布2025-07-13 832

-

HAC954QN型高速时钟缓冲器产品说明书2025-02-13 502

-

LMKDB1120和LMKDB1108超低抖动PCIe第1代到第6代LP-HCSL时钟缓冲器数据表2024-08-20 488

-

矽力杰高性能20路PCIe时钟缓冲器2023-12-20 2260

-

核芯互联推出符合DB2000QL及PCIe Gen5和Gen 6标准的低抖动时钟缓冲器CLB20002023-06-08 3006

-

芯科实验室推出业界首款通用时钟缓冲器Si533xx2012-11-06 6455

全部0条评论

快来发表一下你的评论吧 !