频率合成器是影响系统指标的原因吗?

电子说

描述

我们常说频率合成器常被比作电子系统的“心脏”,那频率合成器是如果影响系统指标的呢?

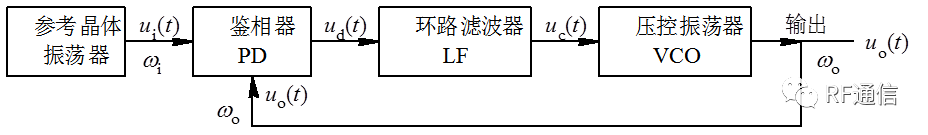

1.工作原理PLL

由鉴相器(PD),环路滤波器(LPF),压控振荡器(VCO)三个基本模块组成的一种相位负反馈闭环系统。

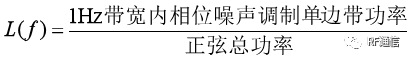

1.相位噪声

相位噪声:正弦波瞬时相位Φ(t)=ωt+φ(t)=线性相位ωt+随机相位φ(t),随机相位φ(t)的功率谱就是相位噪声谱,归一化后用功率谱密度表示。

相位噪声采用相对值表示:

相位噪声相当于一个噪声源对正弦波进行相位调制,若相位噪声较小,则调相指数(最大相偏)很小,φ(t)的功率谱与正弦波的功率谱相差不太大,所以用频谱分析仪测正弦频谱时,只能大致能观察相位噪声(但不准确,而且频谱分析仪的动态范围偏小)。

相位噪声中,窄带分量就是杂散。

通常我们说相位噪声很重要,那相位噪声如何影响指标,相位噪声又是怎么提出技术要求的呢?

我们经常看到的指标要求

邻信道功率比:≤-60dBc@±12.5kHz

邻信选择性:≤-60dBc@±12.5kHz

阻塞:≤-90dBc@±1MHz

互调要求:≤-60dBc@±50kHz@±100kHz

这些指标前文中讲过有一些与系统的线性有关,也与系统的相位噪声相关,那么是怎么与相位噪声有关的呢?

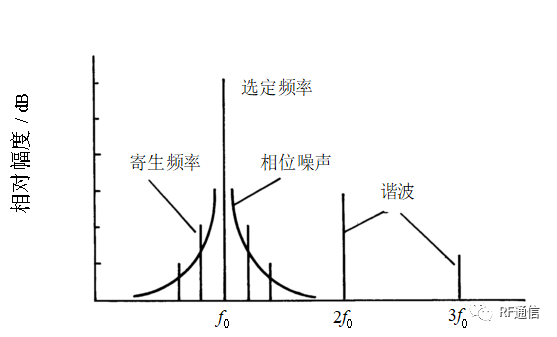

这里我们先提一个概念,倒易混频

正常mixing是拿LO当本振,去变RF的频率。倒易mixing是倒过来拿RF当本振,去变LO的频率。这两种mixing同时存在,只是强弱不同,与RF输入功率和LO远端相位噪声紧密相关。

倒易混频相当于天线端噪底从-174dBm/Hz抬高到L(Δf)+Pi。邻道选择性、阻塞即为倒易混频的一种,相当于抬高底噪。

以邻道选择性为例,根据倒易混频的要求即可算出对相位噪声的要求。

对相位噪声的要求如下:

第1邻道-60dBc@12.5kHz要求本振相位噪声必须低于-60-10log(12.5103)-10=-117dBc/Hz@12.5kHz。

指标换算即为邻道功率比对相位噪声的最低要求,12.5k的相位噪声为环路外噪声,根据频率源的计算公式可知,邻道指标对相位噪声的要求主要由VCO的相位噪声决定。在VCO的设计时就需要注意相位噪声的要求。同样的对于发射指标-发射邻道抑制可以同样换算出相位噪声的要求。

1.锁定时间

跳频发射机在频率跳变期间留出一定的时间,给频率合成器修改频率。

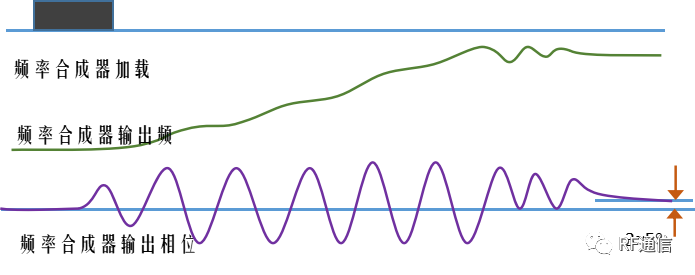

换频时间是指从频率合成器加载开始,到频率合成器的输出频率锁定,且相位抖动小于一定值(5°)的时间差。

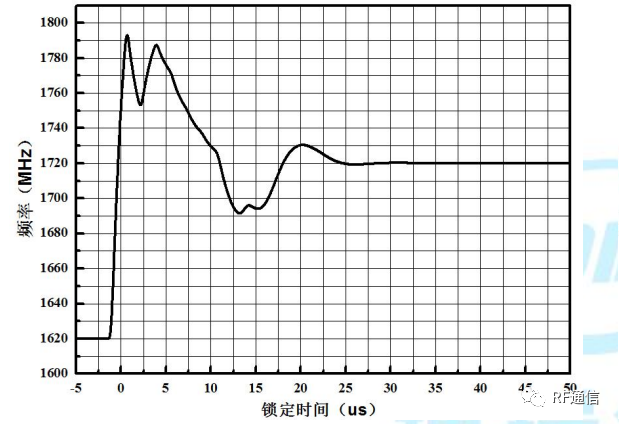

锁相环手册中一般会给出频率切换的时间,如下图所示锁定时间为25us,但是从频率加载的到锁定的时间是多少呢?这个要如何计算?

我们都知道,锁相环的加载是每一个clk送一个数,如果上图锁相环一共有6个寄存器,每个寄存器有32位,clk是5Mbps,那么从加载到锁定的时间是:0.2326+25=63.4us,在选择锁相环的时候就可以推算出锁定时间。

1.杂散来源

PLL电荷泵存在泄漏:参考频率、鉴相频率、数字时钟干扰等,这些都会以杂散的形式表现。

电源存在纹波,DC-DC共模干扰,放大器产生幅度杂散,VCO产生相位杂散。

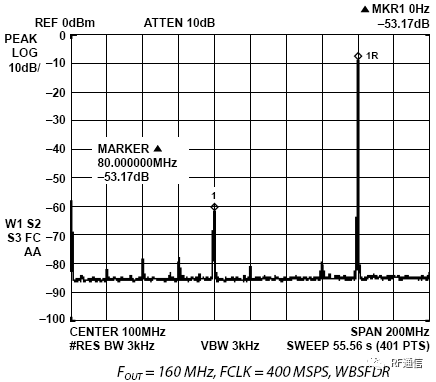

若fout的n次(主要是2、3次)谐波频率大于fclk/2,就会折叠回0~ fclk/2, 任何fout必有一个影子fclk- fout 。这个称之为整数边界杂散

杂散解决办法

启用Δ-∑调制(dither),将杂散能量转换为相位噪声能量,被调制到频率高端,通过低通环路抑制,杂散降低,但相噪变差;

电源:DC-DC开关频率的选择,低噪声LDO的选择;

电源滤波器:抗共模干扰,抑制浪涌;

单元电源:限流,抑制浪涌,限制地电流浪涌;

布局:遵循PCB上噪声分布;

内部干扰:远离DC-DC、数字器件;

-

系统的频域性能指标有哪些 频率合成器是如果影响系统指标的呢?2023-07-14 3644

-

pll频率合成器工作原理与pll频率合成器的原理图解释2023-02-24 11791

-

频率合成器的工作原理、主要指标及作用2022-04-28 11472

-

锁相环频率合成器是什么原理?2021-04-22 2649

-

PXI 3010艾法斯频率合成器2020-03-17 1064

-

什么是频率合成器2019-08-19 5767

-

如何利用FPGA设计PLL频率合成器?2019-07-30 4559

-

基于DDS的频率合成器设计介绍2019-07-08 3033

-

使用pll和voc设计频率合成器的特点2017-12-07 10771

-

合成器2017-12-06 3602

-

频率合成器,频率合成器原理及作用是什么?2010-03-23 15337

全部0条评论

快来发表一下你的评论吧 !