多核CPU的SoC缓存一致性设计概述

描述

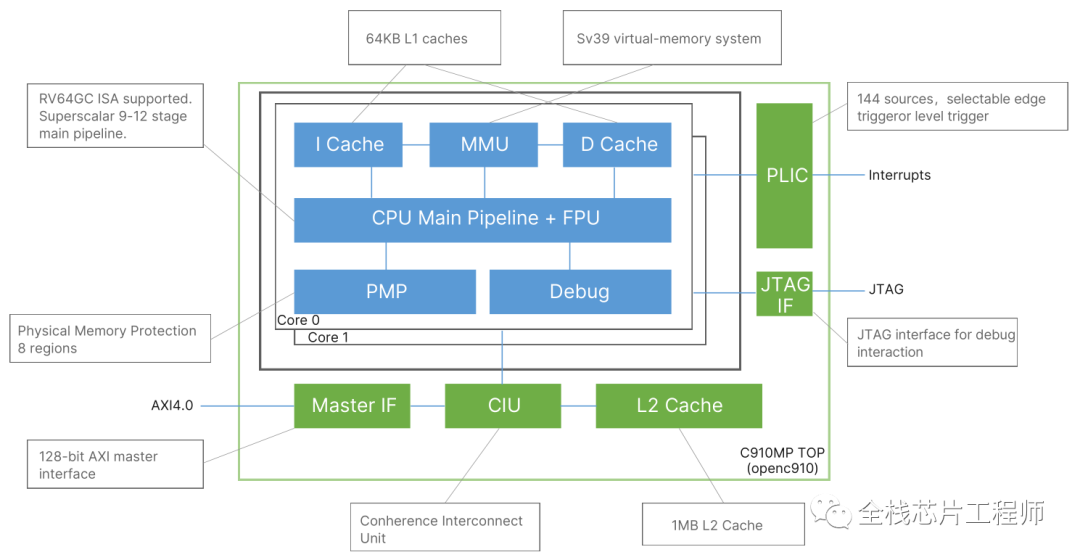

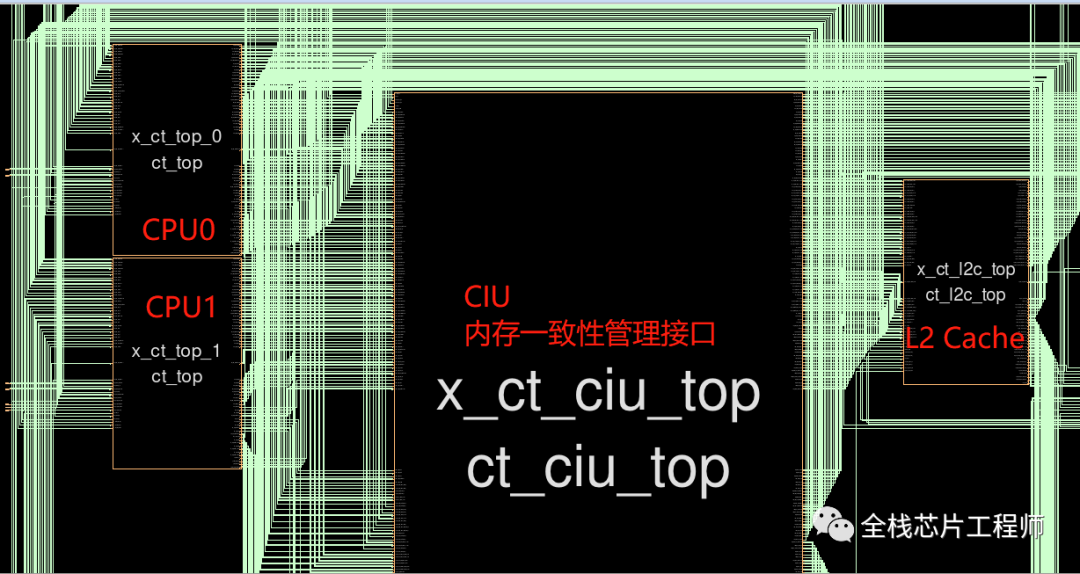

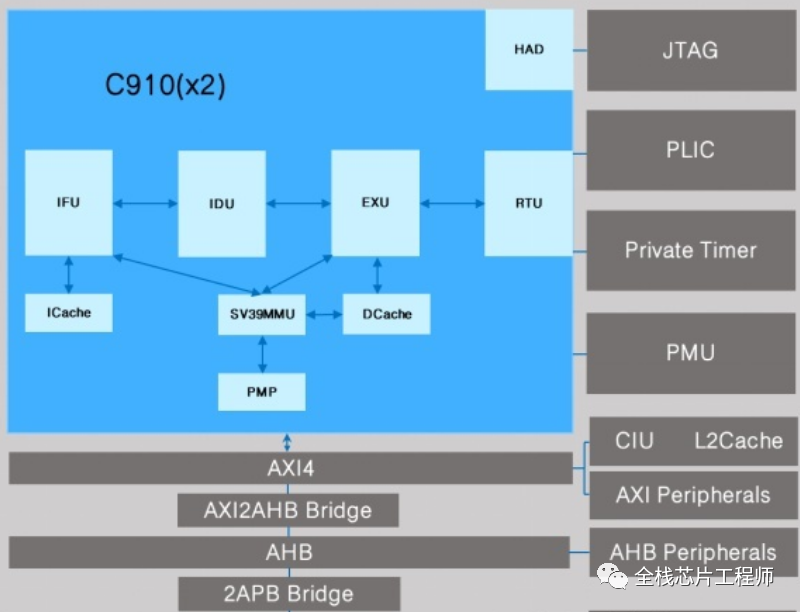

玄铁C910处理器是同构多核架构,支持双核;(开源版本为双核,预留四核接口),主要特征有:

• 支持各个核心独立下电以及cluster下电;

• 支持1 个AXI4.0 Master 接口,128比特的总线宽度;

• 两级cache结构,哈佛结构L1cache(Icache、Dcache)和共享的L2cache;

• L1cache支持MESI 的一致性协议,L2cache支持MOESI 的一致性协议;

• 支持RISC-V私有中断控制器CLINT 和平台级中断控制器PLIC;

• 支持自定义且接口兼容RISC-V 的多核调试框架;

C910MP 二级高速缓存采用 MOESI 协议维护多个处理器核心数据高速缓存的一致性。MOESI 代表了每个缓存行在数据高速缓存上的 5 个状态,分别是:

• M:表示缓存行仅位于此数据高速缓存中,且被写脏;(UniqueDirty)

• O:表示缓存行可能位于多个数据高速缓存中,且被写脏;(ShareDirty)

• E:表示缓存行仅位于此数据高速缓存中,且是干净的;(UniqueClean)

• S:表示缓存行可能位于多个数据高速缓存中,且是干净的;(ShareClean)

• I:表示缓存行不在该数据高速缓存中。(Invalid)

那么MESI是什么原理?硬件如何维护多核CPU的数据一致性?答案参见知识星球讨论。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

异构计算下缓存一致性的重要性2024-10-24 3372

-

Redis缓存与Mysql如何保证一致性?2023-12-02 1980

-

如何保证缓存一致性2023-10-19 2684

-

管理基于Cortex-M7的MCU的高速缓存一致性2023-09-25 627

-

介绍下cpu缓存一致性(MESI协议)2023-06-09 6195

-

介绍ARM存储一致性模型的相关知识2023-02-14 2954

-

本周五|搞定缓存一致性验证,多核SoC设计就成功了一半2023-01-05 962

-

搞定缓存一致性验证,多核SoC设计就成功了一半2022-12-29 1279

-

小编科普CPU缓存一致性协议MESI2021-06-17 1672

-

管理基于Cortex®-M7的MCU的高速缓存一致性2021-04-01 983

-

自主驾驶系统将使用缓存一致性互连IP和非一致性互连IP2019-05-09 4081

-

Cache一致性协议优化研究2017-12-30 1179

-

加速器一致性接口2017-11-17 4545

-

一致性规划研究2009-04-06 675

全部0条评论

快来发表一下你的评论吧 !