PCB上的EMC设计能有哪些处理方法?

PCB设计

描述

滤波在EMI处理中的应用

做过EMC设计的都知道,滤波是必不可少的最常用的手段,常见的措施有加去耦电容、三端电容、磁珠、电源滤波、接口滤波,电容类去耦滤波要靠近滤波区域放置。

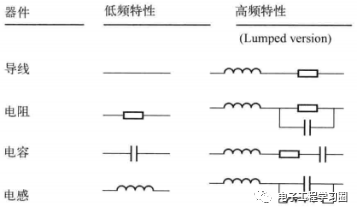

在滤波设计时,基本都是衰减高频噪声,在高频时,元器件会有不同的高频特性,如下图所示:

电阻、电容、电感、导线的高低频特性

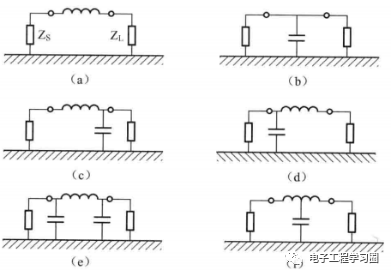

在滤波电路的EMC设计中,低通滤波器用来衰减高频噪声,滤波电路的典型结构如下图所示:

低通滤波电路的结构形式

图a为电感滤波器,适用于高频时源阻抗和负载阻抗较小的场合。

图b为电容滤波器,适用于高频时源阻抗和负载阻抗较大的场合。

图c和图d所示为L形滤波器,图c适用于高频时源阻抗小、负载阻抗较大的场合,图d适用于高频时源阻抗较大、负载阻抗较小的场合。

图e为π形滤波器,适用于高频时源阻抗和负载阻抗较大的场合。

图f为T形滤波器,适用于高频时源阻抗和负载阻抗都比较小的场合。

滤波电路在布局、布线时要注意:

1.确保滤波电路的地是一个低阻抗的地,不同功能电路之间不能存在共地阻抗

2.滤波电路的输入/输出不能互相交叉走线,需要隔离。

3.滤波电路的走线路径要短,要尽量减小滤波电容的等效串联电感和等效串联电阻

4.接口滤波电路应该尽量靠近接口的接插件放置。

EMC中地的分割与汇接

在PCB单板中,噪声波动大的地称为“动态地”,纹波小的地称为“静态地”。静态地和动态地一般要做隔离。

分地处理可以根据不同电源电压、数字和模拟信号、高速和低速信号、大电流和小电流来分别设置地线。这样可以防止不相容电路的回流信号叠加,防止共地线阻抗耦合。

例如数字地和模拟地,数字信号变化速度快,所以在数字地上引起的噪声会很大,而模拟信号需要一个干净的地参考工作,因此模拟地和数字地混在一起,噪声就会影响模拟信号。模拟地和数字地一般会分开处理,然后通过细的走线连接在一起,或单点连接。常用的单点连接方式有PCB走线、0欧姆电阻、磁珠和小电容等。

当然数字地和模拟地分开处理只是针对一般情况,如果数字地的噪声干扰幅度在允许的阈值范围内就可以合在一起。

EMC中的屏蔽与隔离

屏蔽根据原理不同可以分为电屏蔽、磁屏蔽和电磁屏蔽:

1.电屏蔽的实质是减小两个设备(或电路、组件、元件)间电场感应的影响。原理是将干扰源被良导体制成的屏蔽体导入地,因此电屏蔽需要保证接地良好及屏蔽体是良导体。

2.磁屏蔽的原理是由屏蔽体对干扰磁场提供低磁阻的磁通路,对干扰磁场进行分流。因此要选择钢、铁盒坡莫合金等高磁导率的材料设计壳体。

3.电磁屏蔽的原理是通过金属屏蔽体可以反射、吸收电磁波来屏蔽辐射干扰源。辐射的频率和屏蔽体的孔缝尺寸相关,设计电磁屏蔽时需要考虑。

在PCB设计时,对于敏感电路、强辐射电路等需要设计一个屏蔽腔,在屏蔽腔壁紧贴的部位要加上接地过孔,要求如下:

1.要有两排以上的过孔;

2.两排过孔要互相错开;

3.同一排的过孔间距要小于λ/20;

4.PCB与屏蔽腔焊接部位禁止有绿油;

5.处理射频信号,射频信号线在顶层穿过屏蔽壁时,要在屏蔽腔的相应位置开一个槽门,门高大于0.5mm,门宽要保证安装后信号线和屏蔽体间的距离大于1mm,如下图所示

屏蔽壁槽门

一些电磁计算软件如HFSS、Feco、EADS/EMC2000、Flowmerics/FLOWEMC和Ansys/Multiphysics等,可以帮助设计人员设计出符合EMC的结构,软件可对电子设备通过孔、缝等结构的电磁场辐射泄漏进行仿真,主要涉及器件、印制板建模及腔体结构建模等。

-

EMC设计—PCB高级EMC设计2025-05-28 378

-

PCB的EMC设计(一):层的设置与排布原则2025-05-17 1501

-

华为PCB的EMC设计指南2025-01-15 3011

-

高功率PCB中EMC的处理与优化策略2024-01-20 2725

-

提高电路板EMC能力PCB设计和布线方法2023-12-07 2161

-

PCB的EMC设计指南2022-06-06 1127

-

PCB板EMC整改方法讲解!2021-09-22 4029

-

如何提高PCB的EMC特性?2021-04-27 2123

-

PCB设计的EMC有哪些注意事项2020-07-09 3278

-

PCB板上抑制EMC干扰的各种方法总结2019-12-05 6228

-

PCB中EMC问题处理方案资料2018-01-24 967

-

解惑高级PCB-EMC问题2016-08-23 5224

-

PCB的EMC设计2010-02-24 1198

-

PCB设计考虑EMC的接地技巧2009-11-17 1595

全部0条评论

快来发表一下你的评论吧 !