RA6快速设计指南 [4] 时钟电路 (2)

描述

5

时钟电路

5.1 复位条件

复位后,RA6 MCU开始以中速片上振荡器 (MOCO) 作为主时钟源运行。复位时,默认情况下主振荡器和PLL处于关闭状态。HOCO和IWDT可能处于打开或关闭状态,具体取决于选项设置存储器中的设置(请参见后文第4节)。

5.2 时钟频率要求

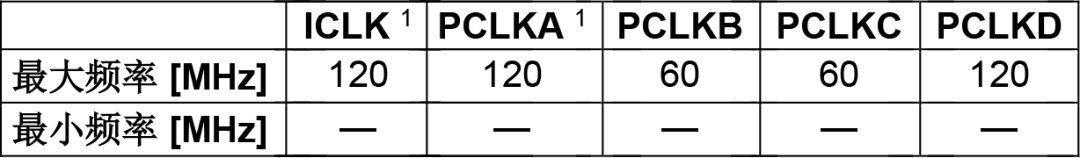

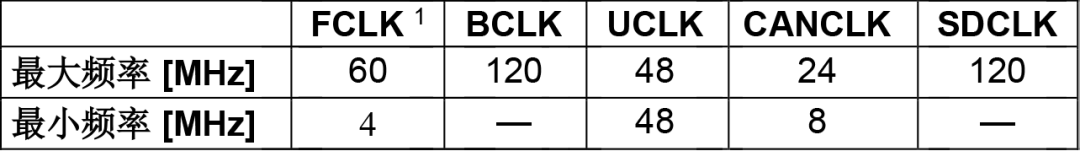

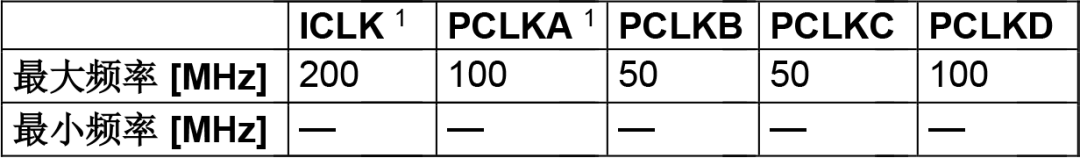

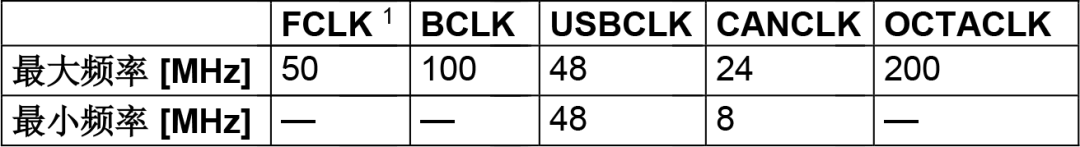

ICLK必须始终大于或等于BCLK。最小和最大频率如下表所示。有关详细信息,请参见《MCU硬件用户手册》中“时钟生成电路”一章的“概述”部分,其中包括外部和内部时钟源规范。更多详细信息,请参见《MCU硬件用户手册》中“电气特性”一章的“交流特性”部分。

表8. Arm Cortex-M4 MCU内部时钟的频率范围

1. 如果使用以太网控制器,则ICLK和PCLKA频率必须相同且至少为12.5MHz

1. 写入或擦除ROM或数据闪存时,FCLK必须以至少4MHz的频率运行。

表9. Arm Cortex-M33 MCU内部时钟的频率范围

如果使用以太网控制器,则ICLK和PCLKA频率必须相同且至少为12.5MHz。

写入或擦除ROM或数据闪存时,FCLK必须以至少4MHz的频率运行。

5.2.1 USB通信要求

RA系列的某些产品上提供的全速USB 2.0模块 (USBFS) 和高速USB 2.0模块 (USBHS) 需要48MHz的USB时钟信号(UCLK或USBCLK)。当使用USB并选择HOCO作为PLL的时钟源时,必须使能锁频环 (FLL) 功能。

使用USB时,仅可选择以下主时钟振荡器频率:8MHz、10MHz、12MHz、15MHz、16MHz、20MHz或24MHz。频率的选择取决于USB模块所需的时钟生成电路和48MHz时钟中可用的特定分频比。

对于Arm Cortex-M4器件,使用的分频器取决于SCKDIVCR2寄存器中UCK位的设置。

对于Arm Cortex-M33器件,使用的分频器取决于USBCKDIVCR寄存器中USBCKDIV位的设置。

5.2.2 以太网控制器要求

对于Arm Cortex-M4器件,当使用以太网控制器 (EtherC) 和以太网DMA控制器 (EDMAC) 时,PCLKA(以太网)必须与ICLK相同,并且两者的范围必须均为12.5MHz到120MHz。

对于Arm Cortex-M33器件,当使用以太网控制器 (EtherC) 和以太网DMA控制器 (EDMAC) 时,PCLKH(以太网)的范围必须为12.5MHz到100MHz。

5.2.3 ROM或数据闪存的编程和擦除要求

FCLK必须至少为4MHz才能在内部ROM和数据闪存上执行编程和擦除。

5.2.4 SDRAM控制器的要求

SDCLK来源于BCLK。请勿将SDCLK设置为高于系统时钟 (ICLK) 的频率。

5.3 降低时钟生成电路 (CGC) 的功耗

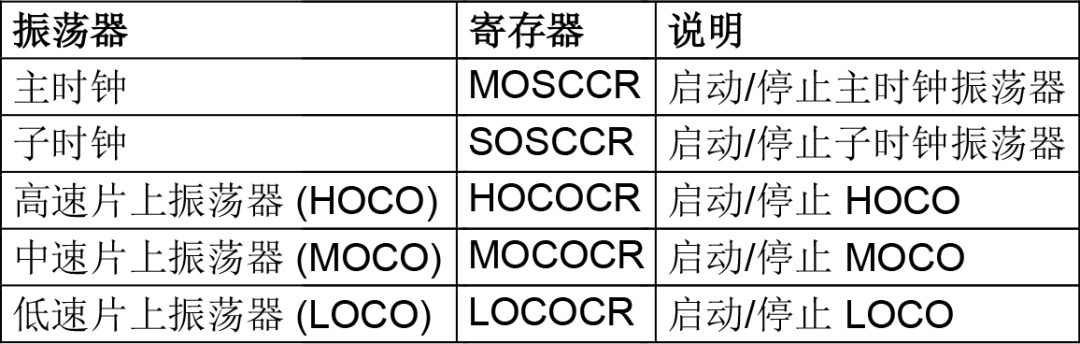

为了帮助节省功耗,请尽可能将所有未使用的时钟(例如BCLK)的分频器设置为最大可能值。另外,如果不使用时钟,请通过设置适当的寄存器来确保时钟已停止。下表显示了用于控制每个时钟源的寄存器。

表10. 时钟源配置寄存器

5.4 写入系统时钟控制寄存器

写入系统时钟分频控制寄存器 (SCKDIVCR)、系统时钟分频控制寄存器2 (SCKDIVCR2) 和系统时钟源控制寄存器 (SCKSCR) 中的各个位域时,应格外小心。

当将SCKDIVCR或SCKDIVCR2中的任何值从较低的分频比更改为较高的分频比时,请至少等待750ns,然后再更改该值。当将任何值从高分频比更改为低分频比时,请在更改值后至少等待250ns,然后再开始后续处理。

当将SCKSCR的值从PLL更改为其他时钟源时,请至少等待750ns,然后再更改该值。当将值从非PLL时钟源更改为PLL时,请在更改值后至少等待250ns,然后再开始后续处理。

测量等待时间的推荐方法是在软件中通过对指令周期进行计数来实现。确保考虑情况最差的使用条件,以确保会经过所需的等待时间。

-

RA2快速设计指南 [3] 时钟电路2023-10-24 1509

-

EK-RA4M2– 快速入门指南2023-07-04 450

-

RA6快速设计指南 [9] 存储器 (1)2023-06-21 2202

-

RA6快速设计指南 [8] 使用TrustZone®2023-06-19 1653

-

RA6快速设计指南 [5] 时钟电路 (3)2023-06-12 1578

-

RA6 MCU设计之时钟电路2023-06-09 792

-

RA6快速设计指南 [1] 简介,电源,仿真器支持(1)2023-06-04 2424

-

EK-RA4E2– 快速入门指南2023-05-12 503

-

EK-RA4M2 – 快速入门指南2023-02-03 557

-

CPK-RA6M4 快速入门指南2023-01-30 518

全部0条评论

快来发表一下你的评论吧 !