MAX2242功率放大器: 应用中的关键问题

描述

本文详细描述了MAX2242功率放大器(PA)的应用。主题包括:PCB布板、级间匹配、热管理以及裸片级(UCSP)封装。PA在CCK调制、第一旁瓣ACPR < -33dBc时提供+22dBm输出功率。片上功率检测器具有20dB动态范围。工作电压为2.7V至3.6V。使用FR4电路板材料。接地是高频、大功率电路的关键。为获得最佳性能,本文提供了电路图范例。对整个输入网络进行仿真时介绍了匹配电路设计。无论低频还是高频电路,电源线上都需要旁路电容。UCSP™封装图上焊球间距为0.5mm。MAX2242测试装置中用频谱分析仪测量旁瓣电平,用RF功率计测量输出功率。

本篇应用笔记的目的是为设计工程师提供关于MAX2242功率放大器的应用资料。本文涉及到许多主题,包括:印刷电路板图、级间匹配、输入输出阻抗、热管理以及裸片级封装。

简要说明

MAX2242是为2.4GHz ISM波段无线LAN应用而设计的线性功率放大器,能在第一旁瓣邻信道功率比(ACPR) < -33dBc和第二旁瓣ACPR < -55dBc时提供22.5dBm线性输出功率,符合IEEE® 802.11b 11MBps WLAN标准。该款PA的封装形式为3 x 4裸片级封装(UCSP),尺寸仅1.5mm x 2.0mm,非常适合小型PC卡和紧凑的闪存卡中的无线装置。

MAX2242功率放大器包括三级PA、功率检测器和电源管理电路。输出功率最大时,功率检测器能以±0.8dB的精度提供大于20dB的动态范围。利用该检测电路很容易实现精确的自动功率控制(ALC)功能。

MAX2242还有一个外部偏置控制引脚。输出功率较低时,利用外部DAC控制可以在保证足够的ACPR前提下降低电源电流,从而在全功率范围内保持尽可能高的效率。该器件工作在单电源+2.7V至+3.6V,内部关断功能将工作电流降至0.5µA,不需要外部电源开关。

应用

IEEE 802.11b

无线LAN

Home RF

2.4GHz无绳电话

2.4GHz ISM无线装置

特性

Po = 22.0dBm线性输出功率(第一旁瓣ACPR ≤ -33dBc、第二旁瓣ACPR ≤ -55dBc)

28dB增益

内置功率检测器

外部偏置控制降低电源电流

+2.7V至+3.6V单电源供电

裸片级封装(UCSP), 1.5mm x 2.0mm

设计要点

设计RF功率放大器时,需要考虑许多因素。在开始设计PCB图之前,必须很好地理解以下注意事项和数据资源(在下文中讨论):

PCB材料

接地方案

级间匹配

输入输出阻抗匹配

瞬态稳定性

热管理

裸片级封装(UCSP)

放大器测试方案

MAX2242数据资料

MAX2242评估板

PCB材料

印刷电路板材料应选用FR4或G-10。这类材料对大多数工作频率在3GHz以下的低成本无线应用都是很好的选择。MAX2242评估板使用的是4层FR4,其介电常数为4.5,绝缘层厚度6mil、1oz覆铜。

接地方案

良好的接地是极为重要的。当设计RF功率放大器时,不同元件的接地方法很重要,需要特别关注。 对低阻器件,考虑更多的是电流环路;而在高阻电路中则更关心高电压。这意味着需要仔细考虑接地的电流通路和元件的电流处理能力。请牢记,接地问题对大功率或高频电路更为关键。而本应用既要求大功率、也是高频电路!

在设计像MAX2242这样在2.45GHz下输出阻抗只有大约(8 + j5)Ω的低阻电路时,0.5nH电感就可以产生8Ω的感抗,8Ω的感抗相当于介电常数为4.5、厚度为6mil的FR4 PCB上60mil x 10mil的微带线产生的阻抗。

本应用中,良好的接地意味着将顶层元件层与地平面之间的感抗降至最小,使两个不同接地点之间的电势差为0V,避免两级之间寄生信号的耦合。

良好的接地需确保地平面尽可能连续,顶层地平面与底层的地平面应该利用多个镀金过孔连接。MAX2242有三个接地引脚:GND1、GND2和GND3。为了使感抗最小,这三个引脚接地的过孔位置要离器件尽可能近。MAX2242评估板上使用10mil镀金过孔接地,这些接地过孔的边缘与PA三个接地引脚的边缘距离为4mil。

图1所示表示如何用多个过孔改善电路板接地条件,通过将接地过孔放置在尽可能接近元件的位置使电路板不同层之间的感抗最小,也使无源元件的感抗最小。另外,将接地过孔沿RF通道摆放可以移动匹配元件的位置,进一步优化设计。

图1. MAX2242评估板顶层元件层视图。

级间匹配

由于级间匹配使部分匹配,多级放大器的外部级间匹配非常严格。为优化前级驱动和驱动放大器需要少量的电感,集总参数形式或分布参数形式均可。

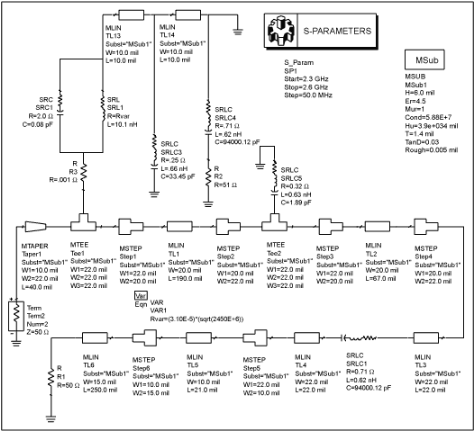

图2. MAX2242应用电路图。

输入输出阻抗匹配

输入输出阻抗匹配通过两个重复操作过程实现。第一步通过小信号仿真;第二步在大信号条件下根据实验经验调节。

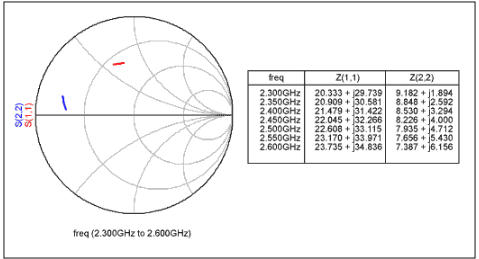

图3和图4所示为按照实际电路板尺寸得到的集总和分布元件模型,它们组成了最佳输入输出匹配网络。

图5是根据实际电路板仿真得到的最佳信号源Z(1,1)和负载Z(2,2)的阻抗。将Z(1,1)和Z(2,2)作为最佳信号源和负载阻抗的起点。

图3. 输入匹配网络。

图4. 输出匹配网络。

图5. 最佳信号源和负载阻抗。

瞬态稳定性

另外一个需要关注的问题是改善瞬态稳定性。按照以下设计准则设计将避免MAX2242出现不稳定。

首先,在主VCC输入端与地之间放置一个大的全局旁路电容(钽电容或电解电容),以避免电路出现振荡趋势。在其它VCC输入端增加局部退耦电容可以阻断与电源有关的反射。

电源的偏置引线需要加适当的屏蔽,以防寄生RF信号耦合到偏置电源。这对于串联增益为30dB或更高的多级PA尤为重要。电源偏置的屏蔽可以通过隔离开各个VCC引线实现,如果可能的话,将VCC引线布在寄生信号最弱的底层地平面上,或布在电路板上寄生信号最弱的其它层面上。

高增益多级放大器容易受到反馈的影响,这种反馈是由输出信号耦合到输入通道引起的。电路会在相位差达到180度的频点发生振荡。为了将输出耦合到输入的RF信号降至最小,建议RF信号走线尽可能短,以减小天线效应。

最后,电路板接地不良也会引起振荡。PA的大电流流经阻抗不为0的地线会将电压差和注入噪声引入地线系统。

图6. 包括内部框图的应用电路原理图。

图7. MAX2242评估板底层视图。

热管理

功率晶体管的集电结耗散大量功率。耗散功率表现为热量,这会使结点温度上升。但是结点温度TJ不能超过额定最大值TJMAX;否则晶体管可能永久损坏。即便不出现突然失效的情况,长期可靠性也会受到影响。硅器件的TJMAX大约为150°C,作为基于硅材料的器件,MAX2242以150°C或TJMAX作为它的最高结点温度。

MAX2242直接用评估板的地平面作为散热器。

图8用等效电路的形式表示热传导过程。功率耗散与电流对应,温度差与电压差对应,热阻与电阻对应。

图8. 热传导过程的等效电路。

TJ = (θJC + θCS + θSA) × PD + TA

裸片级封装(UCSP)

MAX2242采用裸片级封装。这种封装技术最大的优点是使IC到印刷电路板间的电感最小。另一个好处是减小封装尺寸、缩短研发周期,同时提高热传导特性。

欲获得更多关于UCSP的信息,请参见应用笔记1891:"晶片级封装(WLP)及其应用"。

图9. 裸片级封装。

放大器测试方案

图10. MAX2242测试方案。

审核编辑:郭婷

-

功率放大器选购注意什么问题2023-08-28 1379

-

功率放大器属于什么设备 功率放大器的基本要求2023-02-24 3368

-

MAX2242功率放大器:关键应用问题2023-02-23 1505

-

一文解读功率放大器(功率放大器如何选型)2022-11-15 4312

-

功率放大电路的关键问题 功率放大器的设计方法2022-08-08 4798

-

RF功率放大器的设计2021-12-22 12721

-

功率放大器的设计资料分享2021-11-11 3156

-

请问设计功率放大器的关键是什么2021-04-08 1622

-

行波管功率放大器的全面介绍2019-07-09 11168

-

功率放大器,超声功率放大器定义分类和应用2017-12-15 5818

-

功率放大器类型有哪些?功率放大器如何选择厂家2017-10-17 4393

-

功率放大器的性能指标,功率放大器的应用2017-05-12 4084

-

MAX2242功率放大器: 应用中的关键问题2008-09-17 1291

-

线性功率放大器设计和乙类和丙类功率放大器设计2008-08-17 9460

全部0条评论

快来发表一下你的评论吧 !