UHF ASK接收器的数据切片技术

描述

幅度移键控 (ASK) 和开关键控 (OOK) 接收器用于间歇性低数据速率应用,如 RKE、家庭安全、车库门开启器和遥控器。从远程发射器传输到ASK或OOK接收器的数据在数据切片器中重建。因此,数据切片器是 ASK 和 FSK 接收器的组成部分,根据 FCC 第 260.470 部分的规则,这些接收器在 15MHz 至 231MHz 短程 UHF 频段工作。本应用笔记解释了Maxim的UHF接收器(包括MAX1470、MAX1473和MAX1471)以及MAX7030和MAX7032等收发器的数据切片器的工作原理。

介绍

在最简单的形式中,数据切片器是一个模拟比较器,用于将解调的ASK信号与阈值进行比较。如果解调信号电压超过阈值,比较器输出将变为高电平,通常为电源电压。如果解调信号低于阈值,则比较器输出变为低电平,通常为零伏或地。

本应用笔记回顾了数据切片的两个方面:形成比较器阈值,以及防止比较器输出在没有信号时“抖动”。后一种操作通常称为“静噪”,可以通过在数据比较器的任一引脚上引入简单的电压偏移来完成。该失调可以直接来自电源或使用迟滞,迟滞是从数据切片器比较器反馈部分输出电压的过程。

我们将展示三种不同的阈值形成方法,以及三种引入静噪的不同方法,所有这些都可以通过添加一些外部电阻和/或电容器来完成。

解调ASK信号

Maxim ASK接收器使用解调器,该解调器是精心设计的限幅IF放大器。该放大器产生的电压与输入IF信号功率的对数成比例。当不存在信号时,放大器形成的电压由静态直流值和小时变噪声电压组成。图1显示了解调器输出响应ASK调制信号的波形。波形将在静态电压V之间来回切换0,当信号被键关闭时,并且信号电压,Vs,当信号按键打开时。在MAX1473中,V0典型值约为 1.2V 和 Vs灵敏度范围约为40mV,信号电平为非常高时约为1V。

图1.ASK解调器输出。

数据切片器框图

图2所示为MAX1473 ASK接收器的框图。本应用笔记重点介绍构成数据切片器的三个运算放大器和图右下角的七个引脚。图3中重新绘制了相同的功能块,以更清楚地说明每个电路的功能。图中电阻和电容的参考指示符与MAX1473评估板原理图中的参考指示符相同。运算放大器U1及其组件构成Sallen-Key数据滤波器,用于平滑ASK解调器检测到的幅度输出。运算放大器U2及其元件构成数据切片器比较器,而峰值检测运算放大器U3及其元件构成峰值检测器输出。现在,我们可以专注于该电路的各个部分,以了解数据切片操作中的各种选项。

图2.MAX1473 ASK接收器框图

图3.MAX1473中的数据切片器模块框图,包括外部元件

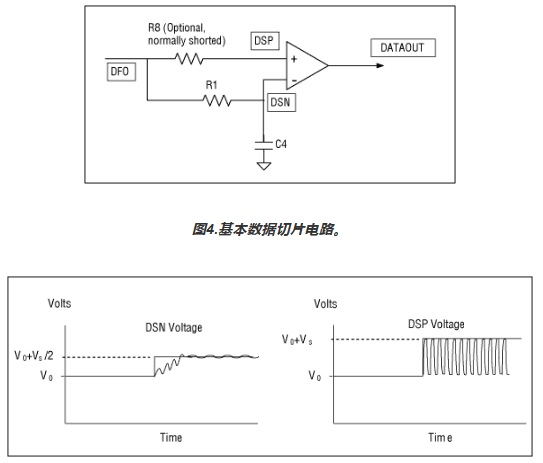

基本数据切片电路

图4所示为最简单的数据切片电路。数据滤波器DFO的输出进入数据切片器比较器DSP的正引脚,并通过简单的RC低通滤波器在DSN处形成切片阈值电压。当检测到并滤波的ASK信号DFO通过R1和C4形成的低通滤波器并建立时,DSN引脚的直流值介于该信号的最大和最小电压之间。图5显示了使用电压V的DSP和DSN上的波形0和 Vs从图 1 。请注意,DSN处的稳态电压为V0+ Vs/2.当接收到的数据流在数据包或帧的开头(以前导码或同步模式的形式)具有足够的额外位时,该电路可以承受损失,而R1-C4电路充电到正确的切片阈值时,该电路可以承受损失。当需要检测序列的前一位时,DSN处形成阈值电压的电路需要快速达到该电压。这就是峰值检测器可以提供帮助的地方。

图5.DSN和DSP信号,用于基本数据切片阈值的形成。

具有快速阈值形成功能的数据切片器

在ASK接收器中增加来自峰值检测器的电压可以加速数据切片阈值DSN的形成。图6中的电路说明了数据滤波器和峰值检波器对DSN的贡献如何结合起来产生快速响应的阈值电压。通过将DFO和PDOUT视为两个独立的电压源,我们可以使用叠加技术(单独找到每个源的响应,然后添加响应)来确定DSN的电压。峰值检波器的贡献是通过C13和C4形成的电容分压器的瞬时电压跳跃。该电压跳变衰减到由R1和R2形成的电阻分压器确定的稳态值。R1-C4低通滤波器的贡献与基波数据切片器电路缓慢上升的阈值相同。通过仔细选择两个R和两个C值,这两个贡献可以相互补充,并在DSN处形成阈值电压,理想情况下,该阈值电压立即跳到正确的阈值并保持在那里。

图6.用于快速阈值形成的电路和波形。

图7显示了两组不同电阻和电容的两个DSN波形。在DSN处产生最接近瞬时跳跃的阈值电压的组件组合遵循以下准则:

图7.使用峰值检测器的组合DSN电压与时间的关系。

我们可以通过一个具体的例子来说明 R 和 C 的选择。对于4kbps NRZ的ASK数据速率,R1-C4低通滤波器的时间常数应约为5位间隔,即5 x 0.25ms或1.25ms。R1 和 C4 的一个不错的选择是:

R1 = 25 kΩ 和 C4 = 0.047 μF

我们选择 C13 等于 C4,并使 R2 比 R1 大得多(因子 10 是好的):

R2 = 250 kΩ 和 C13 = 0.047 μF

此选项将导致阈值电压DSN从V跳升0到 V0+ Vs/2,然后稳定为 V0+0.55Vs.

请注意,这种建立快速切片阈值的方法会在阈值中创建一个小错误。此外,与阈值电压从初始值到最终值的变化相关的时间常数(这是一个非常小的变化)由以下乘积给出:

时间常数 = (R1 ||R2 x (C4 + C13))

这大约是R1-C4平滑电路时间常数的两倍。我们可以通过减小每个电容器值来纠正这种变化,但这不是必需的。由于阈值在初始跳跃后变化很小,因此时间常数并不像缺乏峰值检测器贡献的电路中那样重要。

带双峰检测器的数据切片器

将单峰值检测器与R-C平滑电路结合使用以形成切片阈值有一个小缺点:最终阈值与其理想值略有不同,理想值介于来自数据滤波器的最大和最小电压之间。

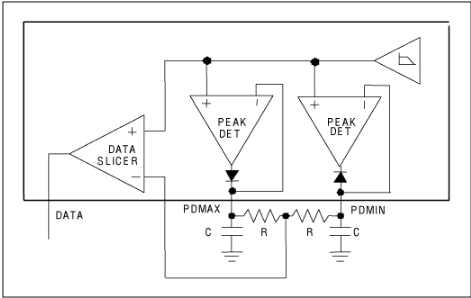

使用最大和最小峰值检测器是改善切片阈值快速建立的一种方法。MAX1471 ASK/FSK接收器、MAX7042 FSK接收器和MAX7030/MAX7031/MAX7032收发器具有最大和最小峰值检波器,因此无需单路R-C平滑电路。 图8显示了这些峰值检测器,每个检波器都有一个外部电阻和电容。每个电容保持峰值电压,每个电阻器为相关电容提供放电路径。这种设计允许峰值检波器动态跟踪数据滤波器输出电压的任何峰值变化。最大和最小峰值检波器可以一起使用,在数据流的最大和最小电压电平之间的一个值处形成一个数据切片器阈值电压。这些R-C对的RC时间常数应设置为位间隔的五倍左右,就像本应用笔记前面描述的简单阈值平滑电路一样。

图8.具有最大和最小峰值检测器的数据切片器电路。

如果某些因素导致基带信号幅度发生显著变化,例如AGC增益开关或上电瞬变,峰值检波器可能会“捕获”错误电平。如果检测到假峰,则切片水平不正确。由于RC时间常数的长度为几位,因此峰值检波器可能无法快速恢复。然而,带有双峰检波器的Maxim接收器都至少有一个用于复位峰值检波器输出的配置:接收器暂时允许峰值检波器跟踪信号。在MAX7042 FSK接收器中,峰值检波器通过暂时将ENABLE引脚拉低,然后将其返回到逻辑高电平设置来复位。MAX7030和MAX7031收发器以相同的方式复位峰值检波器,但只要AGC功能改变状态或T/R开关进入接收状态,也会复位峰值检波器。MAX1471 ASK/FSK接收器和MAX7032 ASK/FSK收发器通过串行端口复位峰值检波器,并在接收机进入休眠模式时自动复位峰值检波器。

向数据切片器添加基本静噪

在没有ASK信号的情况下,ASK检波器输出由具有时变噪声电压的直流电压组成,其峰峰值约为20mV。当数据切片器比较器在DSN阈值电压上来回摆动时,该噪声电压就会出现,导致比较器的输出“颤振”,即在电源电压和地之间快速随机地来回跳动。这种行为通常会不必要地唤醒微处理器,有时会给电源线增加噪声。阻止这种颤振的一种方法是使用简单的静噪电路,该电路在数据切片器的正(DSP)或负(DSN)引脚上增加一个小的直流偏移。

图9显示了使用电源作为直流偏移源的简单静噪电路。通常,您只需要一个大电阻,该电阻值是数据滤波器输出DFO和比较器任一输入引脚之间的电阻值的50至100倍。在图9的第一个电路中,小失调被添加到DSP中。如果失调约为30mV,则会发生两件事。首先,在没有信号的情况下,DSP直流电压上的噪声永远不会使DSP电压低于DSN的阈值水平;其次,DATAOUT引脚将保持高电平,即VDD.在图9的第二个电路中,偏移量被添加到DSN中。现在,DSP上直流电压上的噪声永远不会使DSP电压超过DSN增加的阈值,并且DATAOUT引脚将保持低电平,即GND。静噪电路会略微降低灵敏度(当仔细选择电阻分压器时,灵敏度约为1dB至2dB),当存在解调信号时,在DATAOUT处产生稍宽的正数据脉冲和稍窄的负数据脉冲。

图9.两个使用电源电压的简单静噪电路。

双峰检波器的静噪

使用上图8中的双峰检测器可以形成另一个简单的静噪电路。使两个电阻略微不相等会使阈值高于或低于两个峰值电压的中点,具体取决于哪个电阻更大。如果将门限设置为略高于中点30mV至50mV,则当没有信号存在时,DATAOUT引脚将保持低电平。类似地,如果阈值设置略低于中点,则当没有信号时,DATAOUT引脚将保持高电平。

向数据切片器添加电阻迟滞

您还可以使用一个大电阻将数据切片器的DATAOUT引脚连接到DSP引脚。图10显示了电阻迟滞的等效电路。这种方法与连接V的效果几乎相同DD通过电阻器连接到 DSP 引脚。这里唯一的区别是,当存在解调信号时,DSP处的小偏移仅在解调数据的正摆幅期间存在。因此,在 DATAOUT 处,正数据脉冲宽度的增加略小,因为正数据脉冲的前缘不会因偏移的存在而提前。

图 10.用于静噪功能的电阻迟滞电路。

向数据切片器添加容性迟滞

电容迟滞在DATAOUT信号的过度抖动和静噪或电阻迟滞引起的灵敏度降低之间提供了折衷方案。容性迟滞电路如图11所示。

与阻性迟滞一样,DATAOUT信号的一小部分被反馈回DSP引脚,这次通过电容分压器C7-C9。C10的典型电容值为7pf,C1000的典型电容值为9pf。添加到DSP的失调不同,因为它是一个瞬态失调,衰减的时间常数由下式给出:

R8 x (C9 + C7)

根据时间常数的长度,失调使DSP上的噪声不会低于切片阈值,直到失调衰减。这有效地增加了 DATAOUT 引脚保持高电平的时间,从而降低了 DATAOUT 颤振的频率。虽然电容迟滞不能完全消除颤振,但它减少了转换次数。

请注意,C9的存在会在解调的ASK信号路径中产生另一个R8的低通滤波器。与此滤波器时间常数相关的极点应大于Sallen-Key数据滤波器的带宽,以免滤波信号太慢。

图 11.电容迟滞电路和波形。

审核编辑:郭婷

-

深入解析MAX1473:315MHz/433MHz ASK超外差接收器2026-04-30 897

-

UHF ASK接收器的数据切片技术2023-03-04 1676

-

计算ASK接收器的灵敏度2023-03-02 2376

-

超低静态电源电流125kHz ASK接收器2023-01-23 2755

-

接收器技术的发展历程2021-01-21 1951

-

MICRF022YM-SW48 300-440 MHz ASK接收器的典型应用2020-07-21 1848

-

MICRF002是单芯片ASK / OOK(ON-OFF键控)RF接收器IC2020-07-20 1834

-

用于LTC5507 RFID读写器ASK接收器的宽带RF IC2020-06-09 2645

-

美信MAX1473:315MHz/433MHz ASK超外差接收器2014-03-01 4784

-

MAX7049 ASK/FSK UHF发射器2011-07-08 2669

-

PT4317-X:低功耗UHF OOK/ASK超外差接收芯片2011-05-06 4450

-

MAX1473集成宽动态范围ASK超外差接收器2011-02-12 2540

-

普诚推出低功耗UHF OOK/ASK超外差接收器PT43172010-11-19 2854

-

具有输出滤波器的RFID阅读器ASK接收器图2009-09-02 1619

全部0条评论

快来发表一下你的评论吧 !