设计数字无线电接收器的基础知识

描述

本文介绍了设计数字无线电接收机的基础知识。随着数据转换器和无线电技术的许多新进展,复杂的接收器设计已大大简化。本文试图解释如何计算这种接收器的灵敏度和选择性。它绝不是详尽的阐述,而是此类设计中涉及的许多技术和计算的入门。

无线电设计和架构的许多进步现在允许无线电设计领域的快速变化。这些变化允许通过使用数字元件来取代不可靠和不准确的模拟元件来减小尺寸、成本和复杂性并改善制造。为此,半导体设计和制造需要取得许多进展,并在过去几年中取得了成果。其中一些进步包括更好的集成混频器、LNA、改进的SAW滤波器、低成本高性能ADC以及可编程数字调谐器和滤波器。本文总结了这些器件的设计问题以及这些器件与完整无线电系统的接口。

什么是收音机?

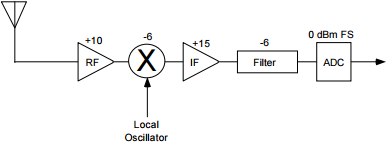

传统上,无线电被认为是连接到天线及其后面一切的“盒子”,但是,许多系统设计被划分为两个独立的子系统。无线电和数字处理器。通过这种分割,无线电的目的是向下转换和过滤所需的信号,然后将信息数字化。同样,数字处理器的目的是获取数字化数据并提取所需的信息。

需要了解的重要一点是,数字接收器与数字无线电(调制)不是一回事。事实上,数字接收器在接收任何模拟信号(如AM或FM)方面都非常出色。 数字接收器可用于接收任何类型的调制,包括任何模拟或数字调制标准。此外,由于数字处理器的核心是数字信号处理器(DSP),这允许通过软件控制整个无线电接收器本身的许多方面。因此,这些DSP可以根据客户细分通过升级或新功能重新编程,所有这些都使用相同的硬件。但是,这本身就是一个完整的讨论,而不是本文的重点。

本文的重点是无线电以及如何预测/设计性能。将讨论以下主题:

可用噪声功率

级联噪声系数

噪声系数和模数转换器

转换增益和灵敏度

ADC杂散信号和抖动

三阶截点

模数转换器时钟抖动

相位噪声

射频部分的 IP3

单载波与多载波

正在讨论两种基本类型的无线电。第一个称为单载波接收器,第二个称为多载波接收器 它们的名字暗示了显而易见的,但它们的功能可能并不完全清楚。单载波接收器是一种传统的无线电接收器,在IF级的模拟滤波器中产生选择性。多载波接收器使用单个RF/IF模拟条处理频带内的所有信号,并在模数转换器之后的数字滤波器内获得选择性。这种接收器的好处是,在具有多个接收器调谐到同一频段内不同频率的应用中,可以实现更小的系统设计,并且由于消除了冗余电路而降低了成本。典型的应用是蜂窝/无线本地环路基站。另一个应用可能是监视接收器,通常使用扫描仪来监视多个频率。此应用程序允许同时监控多个频率,而无需顺序扫描。

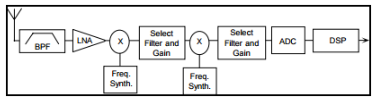

典型的单载波接收器

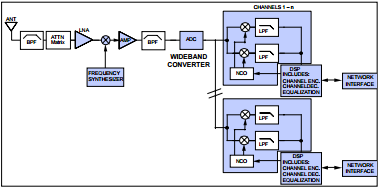

典型的多载波接收器

实现数字无线电接收器的优势

在详细讨论设计数字无线电接收器之前,需要讨论一些技术优势。其中包括过采样、处理增益、欠采样、频率规划/杂散放置。其中许多提供了传统无线电接收器设计无法实现的技术优势。

过采样和过程增益

奈奎斯特准则紧凑地确定了任何给定信号所需的采样速率。很多时候,奈奎斯特速率被引用为采样速率,是最高频率分量的两倍。这意味着对于70 MHz的中频采样应用,将需要140 MSPS的采样速率。如果我们的信号在5 MHz左右仅占用70 MHz,那么以140 MSPS采样几乎是浪费的。相反,奈奎斯特要求对信号进行两倍于信号带宽的采样。因此,如果我们的信号带宽为5 MHz,则以10 MHz采样就足够了。除此之外的任何内容都称为过度采样。过采样是一项非常重要的功能,因为它允许在数字域中有效增益接收的SNR。

与过度采样相反的是欠采样的行为。欠采样是以远低于实际信号频率一半的频率进行采样的行为(请参阅下面关于欠采样的部分)。因此,可以同时进行过采样和欠采样,因为一个是根据带宽定义的,另一个是根据感兴趣的频率定义的。

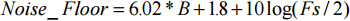

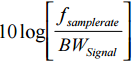

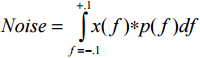

在任何数字化过程中,信号采样速度越快,本底噪声就越低,因为噪声会分散到更多的频率上。总集成噪声保持不变,但现在分布在更多频率上,如果ADC后面有一个数字滤波器,则具有优势。本底噪声遵循以下公式:

该公式表示转换器内的量化噪声电平,并显示噪声与采样速率FS之间的关系。因此,采样率每加倍,有效本底噪声就会提高3 dB!

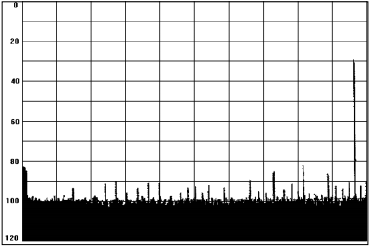

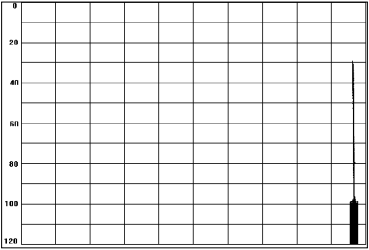

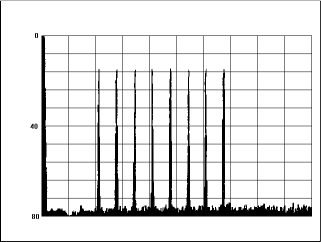

数字滤波具有去除所有不需要的噪声和杂散信号的作用,只留下所需的信号,如下图所示。

数字滤波前的典型ADC频谱

数字滤波后的典型ADC频谱

如上图所示,ADC的SNR可能会得到极大改善。事实上,SNR可以通过使用以下公式来改善:

如图所示,采样速率和信号带宽之比越大,过程增益就越高。事实上,可以实现高达30 dB的增益。

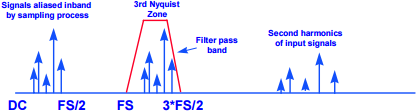

欠采样和频率转换

如前所述,欠采样是以远低于实际信号频率一半的频率进行采样的行为。例如,以70 MSPS采样的13 MHz信号就是欠采样的一个例子。

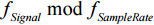

采样不足很重要,因为它可以提供与混合非常相似的功能。当信号采样不足时,频率混叠到基带或第一奈奎斯特区,就好像它们最初在基带中一样。例如,我们上面的70 MHz信号在以13 MSPS采样时将以5 MHz显示。这在数学上可以用以下方式描述:

该方程给出了第一和第二奈奎斯特区的频率。由于ADC将所有信息混为第一个奈奎斯特区,因此必须检查该方程生成的结果,以查看它们是否高于f采样率/2 .如果是,则必须通过从f中减去结果来将频率折回第一个奈奎斯特区采样率.

下表显示了如何将信号混叠为基带及其频谱方向。虽然采样(混叠)的过程与混合(乘法)不同,但结果非常相似,但采样率是周期性的。另一个现象是光谱反转。与混频器一样,某些产品在采样过程中会发生反转,例如上下边带反转。下表还显示了哪些情况会导致光谱反转。

| 输入信号 | 频率范围 | 频移 | 光谱检测 |

|

1圣奈奎斯特 区 |

直流 - FS/2 | 输入 | 正常 |

|

2德·奈奎斯特 区 |

FS/2 - FS | FS输入 | 反 |

|

3RD奈奎斯特 区 |

FS - 3FS/2 | 输入 - 满量程 | 正常 |

|

4千奈奎斯特 区 |

3FS/2 - 2FS | 2FS - 输入 | 反 |

|

5千奈奎斯特 区 |

2FS - 5FS/2 | 输入 - 2FS | 正常 |

频率规划和杂散放置

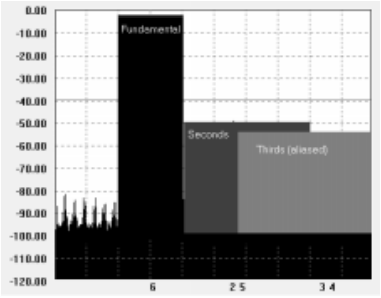

设计无线电架构时面临的最大挑战之一是中频频率布局。使这个问题更加复杂的是,驱动放大器和ADC往往会产生不需要的谐波,这些谐波出现在数据转换的数字频谱中,表现为错误信号。无论应用是否为宽带,仔细选择采样速率和IF频率都可以将这些杂散放置在与数字调谐器/滤波器(如AD6620)一起使用时使其无害的位置,该数字调谐器/滤波器可以选择目标信号并抑制所有其他信号。所有这些都很好,因为通过仔细选择输入频率范围和采样速率,驱动放大器和ADC谐波实际上可以放置在带外。过采样只能通过提供更多频谱来简化问题,使谐波无害地落入其中。

例如,如果确定二次和三次谐波特别高,则通过仔细选择模拟信号相对于采样速率的落点,可以将这些二次和三次谐波置于带外。对于编码速率等于40.96 MSPS,信号带宽为5.12 MHz的情况,将IF置于5.12和10.24 MHz之间会使二次和三次谐波脱离带外,如下表所示。虽然这个例子非常简单,但它可以定制以适应许多不同的应用。

可以看出,二次和三次谐波远离目标频段,不会对基波分量造成干扰。应该注意的是,秒和三确实彼此重叠,并且三分别名围绕 FS/2。在表格中,如下所示。

| 编码速率: | 40.96 兆字节 |

| 基本 | 5.12 - 10.24兆赫 |

| 二次谐波: | 10.24 - 20.48兆赫 |

| 三次谐波: | 15.36 - 10.24兆赫 |

频率规划的另一个例子可以在欠采样中找到。如果模拟输入信号范围为直流至FS/2,则放大器和滤波器组合必须按照所需的规格执行。但是,如果信号放置在第三奈奎斯特区(FS至3FS/2),则不再需要放大器满足系统规格要求的谐波性能,因为所有谐波都将落在通带滤波器之外。例如,通带滤波器的范围从FS到3FS/2。二次谐波的范围从2FS到3FS,远远超出通带滤波器的范围。然后,如果ADC在目标频率下满足基本规格,则负担将转嫁给滤波器设计。在许多应用中,这是一个值得的权衡,因为许多复杂的滤波器可以在这些相对较高的IF频率下使用SAW和LCR技术轻松实现。虽然这种技术可以放松驱动放大器的谐波性能,但不能牺牲交调性能。

使用这种技术使谐波落在奈奎斯特目标区域之外,可以很容易地对其进行滤波,如上所示。但是,如果ADC仍然产生自己的谐波,则可以使用前面讨论的技术来仔细选择采样速率和模拟频率,以便谐波落入带宽的未使用部分并进行数字滤波。

接收器性能预期

考虑到这些想法,如何确定收音机的性能以及可以进行哪些权衡。传统无线电设计中的许多技术都可以使用,如下所示。在下面的讨论中,多通道和单通道无线电之间存在一些差异。这些将被指出。请记住,此讨论尚未完成,许多领域未触及。有关此主题的其他阅读,请参阅本文末尾的参考资料之一。此外,本讨论仅涵盖交付给 DSP 的数据。许多接收器使用专有方案,通过额外的噪声抑制和外差消除来进一步提高性能。

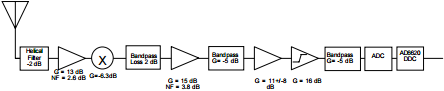

对于下面的讨论,通用接收器设计如上所示。本讨论从天线开始,最后以数字调谐器/滤波器结束。超出这一点的是数字处理器,它超出了本讨论的范围。

分析从几个假设开始。首先,假设接收器是噪声限制的。也就是说,带内不存在会限制性能的杂散。可以合理地假设可以做出LO和IF选择,以便这是真的。此外,稍后将证明,ADC内部产生的杂散通常不是问题,因为它们通常可以通过应用抖动或通过明智地使用过采样和信号放置来消除。在某些情况下,这些可能不是现实的假设,但它们确实提供了一个起点,可以对性能限制进行基准标记。

第二个假设是接收器前端的带宽是我们的奈奎斯特带宽。虽然我们实际分配的带宽可能只有5 MHz,但使用奈奎斯特带宽将简化计算过程。因此,65 MSPS的采样速率将提供32.5 MHz的奈奎斯特带宽。

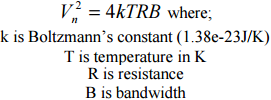

可用噪声功率

要开始分析,必须考虑天线端口的噪声。由于正确匹配的天线显然是电阻性的,因此可以使用以下公式来确定匹配输入端子上的噪声电压。

来自电源的可用功率,在这种情况下,天线是:

当将前面的等式替换为以下公式时,这简化了:

因此,实际上,在这种情况下,来自源的可用噪声功率与非零和有限电阻值的阻抗无关。

这很重要,因为这是我们的接收器将与之进行比较的参考点。在处理阶段的噪声系数时,通常会说它表现出比“kT”噪声高出“x”dB。这是此表达式的来源。

对于通过接收器的每个逐级,该噪声会因级的噪声系数而降低,如下所述。最后,当对通道进行调谐和滤波时,大部分噪声被去除,只留下目标通道内的噪声。

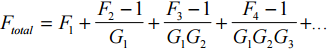

级联噪声系数

噪声系数是一个品质因数,用于描述无线电接收链中信号增加了多少噪声。通常,它以dB为单位指定,尽管在计算噪声系数时,使用数值比率(非对数)。非对数称为噪声因子,通常表示为F,其定义如下所示。

一旦将噪声系数分配给收音机中的每个阶段,它们就可以用来确定它们的级联性能。以输入端口为基准的总噪声因数可按如下方式计算。

上面的F是每个串联级的噪声因子,而G是级的增益。此时,噪声因子或增益均不是对数形式。应用此公式时,这会将所有分量噪声反射到天线端口。因此,上一节的可用噪声可以直接使用噪声系数来降低。

例如,如果可用噪声为-100 dBm,计算噪声系数为10 dB,转换增益为20 dB,则输出端的总等效噪声为-70 dBm。

应用这些方程时需要考虑几点。首先,无源元件假设噪声系数等于其损耗。其次,在应用方程之前,可以对串联的无源分量求和。例如,如果两个低通滤波器串联,每个滤波器的插入损耗为3 dB,则可以将它们组合在一起,并假定单个元件的损耗为6 dB。最后,混音器通常没有制造商分配给它们的噪声系数。如果未指定,则可以使用插入损耗,但是,如果器件提供了噪声系数,则应使用噪声系数。

噪声系数和模数转换器

虽然可以为ADC分配噪声系数,但以不同的方式工作ADC通常更容易。ADC是电压器件,而噪声系数实际上是一个噪声功率问题。因此,通常更容易将模拟部分与ADC的噪声系数相处,然后转换为ADC的电压。然后将ADC的噪声转换为输入参考电压。然后,可以将来自模拟和ADC的噪声相加到ADC输入端,以求出总有效噪声。

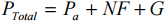

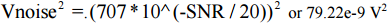

对于此应用,我们选择了AD9042或AD6640等12位模数转换器ADC。这些产品可以采样高达65 MSPS,该速率适用于整个频段AMPS数字化,并能够实现GSM 5倍参考时钟速率。这对于AMPS,GSM和CDMA应用来说绰绰有余。根据数据表,典型SNR为68dB。因此,下一步是计算ADC噪声引起的接收器内噪声衰减。同样,最简单的方法是将SNR和接收器噪声转换为均方根伏特,然后将它们相加为总均方根噪声。如果 ADC 具有 2 V 峰峰值输入范围:

该电压表示ADC内的所有噪声、热噪声和量化噪声。ADC 的满量程范围为 .707 V 均方根。

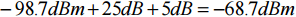

计算ADC等效输入噪声后,下一个计算是接收器本身产生的噪声。由于我们假设接收器带宽是奈奎斯特带宽,因此65 MSPS的采样速率产生32.5 MHz的带宽。根据可用的噪声功率公式,模拟前端的噪声功率为134.55E15瓦或-98.7 dBm。这是天线上存在的噪声,必须通过转换增益来获得,并通过噪声系数来降低。如果转换增益为25 dB,噪声系数为5 dB,则呈现给ADC输入网络的噪声为:

转换为 50 欧姆(134.9e-12 瓦)。由于ADC的输入阻抗约为1000欧姆,因此我们必须将标准的50欧姆IF阻抗与此相匹配,或者将ADC阻抗压低。一个合理的折衷方案是用一个并联电阻将范围垫低至200欧姆,然后使用1:4变压器来匹配其余部分。变压器还用于将非平衡输入转换为ADC所需的平衡信号,并提供一些电压增益。由于阻抗阶跃为1:4,因此在此过程中的电压增益也为2。

根据这个等式,我们的电压平方为 50 欧姆是 6.745e-9 或等于 200 欧姆,26.98e-9。

现在我们知道了来自ADC和RF前端的噪声,系统中的总噪声可以通过平方和的平方根来计算。因此,总电压为325.9 uV。这是ADC中由于接收器噪声和ADC噪声(包括量化噪声)而存在的总噪声。

转换增益和灵敏度

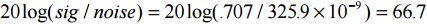

该噪声电压对ADC的整体性能有何影响?假设接收器带宽中仅存在一个RF信号。信噪比为:

由于这是一个过采样应用,实际信号带宽远小于采样速率,因此一旦经过数字滤波,噪声将大大降低。由于前端带宽与我们的ADC带宽相同,因此ADC噪声和RF/IF噪声将以相同的速率改善。由于许多通信标准支持窄信道带宽,因此我们假设信道为30 kHz。因此,我们从过程增益中获得33.4 dB。因此,我们原来的66.7 dB信噪比现在是100.1 dB。请记住,SNR增加是因为滤除过多的噪声,这是过程增益的来源。

图 13 八个相等功率载波

如果这是多载波无线电,则必须与其他RF载波共享ADC动态范围。例如,如果有八个功率相等的载波,如果考虑峰峰值信号,则每个信号不应大于总范围的 1/8。但是,由于信号在接收器中通常彼此不同相(因为遥控器未锁相),因此信号很少会对齐。因此,所需的分贝远低于所需的 18 dB。由于实际上,任何时候都不会超过2个信号对齐,并且由于它们是调制信号,因此仅保留3 dB用于裕量。如果信号确实对齐并导致转换器削波,则在过驱条件清除之前,它只会发生一小部分秒。对于单载波无线电,则不需要动态余量。

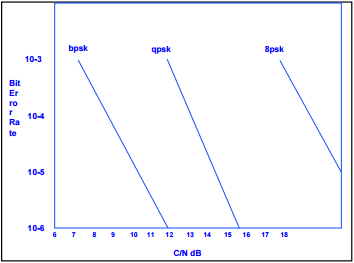

根据调制方案的不同,需要最小C/N才能充分解调。如果方案是数字方案,则必须考虑误码率(BER),如下所示。假设要求最小C/N为10 dB,我们的输入信号电平不能太小,以至于剩余SNR小于10 dB。因此,我们的信号电平可能会从目前的电平下降90.1 dB。由于ADC的满量程范围为+4 dBm(200欧姆),因此ADC输入端的信号电平为–86.1 dBm。如果RF/IF路径中的增益为25 dB,则天线上的接收器灵敏度将为–86.1减去25 dB或–111.1 dBm。如果需要更高的灵敏度,则可以在RF/IF级中运行更大的增益。然而,噪声系数与增益无关,增益的增加也可能对额外增益级的噪声性能产生不利影响。

图 14 误码率与 SNR 的关系

ADC杂散信号和抖动

噪声受限示例不能充分说明接收器的真正限制。SFDR等其他限制比SNR和噪声更具限制性。假设模数转换器的SFDR规格为-80 dBFS或-76 dBm(满量程= +4dBm)。还假设可容忍载波与干扰源的C/I(不同于C / N)比为18 dB。这意味着最小信号电平为 -62 dBFS(-80 加 18)或 -58 dBm。在天线上,这是 -83 dBm。因此,可以看出,SFDR(单音或多音)会在达到实际噪声限制之前很久就限制接收器的性能。

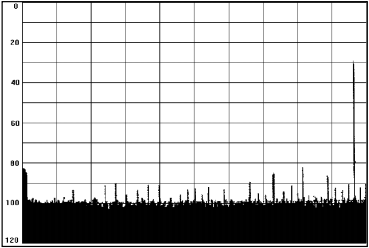

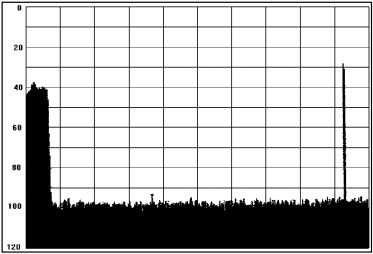

但是,一种称为抖动的技术可以极大地改善SFDR。如ADI公司应用笔记AN410所示,增加带外噪声可以很好地改善SFDR到本底噪声。虽然抖动量因转换器而异,但该技术适用于所有ADC,只要静态DNL是性能限制,而不是压摆率等交流问题。在应用笔记中记录的AD9042中,增加的噪声量仅为-32.5 dBm或21个代码均方根。如下图所示,抖动之前和之后的绘图提供了对改进潜力的洞察。简单来说,抖动的工作原理是获取ADC内产生的相干杂散信号并将其随机化。由于杂散的能量必须守恒,抖动只会使它们在转换器的地板上显示为额外的噪声。这可以在抖动之前和之后的图中观察到,转换器的平均本底噪声略有增加。因此,通过使用带外抖动做出的权衡是,实际上可以消除所有内部产生的杂散信号,但是,转换器的整体SNR略有下降,与噪声限制示例相比,实际上灵敏度损失小于1 dB,并且比前面显示的SFDR限制示例要好得多。

无抖动的 ADC

带抖动的 ADC

在结束话题之前,关于抖动的两个要点。首先,在多载波接收器中,不能预期所有通道都是相关的。如果这是真的,那么多个信号通常会作为接收器通道的自抖动。虽然有时确实如此,但有时当信号强度较弱时,需要添加额外的抖动来填充。

其次,仅模拟前端贡献的噪声不足以使ADC抖动。从上面的例子中,添加了32.5 dBm的抖动,以产生SFDR的最佳改善。相比之下,模拟前端仅提供–68 dBm的噪声功率,远未达到提供最佳性能所需的功率。

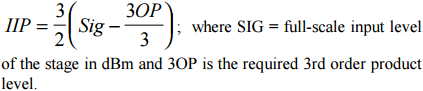

三阶截点

除转换器SFDR外,RF部分还有助于接收器的杂散性能。这些杂散不受抖动等技术的影响,必须加以解决以防止接收器性能中断。三阶交调截点是一个重要的度量,因为接收链内的信号电平通过接收器设计而增加。

为了了解宽带RF组件的性能要求,我们将回顾GSM规范,这可能是最苛刻的接收器应用。

GSM 接收器必须能够恢复功率电平在 -13 dBm 和 -104 dBm 之间的信号。还假设ADC的满量程为0 dBm,通过接收器滤波器和混频器的损耗为12 dB。此外,由于要同时处理多个信号,因此不应使用AGC。这将降低RF灵敏度并导致较弱的信号被丢弃。根据这些信息,RF/IF增益计算为25 dB(0=-13-6-6+x)。

三阶输入交调截点注意事项

所需的25 dB增益如图所示分布。尽管一个完整的系统将具有其他组件,但这将有助于此讨论。由此,当满量程GSM信号为-13 dBm时,ADC输入将为0 dBm。但是,对于-104 dBm的最小GSM信号,ADC上的信号将为-91 dBm。从这一点来看,上面的讨论可用于确定ADC在噪声性能和杂散性能方面的适用性。

现在有了这些信号和所需的系统增益,现在可以检查由-13 dBm满量程信号驱动的放大器和混频器规格。求解信号满量程方面的三阶积:

假设整体杂散性能必须大于100 dB,求解前端放大器的公式表明,三阶输入放大器的IIP>+37 dBm。在混频器上,信号电平增加了10 dB,新的信号电平为-3 dBm。但是,由于混频器在其输出端指定,因此该电平至少降低6 dB至–9 dBm。因此,对于混频器,OIP>+41 dBm。由于混频器在其输出端指定。在最终增益级,信号将衰减至-9 dBm(与混频器输出相同)。对于IF放大器,IIP>+41 dBm。如果满足这些规格,则性能应等于

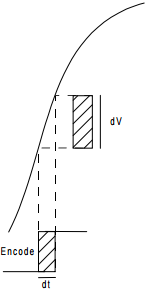

模数转换器时钟抖动

对良好的无线电性能至关重要的一个动态规格是ADC时钟抖动。虽然低抖动对于出色的基带性能很重要,但在采样较高频率的信号(高压摆率)时,例如欠采样应用中,其影响会放大。不良抖动规格的总体影响是随着输入频率的增加,SNR会降低。术语孔径抖动和孔径不确定性经常在文本中互换。在此应用程序中,它们具有相同的含义。孔径不确定度是编码过程中样本间的变化。孔径不确定性有三个残余效应,第一个是系统噪声的增加,第二个是采样信号本身实际相位的不确定性,第三个是码间干扰。中频采样时,需要小于1 pS的孔径不确定度,以实现所需的噪声性能。在相位精度和码间干扰方面,孔径不确定性的影响很小。在1 pS rms的最坏情况下,IF为250 MHz时,相位不确定度或误差为0.09度rms。即使对于GSM等苛刻的规范,这也是完全可以接受的。因此,本分析的重点将放在孔径不确定性引起的整体噪声贡献上。

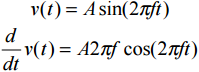

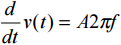

在正弦波中,最大压摆率在过零处。此时,压摆率由计算在 t=0 时的正弦函数的一阶导数定义:

在 T=0 时计算,余弦函数的计算结果为 1,方程简化为:

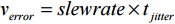

压摆率的单位是伏特每秒,并产生信号通过输入信号过零的速度。在采样系统中,参考时钟用于对输入信号进行采样。如果采样时钟具有孔径不确定性,则会产生误差电压。该误差电压可以通过将输入压摆率乘以“抖动”来确定。

通过分析单位,可以看出这产生了伏特单位。通常,孔径不确定性以秒均方根表示,因此,误差电压将以伏特均方根为单位。对该等式的进一步分析表明,随着模拟输入频率的增加,均方根误差电压也与孔径不确定性成正比。

在IF采样转换器中,时钟纯度至关重要。与混频过程一样,输入信号乘以本振,在本例中为采样时钟。由于时间乘法是频域中的卷积,因此采样时钟的频谱与输入信号的频谱卷积。由于孔径不确定性是时钟上的宽带噪声,因此在采样频谱中也显示为宽带噪声。由于ADC是一个采样系统,频谱是周期性的,并围绕采样速率重复。因此,这种宽带噪声会降低ADC的本底噪声性能。受孔径不确定性限制的ADC的理论信噪比由以下公式确定。

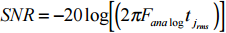

如果针对201 MHz和.7 pS rms的模拟输入“抖动”计算此公式,则理论SNR限制为61 dB。应该注意的是,这与使用另一个混频器级时所要求的要求相同。因此,需要非常高的动态范围和非常高的模拟输入频率的系统也需要非常低的“抖动”编码源。使用标准TTL/CMOS时钟振荡器模块时,ADC和振荡器均验证了0.7 pS rms。使用低噪声模块可以实现更好的数字。

在考虑整体系统性能时,可以使用更广义的公式。该方程以前一个方程为基础,但包括热噪声和微分非线性的影响。

虽然这是一个简单的等式,但它提供了对数据转换器预期噪声性能的深入了解。

相位噪声

虽然频率合成器的相位噪声与编码时钟上的抖动相似,但它对接收器的影响略有不同,但最终,效果非常相似。抖动和相位噪声之间的主要区别在于,抖动是一个宽带问题,在采样时钟周围具有均匀的密度,相位噪声是局部振荡器周围的非均匀分布,通常离音调越远越好。与抖动一样,相位噪声越少越好。

由于本振与输入信号混合,LO上的噪声会影响目标信号。混频器的频域过程是卷积(混频器的时域过程是乘法)。作为混频的结果,来自LO的相位噪声导致来自相邻(和有源)通道的能量被集成到所需通道中,从而增加本底噪声。这称为倒易混合。为了确定备用通道被全功率信号占用时未使用通道中的噪声量,提供以下分析。

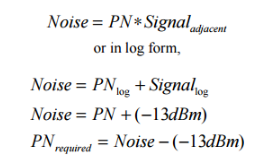

同样,由于GSM是一个困难的规范,这将作为一个示例。在这种情况下,以下等式有效。

其中噪声是由相位噪声引起的目标通道中的噪声,x(f)是以非对数格式表示的相位噪声,p(f)是GMSK函数的频谱密度函数。在本例中,假设 GSM 信号功率为 -13 dBm。此外,假设LO的相位噪声在整个频率范围内是恒定的(大多数情况下,相位噪声随着载波偏移而降低)。在这些假设下,当这个方程在通道带宽上积分时,一个简单的方程就会消失。由于假设x(f)是恒定的(PN - 相位噪声),并且满量程GSM通道的积分功率为-13 dBm,因此公式简化为:

因为目标是要求相位噪声低于热噪声。假设混频器的噪声与天线的噪声相同,则为-121 dBm(天线处的噪声为200 kHz -P一个= 千兆字节) 可以使用。因此,LO的相位噪声必须低于-108 dBm,失调为200 kHz。

审核编辑:郭婷

-

有源FM/AM/SW无线电接收天线电路2022-08-06 6863

-

软件无线电接收器的结构2022-08-04 3700

-

Moku:Go轻松助力校园无线电接收实验的教学2022-07-27 1633

-

爱华无线电接收器FR-C90维修手册2021-05-27 1481

-

TEA5757TEA5759自调谐无线电接收器STR相关资料推荐2021-05-24 2267

-

RF前端数字无线电接收芯片STA001相关资料下载2021-05-17 1074

-

软件无线电接收机2021-04-20 1248

-

如何为我的软件定义无线电接收器架构构建模拟前端?2019-09-10 1754

-

科学家研制出的全新无线电接收器DESHIMA2019-08-20 1448

-

哈佛研究人员创造原子尺度最小无线电接收器2016-12-22 3519

-

简易无线电接收器电路2011-12-09 12767

-

芯科推出新一代多波段无线电接收器IC Si484x2011-08-31 4320

-

FPGA在软件无线电接收机实现数字定时恢复2009-07-27 561

-

无线电基础知识2006-04-16 7564

全部0条评论

快来发表一下你的评论吧 !