Neoverse N2和CMN-700系统的PoC点在哪里?

电子说

描述

DC IVAC/ DC CIVAC指令用于将一个虚拟地址对应的cache line从data cache或是unified cache失效或清除失效到PoC点。N2 core硬件默认会将DC IVAC升级为DC CIVAC操作。

Point of Coherency (PoC)位于:确保系统中所有可以访问内存的agent访问这个地址可以看到同样的copy的地方,不管它的访问内存类型(memory type)和cache属性(cacheable or non cacheable)是什么。

在很多系统中,它都位于系统主内存。

在一个N2+CMN-700的系统中,

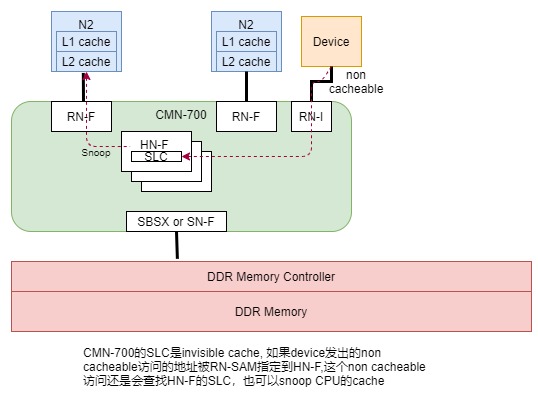

CMN-700的system level cache (SLC)是invisible cache, 如果device发出的non cacheable访问的地址被RN-SAM指定到HN-F,这个non cacheable访问还是会查找HN-F的SLC,也可以snoop CPU的cache。

这是否意味着,这样的系统的PoC点在CMN-700的SLC,而不需要在系统主内存呢?因为DC IVAC/ DC CIVAC只需要将数据失效/清除失效到SLC,不需要失效/清除失效掉SLC中对应的cache line,其他CPU和Device就可以看到同样的copy了。

确实,如果系统中所有可以访问内存的master都接到CMN-700的RN-F,RN-I, RN-D上,并且他们访问的地址是在RN-SAM里面指定到HN-F,PoC只到SLC是可以的。

但是如果系统中有其他不接到CMN-700的master,或者它们访问的地址RN-SAM里面不是指定到HN-F,那么就无法显示PoC要求的:确保系统中所有可以访问内存的agent访问这个地址可以看到同样的copy的地方,不管它的访问内存类型(memory type)和cache属性(cacheable or non cacheable)是什么。

因此,在N2+CMN-700的系统,DC IVAC/ DC CIVAC还是需要失效/清除掉SLC中对应的cache line。

CMN-700支持将这些cache maintanance operation (CMO)下传到内存控制器,如果CMN-700之下还接有其他更低level的cache的话,下传这些CMO可以进一步使CMO PoC的操作影响到更低level的cache。控制是否下传是可以通过编程每个SN-F对应的HF-N寄存器cmn_hns_sam_sn_properties中的cmo_prop_en来实现。

-

如何在Arm Neoverse N2平台上提升llama.cpp扩展性能2026-02-11 298

-

Arm Neoverse N2平台实现DeepSeek-R1满血版部署2025-07-03 1412

-

Arm新Arm Neoverse计算子系统(CSS):Arm Neoverse CSS V3和Arm Neoverse CSS N32024-04-24 3088

-

CMN-700包括哪几种电源管理能力?2023-10-27 1912

-

ARM Neoverse™N2核心技术参考手册2023-08-29 1274

-

Arm Neoverse™ N2核心加密扩展技术参考手册2023-08-17 809

-

ARM Neoverse™N2软件优化指南2023-08-11 588

-

Arm Neoverse N2汽车硬件技术概述2023-08-10 716

-

ARM Neoverse N2 PMU指南2023-08-09 737

-

Arm Neoverse CMN‑700相干网状网络技术参考手册2023-08-08 1675

-

什么是CMN?CMN中的PMU概述2023-03-17 6851

-

Arm Neoverse家族新增V1和N2两大平台,突破高性能计算瓶颈2021-04-30 11189

-

解密Arm Neoverse V1和Neoverse N2平台为下一代基础设施带来计算变革2021-04-28 2383

-

互联网巨头纷纷启用Arm CPU架构,Arm最新Neoverse V1和N2平台加速云服务器芯片自研2020-09-30 1745

全部0条评论

快来发表一下你的评论吧 !