基于PXIE总线的高速CCD数字图像采集系统设计

嵌入式设计应用

描述

为实现高速电容耦合器件(CCD)数字图像采集传输,提出一种基于PXIE总线和Camera Link协议的高速图像采集系统设计方案。设计了Camera Link硬件接口电路,实现了视频数据信号的接口设计、控制信号的接口设计、串行通信信号接口设计;同时采用Xilinx公司的Vir-tex-5 LX50T型FPGA作为PXIE传输控制器,并对IP核进行了开发,减少了外围电路设计难度。创新性地运用直接内存访问的工作方式对PXIE传输速度进行优化。实验结果表明,PXIE配置为8通道时,读取数据速率达到1 504 MB/s,写入速率达到了1 490 MB/s,可以满足高速CCD数据的传输要求。

电容耦合器件(Charge Coupled Device,CCD),是20世纪70年代初发展起来的新型半导体光电成像器件。由于其具有信号输出噪声低、动态范围大、量子效率和电荷转移效率高等特点,加之多年来新型半导体材料技术的不断积累和大规模集成技术的日臻完善,CCD技术目前广泛应用于国民经济、国防建设、科学研究等各个领域。随着上述领域对数字图像的分辨率以及传输速度的要求越来越高,人们对高速图像采集系统的性能、稳定性和可靠性也提出了新的要求。本文提出了一种基于PXIE总线和Camera Link协议的高速CCD图像采集系统设计方案,并详细说明了部分模块的具体实现方式。

1 系统工作原理及总体设计

1.1 Camera Link协议及PXIE协议介绍

(1)Camera Link协议简介

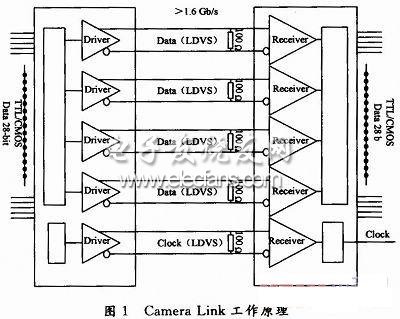

Camera Link是一种基于视频应用发展而来的通信接口。它是NI等13家公司基于Channel Link技术联合推出的一种新型接口,简化了相机与其他设备的连接。Camera Link的驱动端将28位并行数据以7:1方式转化为4组LVDS数据流和1组LVDS时钟信号,串行发送至接收端进行处理。其最高传输速率可达2.38 Gb/s。图1为Camera Link工作原理图。

Camera Link接口协议提供4类信号:相机控制信号、图像数据信号、电源和串行通信信号。其接口有3种结构,分别是初级配置(Base)、中级配置(Medium)和高级配置(Full)。Camera Link使用端口定义来区分这些配置。3M 26-pin MDR(Mini D Ribbon)连接器之所以被选择与Camera Link配套使用是因为它优秀的设计和先前Channel Link高速传输的成功经验。

(2)PXIE协议简介

PXI(PCI Express for Instrumentation)由NI公司于1997年率先提出。PXIE基于Compact PCI标准,增加了时钟和同步触发总线,但其核心仍然是PCI总线。PXI Express相对PXI最显著的改进和优势就在于它融入PCI Express的特点,采用串行传输,点到点的总线拓扑结构。不同于PXI在所有总线设备间分享带宽,PXI Express为每一个设备提供单独的传输通道。同时它所增加的时钟和同步触发信号以及拥有特殊的接口物理特性使得其在测量、通信、工业自动化等领域拥有更大的技术优势。本文采用PXIE-8x,最高传输速度达到1400Mb/s。

1.2 总体设计

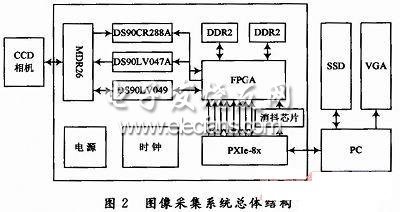

系统总体结构图,如图2所示。

图2中,DS90CR288A为NI公司高性能串并转换器,将Camera Link接口协议的4路LVDS信号和1路LVDS时钟转换为28位LVCMOS/LVTTL数据和一路时钟信号,DS90LV047A为NI公司的3 VLVDS 4路单端转差分驱动器。DS90LV049为NI公司的3V LVDS双向线路驱动器和双向线路接收器。

系统工作流程为:

首先,采集卡通过DS90LV047A对CCD相机发出的控制指令。CCD相机在接到指令后,将采集到的图像数据分为4路LVDS数据信号和1路LVDS时钟信号,通过接口连接器MDR26,输送到图像采集卡;图像采集卡将串行数据转换成38路并行信号和1路随路时钟传送给FPGA进行数据处理。由于数据量很大,为保证数据低误码率及提高可靠性,使用了2块Micron 2 GB DDR2对数据进行缓存和乒乓处理。FPGA根据用户的需求进行高速的图像处理。采集卡通过PXIE-8x将图像数据上传至PC(上位机)上进行后期处理,同时实现PC(上位机)对图像采集卡的控制。图像数据最终通过PC将数据存储在SSD(Solid-state Drive)电子盘上,以供随时调用。在读/写速度等关键性能上,SSD电子盘远远优于传统机械硬盘,因此选用SSD电子盘为数据存储介质。采集卡还采用DS90LV049(LVDS双线路驱动器,带有双线路接收器)来实现采集卡与相机间的串行通信,用户可以根据需要对CCD相机进行配置。

2 关键模块设计

2.1 Camera Link接口设计

根据系统功能要求,Camera Link接口设计包括3个部分,即为视频数据信号接口设计,控制信号接口设计,串行通信命令接口设计。

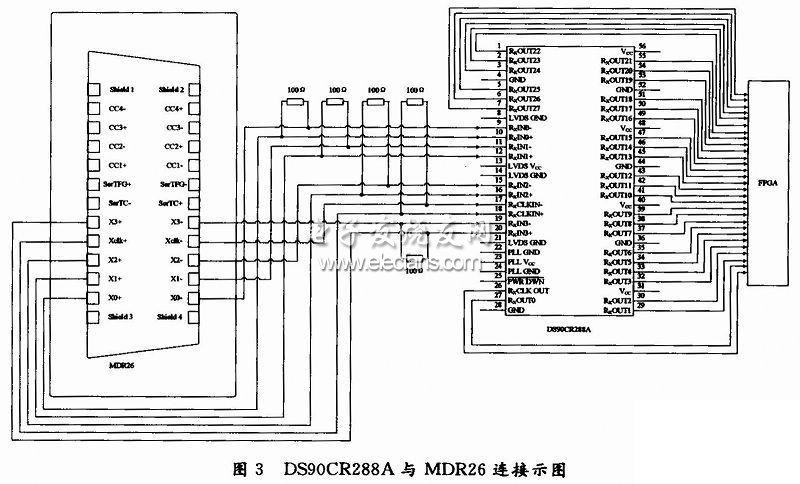

2.1.1 视频数据信号的接口设计

视频数据信号为FVAI,LVAL,DVAL和SP,它们分别是帧允许信号、行允许信号、数据允许信号和保留信号,4路均为LVDS数据信号,外加1对LVDS时钟信号,在此采用了National Semiconductor公司的DS90CR288A芯片,将5路LVDS信号转换为28路数据信号。具体连接图如图3所示。

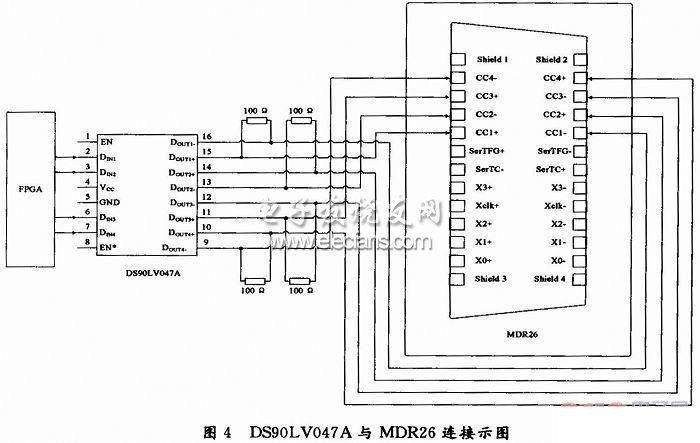

2.1.2 控制信号接口设计

相机控制信号CC1,CC2,CC3,CC4为4路LVDS信号,为节省布线空间,FPGA发出的控制信号均为单端信号,因此采用National Semicon-ductor公司的DS90LV047A芯片将采集卡发出的单端COMS控制信号转化为LVDS信号,完成对CCD相机的控制。图4为DS90LV047A与MDR26的连接。

2.1.3 串行通信信号接口设计

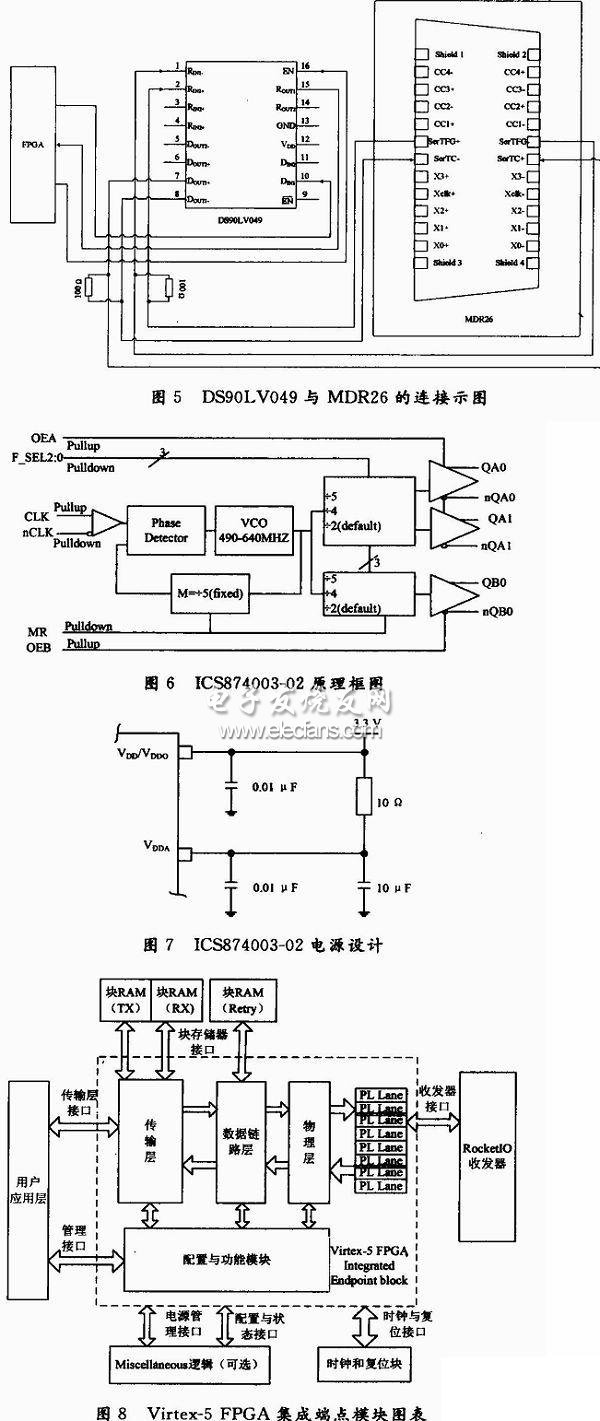

串行通信信号由两对LVDS信号提供,这些信号使相机与其使用者之间可以进行通信。因为是双向通信,在此采用了National Semicon-ductor公司的DS90LV049芯片实现了LVDS差分信号到单端CMOS信号的双向转换。图5为DS90LV049与MDR26的连接示图。图中EN为1时,EN可以不接,4条通路可以全通。

2.2 PXIE模块设计

2.2.1 PXIE的时钟电路设计

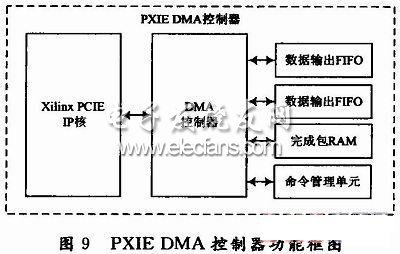

在PXIE规范中,对于时钟的频率稳定度要求是100 MHz±300 ppm,抖动(Cycle-to-Cycle)需要小于125 ps,占空比要求50%±5%以内。因此,系统中选用IDT公司的ICS874003-02作为100 MHz参考时钟的抖动衰减器。ICS874003-02是一款高性能的将差分时钟转换为LVDS电平时钟信号的时钟抖动衰减器,该元件可支持PXI Express系统,具有衰减或“清除”100 MHz PXIE输入时钟抖动,同时将其转换成250 MHz LVDS输出能力的时钟器件。ICS874003-02在芯片内部集成了一个高性能,低相噪的锁相环。锁相环的鉴相带宽为400 kHz,可以快速锁定时钟,减小抖动。该器件支持低于1 ps RMS极低相位噪声的基准时钟生成,满足基于PXIE的高速应用的严格的抖动要求。它的最大周期抖动为35 ps,占空比变化为50%±2%,完全可以满足PXIE对时钟的要求,其内部原理图如图6所示。

该系统设计中采用QA0/nQA0和QA1/nQA1两对差分输出时钟,并且将这两个输出分频器的分频系数设置为5,使输出时钟频率和输入时钟频率相同。

ICS874003-02提供独立的电源用以隔离内部锁相环产生的开关噪声,VDD,VDDA,以及VDDO抑必须单独通过过孔连接到电源层,并且在每个电源脚上都要加入旁路电容,为了获得最佳的时钟抖动特性,电源需要相互隔离。如图7所示,1个10 Ω的电阻以及1个10 μF和0.01 μF的旁路电容构成了一个电源滤波电路,连接到每个VDDA脚,10 Ω的电阻可以被磁珠所替代。

2.2.2 PXIE的IP core设计

该系统中,采用Virtex-5LX50T型FPGA作为PXIE的传输控制器,由于FPGA内部集成了PCIe端点模块,所以减少了很多外围硬件电路的设计难度。PCIe端点模块的IP核框图如图8所示。

由图8可以看出,PXIE IP核采用分层结构,即分别为物理层链路模块、物理层、数据链路层、传输层和用户应用层。传输层负责处理用户应用层(User Applieation)提供的传输层包(TLP)并安排其传输。数据链路层负责链路管理和数据完整性,包括错误的检测和纠正。物理层负责完成包的成帧和解帧、字节的组合和拆分、链路的初始化和训练、扰码生成和解扰。发送时,物理层链路模块负责将物理层生成的扰码应用到传输数据中,同时复用到物理层模块接收到的有序集中,最后把包传输给传输接口;接收时,负责从传输接口上接收TLP字节,从数据中解码有序集,并且将DLLP和TLP解扰。

2.2.3 PXIE传输速度问题及解决情况

由于PXIE传输协议是基于PCIe传输协议的扩展,所以可以利用目前比较成熟的PCIe传输协议实现技术在硬件程序设计层次上实现PXIE传输协议,至于PXIE协议的一些扩展接口,都可以在FPGA外围用基本硬件电路简易的实现。FPGA生产厂商Xilinx公司提供了一套成熟,稳定并且免费的PCIe传输方案,以IP(Intellectual Property)的形式提供给用户。

PCIe IP核虽然为PXIE传输协议提供了解决方案,但是仍然存在问题。首先,在实际测试过程当中,由于PCIe IP一直占用了CPU,使得PC在进行数据传输时,主机本身无法进行其他操作,还有一定几率造成系统崩溃。其次,由于PCIe协议进行传输的包载荷过小,在进行大数据量传输的时候,会进行多次传输,从而浪费大量时间在结束和发起传输上,导致平均数据传输率下降。最后,由于IP核的重要特性是通用化,所以IP核的接口包括了所有PCIe信号,使得用户操作非常繁琐,不利于设计的移交和修改。直接内存访问(Direct Memory Access,DMA)控制器能够从根本上解决前两个问题,经过优化设计也能改善第三个问题。

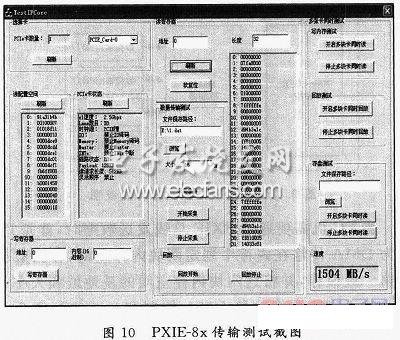

PXIE总线DMA的FPGA功能设计框图如图9所示。

当PC机需要通过PXIE总线发送数据时,首先PC机为DMA传输在内存中划定两块内存空间,作为数据的第一级缓存,并将这两块内存空间的基地址和大小轮流通过PXIE总线传给DMA控制器。这些配置命令通过特定的字符串被识别,并写入相应的配置命令寄存器。划定两块内存空间是为了在当DMA控制器从一块内存中读取数据时,PC机可以向另一块内存写入数据,以乒乓操作的形式提高传输效率。

接下来,PC机发起对数据的传输。PC机上的PCIe控制器从内存中取得数据后,将原始数据封装,并串转换往下继续传输,数据包通过吉比特串行收发器传至FPGA,在进入PCIe IP核后被拆解,剥离的纠错信息作为包进一步处理的依据,最后在应用层以并行数据的形式推入DMA控制器。

DMA控制器将数据流存人数据输出FIFO,根据FIFO剩余空间的大小判定是否从PC机中继续读取数据,这样就保证了数据不会因为来不及从FIFO中取走而丢失。当DMA控制器接收到一块内存大小的数据之后,就会以边带信号的形式发送中断信号给上位机,上位机接收到中断之后就可以开始下1次DMA传输。

当PC机需要通过PXIE总线接收数据时,工作流程与通过PXIE总线发送数据基本类似,主要区别在于从PC机往下发送的包里不包含数据,仅包含路由及其他控制信息,DMA控制器接收到包后,会以完成包的形式将数据打包往上传回PC机,完成包按照接收到包中的路由信息,逆向寻址回到PC机的内存,PC机就完成了一次通过PXIE总线接收数据。

加入DMA控制器之后的PXIE总线被重新封装,操作得到简化。

2.3 测试结果

在测试中,PXIE配置为8通道,测试数据为16 MB,在PC机通过PXIE接口读取数据的操作过程当中,平均数据率达到1 504 Mb/s。在PC机通过PXIE接口发送数据的操作过程中,平均数据率达到1 490 Mb/s。通过PCIe测速软件进行传输速度测试,其结果如图10所示。

3 结语

本文介绍了一种基于PXIE总线和Camera Link协议的高速CCD图像采集系统的设计方案。该方案给出了一种Camera Link硬件接口电路的设计思路,并且选用Xilinx公司的Virtex-5 LX50T型FPGA作为整个采集系统的核心处理器,同时对Virtex-5自带的IPcore进行研究和开发,实现Camera Link采集卡通过PXIE总线与上位机进行串行通信。在试验过程中,FPGA设计灵活,开发周期短的优点充分得以体现,为下一步的高速图像采集系统的研制奠定了基础。

-

请问有适用嵌入式系统的数字图像采集模块设计方案吗?2021-04-08 1857

-

凌华科技推出机器视觉应用的高速数字图像采集卡,适用于PCB检测等2020-08-30 2491

-

使用GigE接口实现嵌入式并行多路数字图像采集系统的技术详细概述2019-11-22 1475

-

基于FPGA和MV-D1024E相机的图像采集系统该怎么设计?2019-10-31 1572

-

基于采用FPGA控制MV-D1024E系列相机的图像采集系统设计2019-07-02 2808

-

基于DVI接口的高速图像总线控制系统2019-06-10 2478

-

CCD高速数字图像多路光纤传输系统研究_李强2017-03-19 987

-

基于FPGA的新型高速CCD图像数据采集系统2016-09-22 690

-

基于DSP和FPGA的CCD图像采集系统设计与实现2014-11-07 4041

-

基于FPGA的B超数字图像实时采集系统2012-08-17 2795

-

基于USB的高清彩色CCD图像采集系统2012-03-22 967

-

基于PCI总线和DSP的实时图像采集与处理系统2011-02-25 761

-

数字图像的实时采集原理2009-03-29 1987

-

凌华科技推出适用于机器视觉应用的高速数字图像采集卡(采用PC2008-08-12 1343

全部0条评论

快来发表一下你的评论吧 !