HFTA-16.0:双极型集成电路的ESD保护

描述

众所周知,静电放电(ESD)会对集成电路(IC)造成破坏性的能量冲击,许多设计功能会影响到器件的ESD性能。本应用笔记讨论了几种保护IC免遭ESD破坏的电路设计方案。

概述

静电放电(ESD)会对集成电路(IC)造成破坏性的能量冲击,良好的IC设计能够在IC装配到应用电路的过程中保护IC免遭ESD冲击的破坏。安装后,IC还必须能够承受ESD穿过静电防护电路进入最终电路的冲击。除此之外,机械防护、电源去耦电容都有助于提高ESD保护能力,但是,如果电容选择不当将会造成IC更容易损坏。为了给IC提供合理的ESD保护,需要考虑以下内容。

冲击IC的ESD传递模式

内部ESD保护

应用电路与IC内部ESD保护的相互配合

修改应用电路提高IC的ESD保护能力

ESD传递模式

静电放电强度以电压形式表示,该电压由电容的储能电荷产生,最终传递到IC。作用到IC的电压和电流强度与IC和ESD源之间的阻抗有关。对电荷来源进行评估后建立了ESD测试模型。

ESD测试中一般使用两种充电模式(图1),人体模式(HBM)下将电荷储存在人体内(100pF等效电容),通过人体皮肤放电(1.5kΩ等效电阻)。机器模式(MM)下将电荷储存在金属物体,机器模式中的放电只受内部连接电感的限制。

图1. ESD测试模型

以下概念对于评估ESD向IC的传递非常有用:

电压高于标称电源电压时,IC阻抗较低。

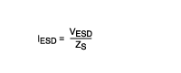

对于图1中的HBM模式:ZS = ZHBM = 1.5kΩ

在MM模式下,电流受特征阻抗(约50Ω)的限制。

上述特征阻抗的计算可以从低阻L-C电路的能量(E)推导出来:

如果ESD电流主要流入电源去耦电容,IC电压由储存的电荷量决定:

Q = C x V和QFinal = QInitial

V1 x (C0 + C1) = VESD x C0 (见图1)

能够在瞬间导致IC损坏的能量相当于微焦级,有外部电源去耦电容时,考虑这一点非常重要,图1中从电源电容(C1)传递到IC的能量是:

耗散功率(P)会产生一定热量,假设能量经过一段较长的时间(t)释放掉,热量将随之降低:

ESD能量传递到低阻电路时需要考虑其电流(上述第1、2条);对于高阻而言,能量以电压形式通过电荷转移传递到电源去耦电容和寄生电容(第3条)。对IC造成损坏的典型能量是在不到一个毫秒的时间内将微焦级能量释放到IC (第4、5条)。

IC内部保护电路

标准保护方案是限制到达IC核心电路的电压和电流。图1所示保护器件包括:

ESD二极管—在信号引脚与电源或地之间提供一个低阻通道,与极性有关。

电源箝位—连接在电源之间,正常供电条件下不汲取电流,出现ESD冲击时呈低阻。

ESD二极管

如果对IC引脚进行HBM测试,测试电路的初始电压是2kV,通过ESD二极管的电流约为1.33A (图2):

图2. ESD二极管的电流和电压(测量数据)

理论上,进行HBM测试时引脚电压受限于二极管压降。大电流会在ESD二极管和引线上产生I-R压降,在信号引脚产生额外的电压,如图2所示。

为了确定IC是否能够承受2kV的ESD冲击,需要参考厂商提供的资料。IC的额定电压由最大电压决定,图1中的VESD,这是IC能够承受的一种特定的ESD源。Maxim IC所能承受的ESD指标在可靠性报告中可以查找到。

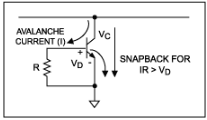

电源箝位

双极型IC的箝位电路类似于在受保护核电路中提供一个受冲击时击穿的部件,图3给出了图1中箝位功能的详细电路。箝位晶体管的过压导致集电极-基极之间的雪崩电流,发射结的正向偏置会进一步提高集电极电流,导致一个“突变”过程。箝位时的V-I特性曲线如图4所示。

图3. 图1中的箝位电路

图4. V-I箝位特性

箝位二极管在IC其它电路遭到破坏之前导通,箝位管要有足够的承受力,保证ESD电流不会导致二次击穿。2kV HBM测试的箝位过程如图5所示,图5中的电压包括I-R压降和突变稳定后的箝位电压。

图5. 箝位工作过程(测量数据)

ESD保护与应用电路

箝位电压从第一次击穿变化到突变稳定后的导通电压,如图5所示。为保证箝位时关闭正常的工作条件,设计的箝位电压一般要略高于IC的绝对最大电压。

电源去耦电容会影响箝位操作,传递到去耦电容的电荷会产生高于IC绝对最大值的电压,但还不足以使箝位电路导通。这时的电容相当于一个能源,迅速向器件注入能量。

对于一个给定的去耦电容,ESD测试中初始电压的变化遵循电荷守恒原理。例如,使用一个0.01µF去耦电容,2kV HBM测试电压可以达到20V:

或

图6. 能量和电压与电源耦合电容的关系

被保护引脚电容上的能量如图6所示,对小的去耦电容,箝位二极管通过进入突变稳定模式限制电压(V1)。突变稳定后的电压所产生的能量近似地随着电容的增大而成比例增大。电源去耦电容增大到一定程度后,电荷传输不会产生导致箝位电路击穿的电压。

箝位电压高于IC所能承受的电压(典型值6V),低于二极管的击穿电压(约10V)时,对于存在去耦电容的情况,因为电容储能可能导致某些问题。如果IC在没有外部电路的情况下进行测试,引脚上作用10V电压是可以接受的,对器件不会构成威胁。

改善ESD保护

合理选择去耦电容的大小有助于在电路中提高IC的保护,降低电容储能,使ESD电荷不会产生击穿箝位电路的电压。我们可以考虑图1中C1>>C0的情况:

最初:

将C1加倍,则会导致:

电容加倍,能量降低一倍。

对于小尺寸高速双极型IC,HBM测试中吸收的最大能量是1µJ;2kV人体模式下,如果电容小于0.02µF (图6), 箝位二极管会产生动作。为了使去耦电容的能量低于1µJ,去耦电容有两种选择:要么容值大于0.05µF,要么小于0.005µF。当使用更高的测试电压时,要按比例增大0.05µF电容的尺寸。

实际应用中,通常不允许使用更大的去耦电容。浪涌电流的要求会限制电容尺寸。如果不控制电压摆率,唯一限制浪涌电流的途径就是限制去耦电容的尺寸:

去耦电容与电源间的引线总是存在一定量的电感,通常也会接入一个滤波电感。这种配置下,最大浪涌电流取决于滤波电感与去耦电容的特征阻抗,这个阻抗(图7中的Zo)类似于MM测试中的电流限制。

图7. C1较大时的电源阻抗

通过限制浪涌电流,可以使用较大的滤波电容(C1);发生ESD冲击时,使得作用在IC上的电压低于器件允许的最大额定电压。

改善ESD保护的有效途径有:

使用更大的滤波电容,使最大ESD电压低于IC引脚所能承受的绝对最大电压。

使用小的滤波电容,使得箝位二极管在低能量时提供保护。

增大串联电感限制大电容产生的浪涌电流。

增加外部箝位二极管,如图8所示的齐纳二极管,使ESD电压低于器件所能承受的绝对最大电压(图9)。

图8. 齐纳ESD保护二极管

图9. 利用齐纳保护二极管改善箝位(测量数据)

结论

IC及其周边元件需要承受突破应用电路镜电防护层的ESD能量,电源的去耦电容可能是降低作用到IC上的ESD强度的一条低成本解决途径,诸多设计因素会影响ESD性能,具体可以归纳为:

确定应用场合的测试电压(VESD),典型值为2kV的HBM或100V MM模式。

检查IC的可靠性报告,确认二极管、钳位二极管和传导路径适合的测试电压。Maxim的可靠性报告中提供了IC的相关信息。

当使用外部电容,如电源滤波电容(C1)时,需检查其产生的电压,这个电压最终作用到IC上。

如果出现ESD冲击时,电压介于IC的最大额定电压(典型值为6V)与击穿电压(典型值在8V至10V),可以考虑使用较大尺寸的电容来替代电源滤波的方案。

审核编辑:郭婷

-

集成电路继电保护(基本电路,距离保护,高频保护,发电机失磁保护,接地保护)2008-08-14 6947

-

新型互补电容耦合ESD保护电路的设计2009-12-23 10520

-

双极型集成电路的特点有哪些?2017-01-10 4728

-

集成电路电源芯片的分类及发展2018-10-18 4774

-

如何设计ESD保护电路?2019-08-07 5232

-

在I/O电路中ESD保护结构的设计要求2021-04-02 4248

-

如何进行双极型集成电路的ESD保护?2021-04-07 2374

-

如何设计MOS集成电路ESD保护模块?2021-04-12 2206

-

双极型集成电路的ESD保护2009-04-27 617

-

什么是双极型集成电路2009-06-30 5090

-

集成电路分为哪几类 集成电路分类介绍2021-10-03 19123

-

集成电路分类有哪些2022-02-01 9254

-

影响 ESD 保护要求的集成电路趋势2022-11-14 565

-

HFTA-16.0:双极集成电路的 ESD 保护2022-11-18 276

-

集成电路电磁兼容性及应对措施相关分析(三)—集成电路ESD 测试与分析2024-12-20 1393

全部0条评论

快来发表一下你的评论吧 !