求一种基于LVDS和SERDES接口的TDM方案

接口/总线/驱动

描述

通过在数据的并行发送路径上同时传输时钟信号来进一步改进数据的传输。这种一起发送时钟和数据的方法称为源同步接口。由于时钟具有与数据相同的片外/片上偏斜,所以更容易满足时序要求,特别是如果使用硬件设计质量良好的FPGA电路板,其上具有相同传输时间的匹配延迟轨迹。

让时钟从源传输,而不是在本地生成并保持同步,通常不适用于驱动分割的SoC功能逻辑,但对于单向串行数据传输非常有用。

片间的传输时间非常重要,它仍然是多片FPGA系统速度最大的物理限制,克服这一问题的方法是在FPGA之间使用差分信号。使用FPGA对LVDS的内置支持,可以将传输速率提高到1GHz。这允许更高的复用率,而不必降低原型总体的时钟速度。

另外,现代FPGA具有专用的串行到并行转换器SERDES接口,该转换器具有特定的时钟和逻辑功能,可实现高速串行传输。使用SERDES口避免了在FPGA结构中实现类似功能的时序和布局复杂性。还可以使用FPGA内置的SERDES块双倍数据速率(DDR)操作支持,通过使用传输时钟的两个边缘,将传输数据速率加倍。

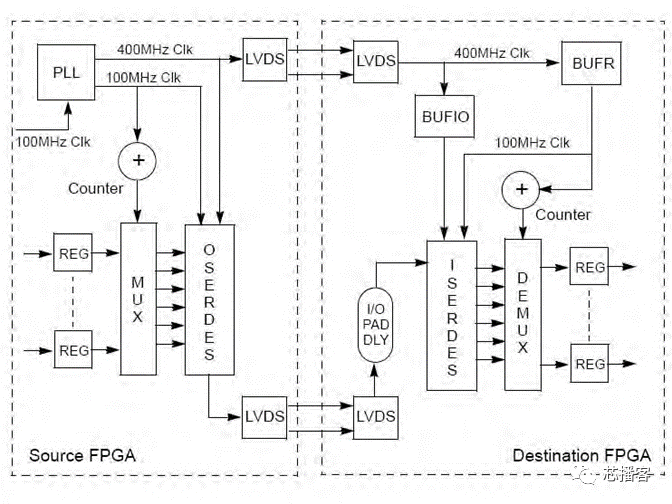

保证了板载的最高传输速度,但稍有缺点的是每个串行数据流需要两个引脚。因此,虽然比率为8:1的单端复用方案只需要一个FPGA间迹线来传输八个数据信号,但差分IO标准需要两个,因此我们称之为8:2的多路复用器比率。因此,差分解仅将互连减少了四倍,而不是八倍。然而,当考虑到LVDS的显著更高速度时,可以考虑128:2的复用率,这提供了比单端方案可能的更大的数据传输带宽,如图所示,该SERDES传输以400MHz的传输速率运行。

并且需要两个时钟用于操作。时钟由源FPGA内的PLL基于来自外部源的100MHz时钟生成。OSERDES配置为8:1的比率,但由于它在DDR模式下运行,我们只需要400MHz而不是800MHz的传输时钟。这意味着400MHz时钟在一个100MHz周期内传输8位。为了提供高于8的复用率,我们可以在OSERDES的输入端使用额外的多路复用器,但这只需要在较慢的内部时钟速率下工作。

数据和传输时钟都通过LVDS信令传递到目的地FPGA,但在目的地FPGA处。然后,数据和传输时钟驱动ISERDES块。接收到的时钟通过BUFR块将其除以4,以创建100MHz的本地版本,这也是ISERDES和dmux控制所需的。该图仅给出了概述,并且实现可能更复杂,实现的方式将取决于原型验证系统供应商提供的方案。

审核编辑:刘清

-

工业系统中LVDS SerDes的设计与应用2024-09-26 399

-

LVDS-SERDES发射机SN65LVDS95LVDS数据表2024-06-26 497

-

SerDes的技术原理 SerDes的重要概念和技术概述2023-11-14 19941

-

如果不使用FPGA自带的SERDES,可否适用LVDS接口实现其功能?2023-05-08 4115

-

介绍一种采用光SerDes而非电SerDes的高速收发器2023-04-01 4545

-

一种高速串行视频接口TIDA-00137参考设计2022-09-19 1653

-

求一种低成本高速USB接口的设计方案2021-05-10 1989

-

求一种PCIe接口的视频采集解决方案2021-04-30 1402

-

求一种基于LVDS接口的PCM解码板设计方案2021-04-20 1413

-

求一种因光纤漂移引起SERDES FIFO溢出的解决方案2021-04-19 2185

-

使用SERDES(LVDS)作为背板怎么实现?2020-07-13 3044

-

一种基于TDM的工业串行实时通讯协议2012-08-06 1918

-

SN65LVDS93,pdf(LVDS Serdes Tra2010-09-09 1321

全部0条评论

快来发表一下你的评论吧 !