RC Corner基础知识详细讲解

电子说

描述

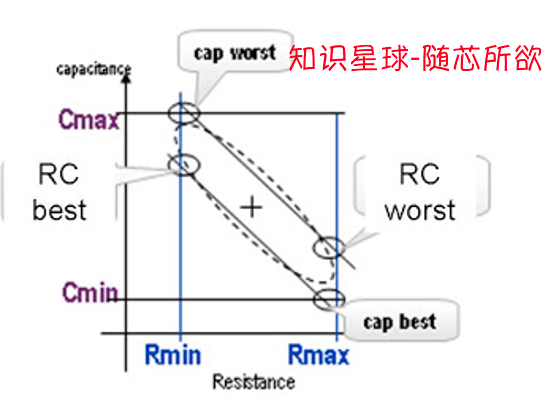

90nm 更早的工艺,通常都只有两个RC Corner: Cworst = Cmax, Rmin;

Cbest =Cmin, Rmax 电容电阻特性分别占主导。

90nm后更新的工艺,考虑到互连线coupling的影响,出现了RCworst, RCbest corner. RCbest(也被称为XTALK Corner)= Cc max(此时耦合电容最大),Cg x R min RCworst(也被称为Delay Corner)= Cg x R max(此时RC的乘积最大), Cc min Cc是耦合电容,Cg是对地电容

因此加起来就有4个RC Corner,

Cbest, Cworst, RCbest,

C-best:

•它具有最小的电容,所以也被称为Cmin Corner;

•互连电阻大于Typical Corner;

•此Corner导致那些nets都非常短的路径的延迟非常小,可用于hold分析。

C-worst:

•具有最大的电容,所以也被称为Cmax Corner;

•互连电阻小于Typical Corner;

•此Corner导致那些nets都非常短的路径的延迟非常大,可用于setup分析。

RC-best:

•指最小化互连RC乘积的Corner,所以也被称为RC-min Corner; •通常对应于较小的蚀刻,这增加了Trace(实际走线)的宽度。这导致最小的电阻,但其电容值要大于Typical Corner; •对于具有长互连的路径,该Corner具有最小的路径延迟,可用于hold分析。

RC-worst:

•指最大化互连RC乘积的Corner,所以也称为RC-max Corner;

•通常对应于较大的蚀刻,这会减少Trace(实际走线)的宽度,这导致最大的电阻,但其电容值要小于Typical Corner;

•对于具有长互连的路径,该Corner具有最大的路径延迟,可用于setup分析。

Typical:

•典型值,这是指互连电阻和电容的标称值。

总结: 所以你可能已经注意到有两种类型的寄生:一种是基于C的,另一种是基于RC的。 在基于C的里面,C意味着最差和最佳情况的电容C;

但在基于RC的里面,RC意味着最差和最佳情况的电阻R,同时调整C为最差或最佳。

根据经验,发现基于C的提取比基于RC的提取为内部时序路径提供了更差和最好的情况,因为电容主导了短线。

然而,对于大型设计,由于R在长导线中占优势,因此Block之间的时序路径(inter-block timing path通常)最差,RC寄生效应最差。

注意:没有Corner能保证任意晶体管驱动任意导线拓扑的最小或最大延迟 借助下面的图片,很容易理解该内容:

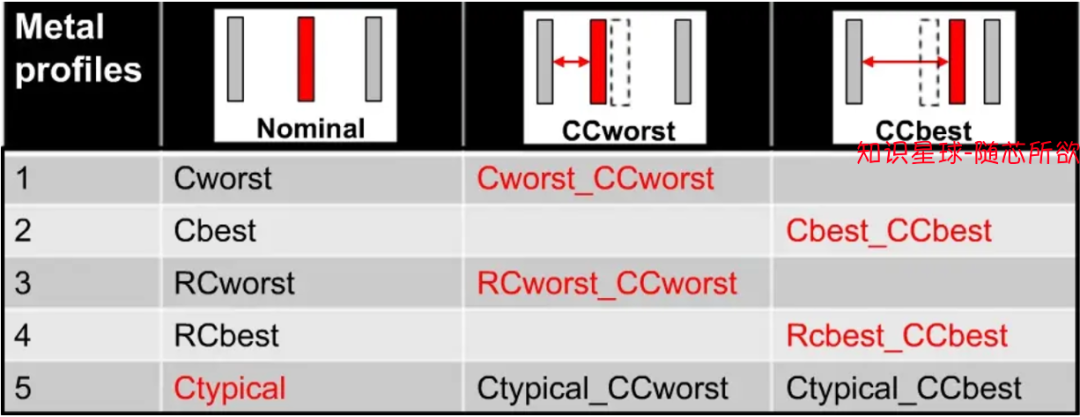

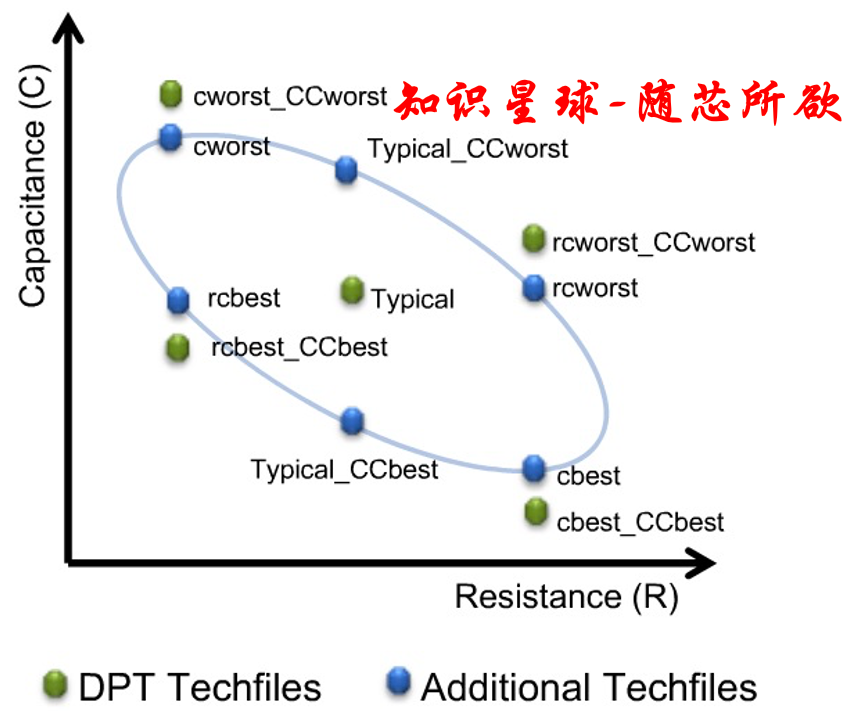

在先进工艺的下,会引入Double Pattern,考虑到不同Mask之间的misalign,因此会增加额外的CCworst和CCbest Corner。引入Double Pattern之后的Corner如下:

它们之间的RC关系如下:

审核编辑:刘清

-

超详细的射频基础知识2022-11-04 3457

-

电路基础知识讲解 电路基本元件知识与电路元件的伏安特性和功率特性2023-07-31 6251

-

智能手机基础知识讲解2012-08-15 50168

-

C++语言基础知识讲解2016-01-14 853

-

C51语言的基础知识点实例讲解2019-06-04 1683

-

PIC16C5X基础知识讲解2021-04-07 995

-

C语言基础知识讲解2021-05-19 1426

-

EMC的原理基础知识讲解2021-05-28 1464

-

华为防雷接地基础知识讲解2021-06-03 1245

-

单片机基础知识讲解PPT课件下载2021-07-29 2735

-

嵌入式系统基础知识讲解2021-07-30 1102

-

Oracle数据库基础知识讲解2021-09-28 1074

-

量子力学基础知识讲解2022-03-07 986

-

CAN总线的基础知识详细讲解2022-04-02 1292

-

芯片后端signoff的RC corner指什么?2023-12-05 3620

全部0条评论

快来发表一下你的评论吧 !