将RTL模块添加到Block Design的步骤

描述

绪论

使用Vivado Block Design设计解决了项目继承性问题,但是还有个问题,不知道大家有没有遇到,就是新设计的自定义 RTL 文件无法快速的添加到Block Design中,一种方式是通过自定义IP,但是一旦设计的文件有问题就需要重新修改,同时需要控制接口时候还需要在AXI总线模板基础上进行修改,再同时繁琐的步骤也让人“望而却步”。下面介绍一种简单的方式。

我目前使用的是 Vivado 2019.1、2020.2,但据我所知,此功能几乎适用于 Vivado 的所有版本(如果不正确,请随时在后台更正)。

创建 Vivado 项目

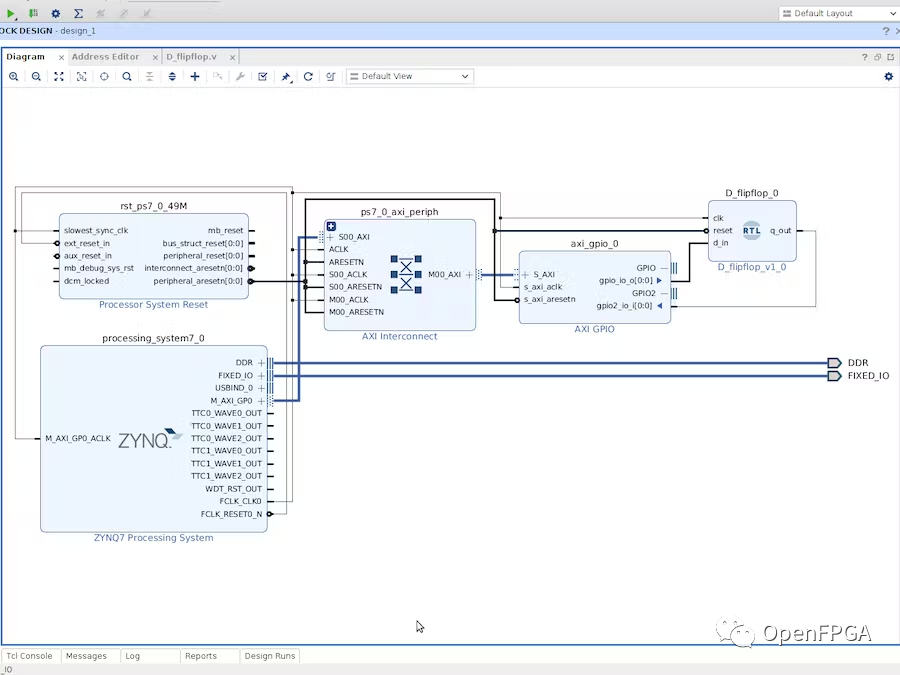

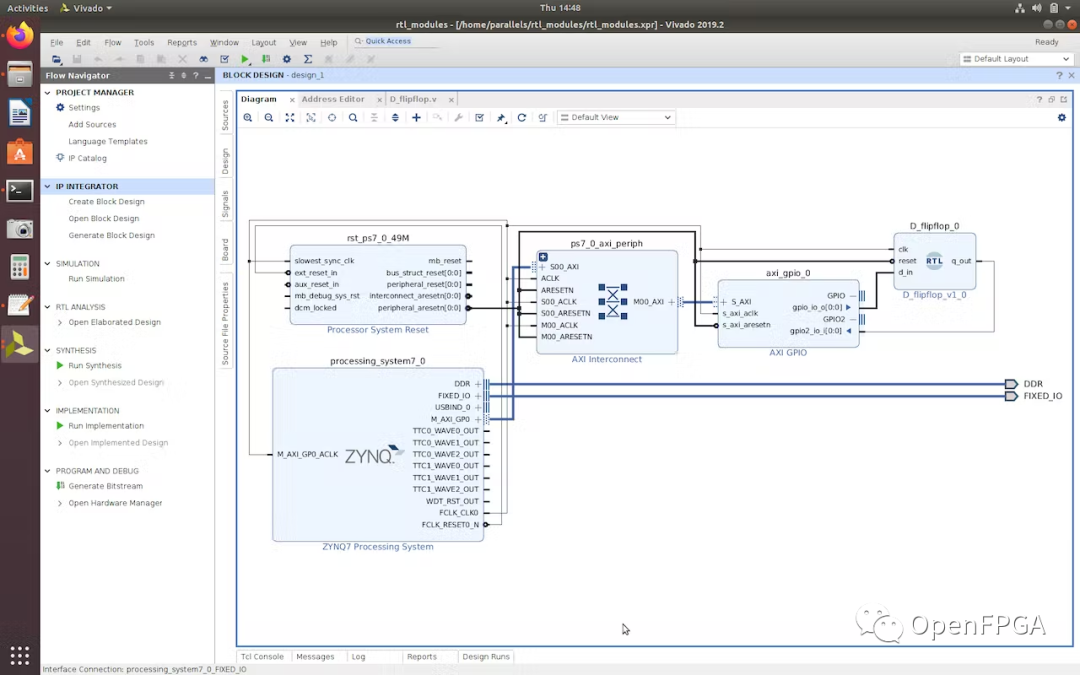

为了开始这个例子,我创建了一个基于 Zynq 的新 Vivado 项目(这只是我的例子,但这个项目的内容并不特定于任何特定的 FPGA 开发板),同时这个项目中包括一个通过AXI-Lite控制的自定义RTL。

添加设计文件并编写自定义 RTL

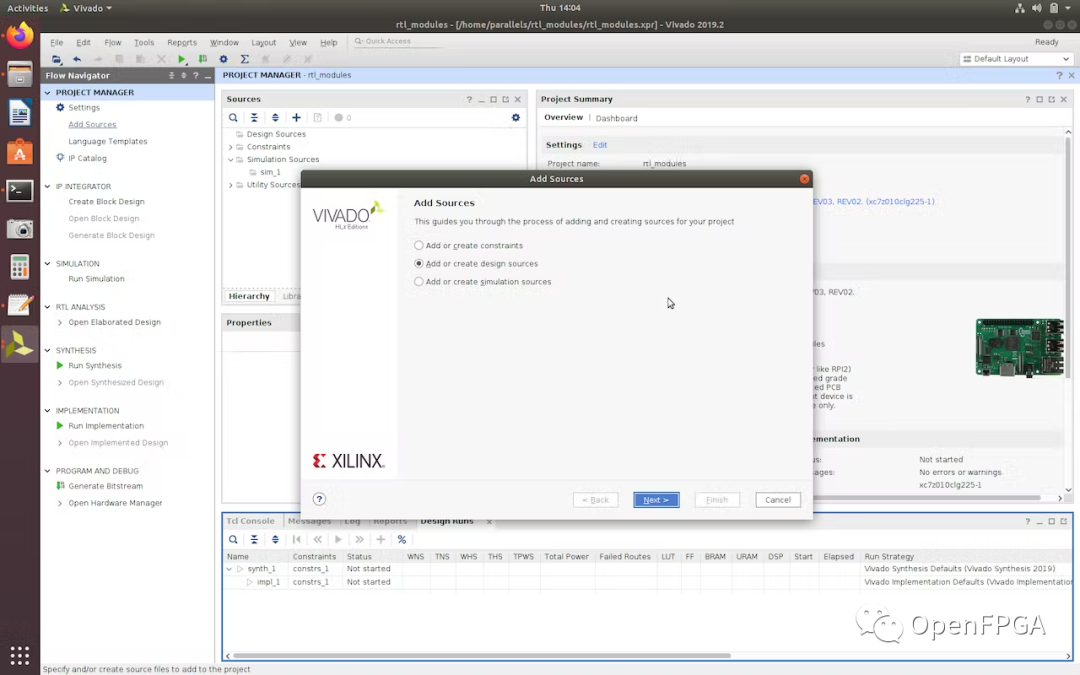

不用于仿真目的的自定义 RTL(即测试文件)都被视为 Vivado 中的设计源。使用 Flow Navigator 中的Add Sources选项并选择Add or create design sources ,然后单击 Next。

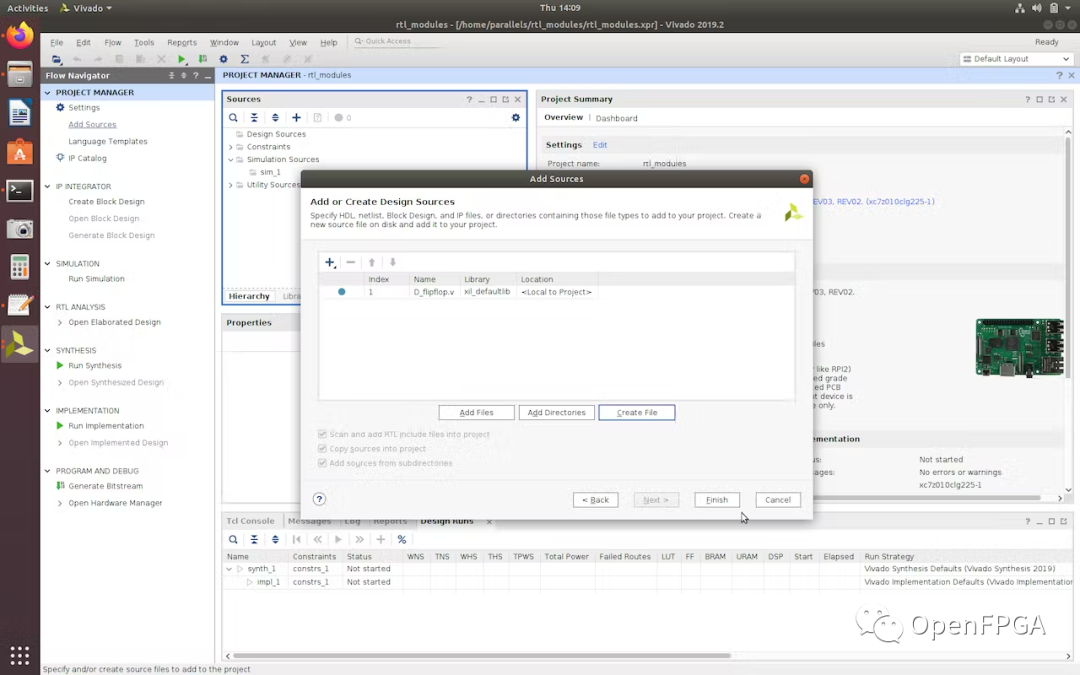

我们创建一个名为D_flipflop的新文件并添加了以下逻辑:

module D_flipflop( input clk, input reset, input d_in, output reg q_out ); always @ (posedge clk) begin if (reset == 1'b1) begin q_out <= 1'b0; end else begin q_out <= d_in; end end endmodule

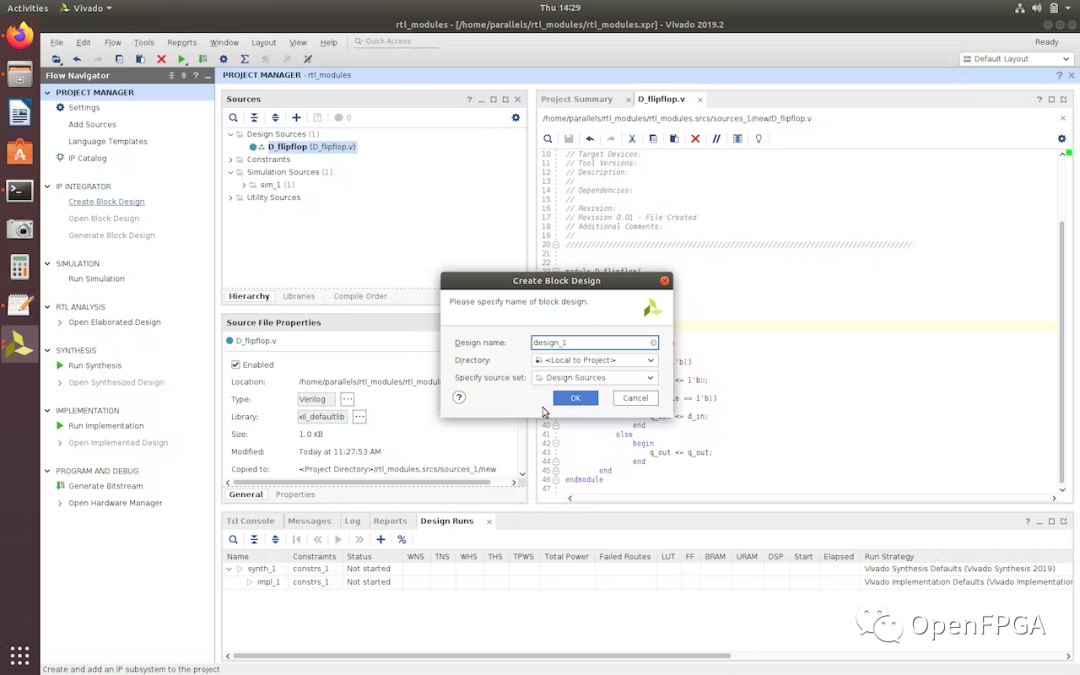

创建Block Design

使用 Flow Navigator 窗口中的Create Block Design选项,将新的Block Design添加到项目中。

将 Zynq 处理系统 IP 块添加到设计中,并运行自动设置或者自动连线。

将 RTL 模块添加到Block Design

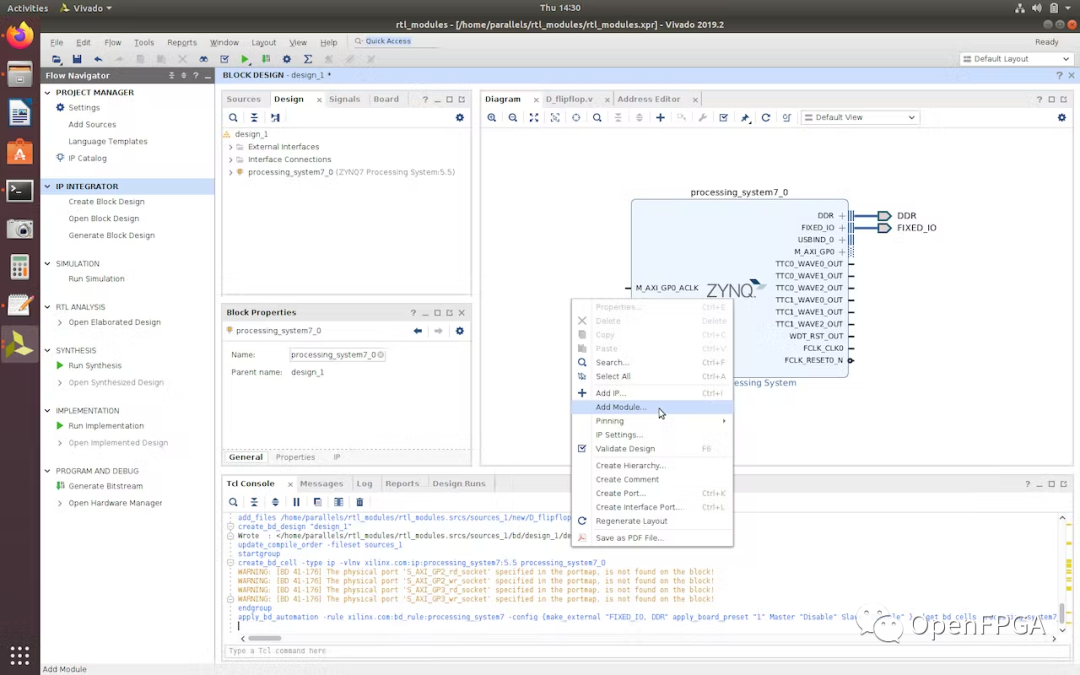

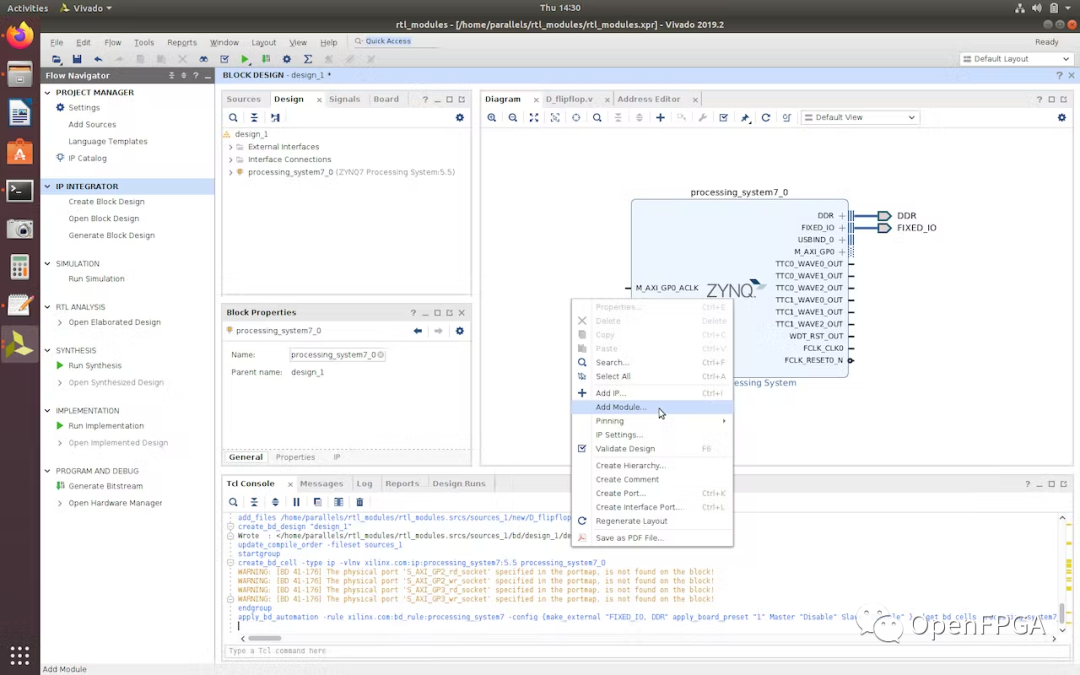

要添加我们在上一步中创建的 D 触发器的 RTL 模块,右键单击 Diagram 窗口空白处的任意位置,然后选择Add Module...选项。

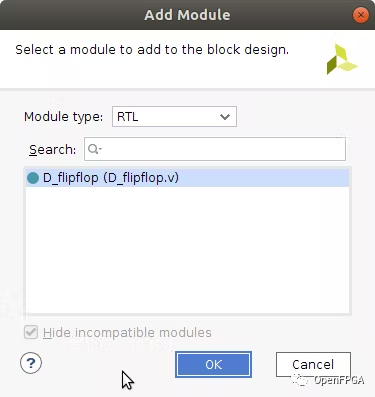

Vivado 将自动显示它在当前项目中找到的所有有效 RTL 模块。由于写入或导入到当前项目中的模块是我们刚刚设计的 D 触发器,因此它是本例中的唯一选项。

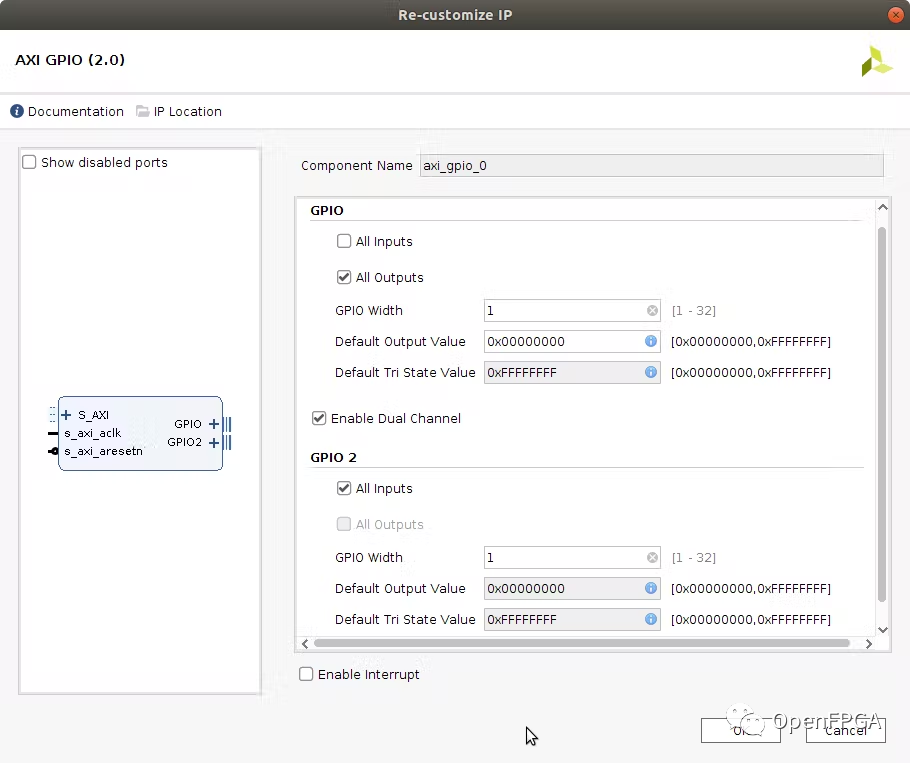

为了给触发器提供源,我添加了一个 AXI GPIO IP ,其中第一个通道作为输出,第二个通道作为输入。自动连接即可。

为 AXI GPIO 模块运行自动连接后,将输出 GPIO 通道连接到触发器的 d_in,将触发器的 q_out 连接到输入 GPIO 通道。

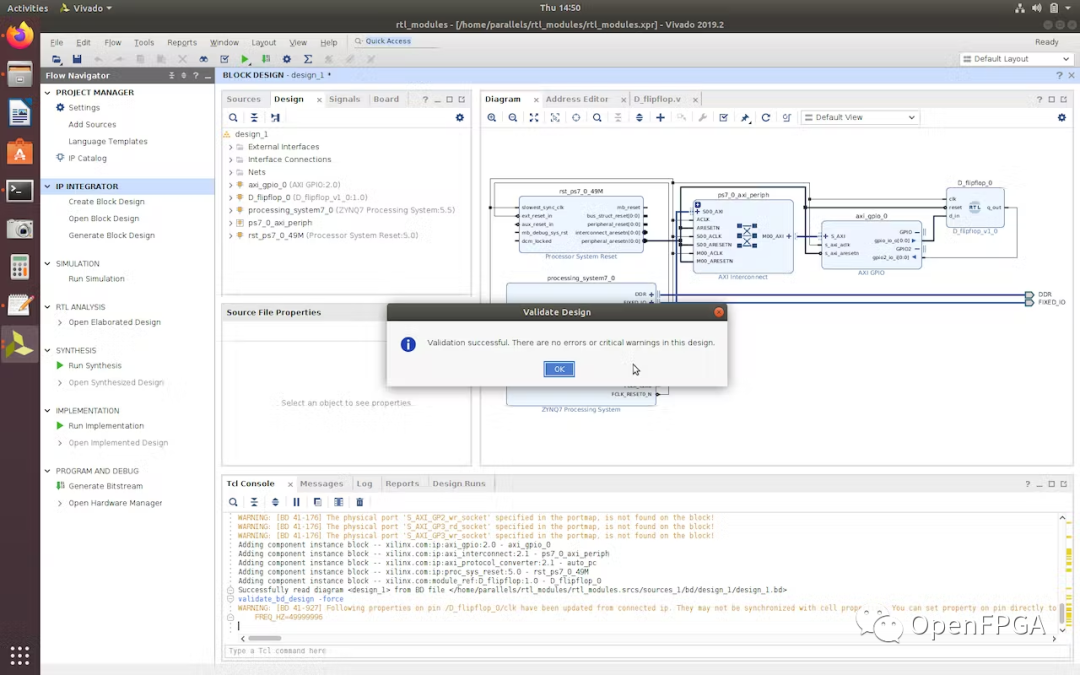

全部连接好后,点击那个勾勾进行验证。

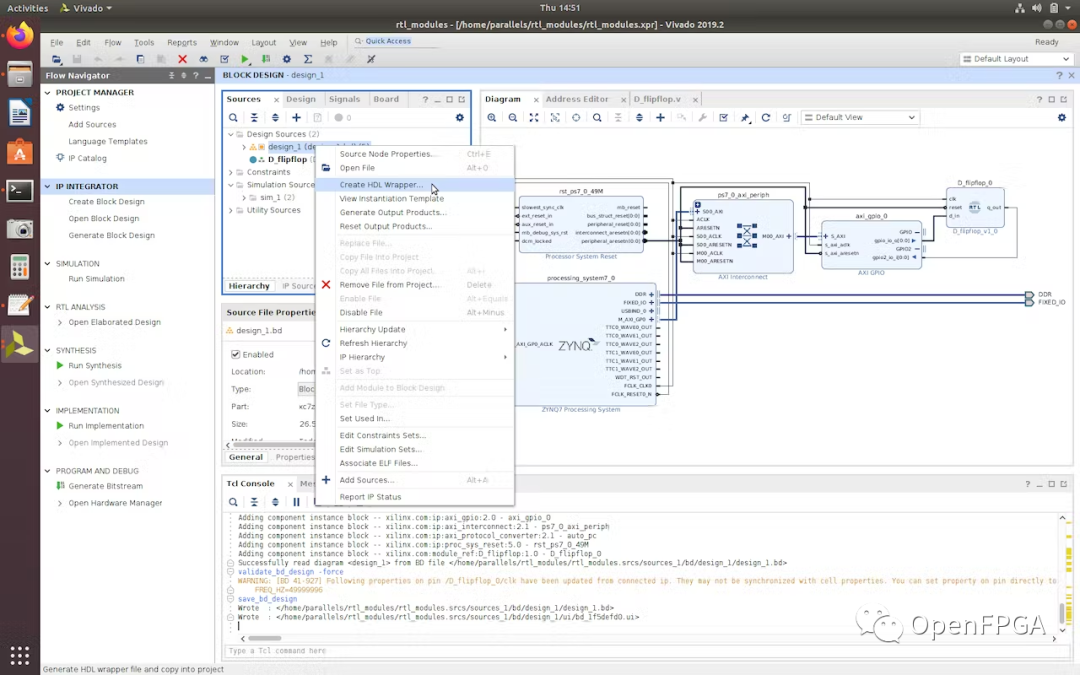

Block Design完成后,为Block Design生成顶层文件。

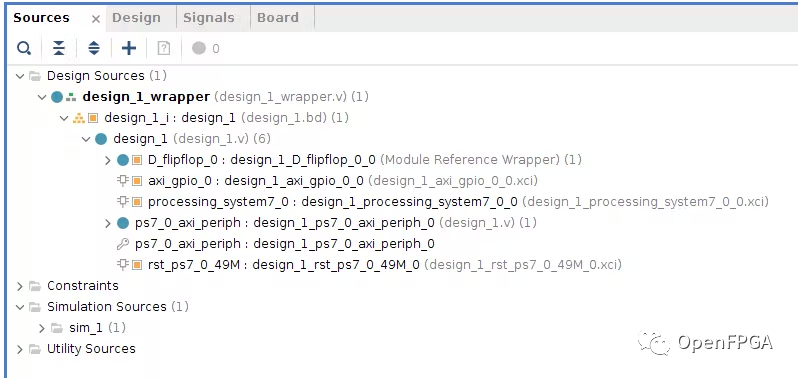

完成后可以看下整个项目的文件层次结构。

就是这样,OVER~

审核编辑:刘清

-

可以将块设计添加到库中吗?2019-04-18 1277

-

在块设计中添加模块引用期间出错2019-04-24 1381

-

将新库添加到Petalinux rootfs的最简单方法是什么2020-05-22 3793

-

怎样将PMSM模块添加到Simulink中2021-09-23 3047

-

为什么无法将DMA添加到SDMMC?2023-01-13 813

-

Yocto S32G添加新层,如何添加到图像?2023-04-25 714

-

如何将TDM业务添加到WiMAX平台上2009-10-20 977

-

如何将Crosswalk添加到Cordova应用程序中2018-11-07 3264

-

S7-1200将模块添加到组态的方法2022-03-11 7289

-

如何将WizFi360 EVB Mini添加到树莓派Pico Python2022-12-01 763

-

将LED添加到十字绣图片2023-02-09 897

-

使用Vivado Block Design设计解决项目继承性问题2023-02-13 4685

-

如何将溶解氧添加到WiFi水培套件2023-06-14 659

-

西门子博途S7-1200:将模块添加到机架的方法2023-09-04 10846

-

安装python怎么添加到环境变量2023-11-23 4706

全部0条评论

快来发表一下你的评论吧 !