clock skew会影响时序收敛吗?

描述

Q:clock skew会影响时序违例吗?

对于发送时钟和接收时钟是同一时钟的单周期路径,时钟抖动对建立时间有负面影响,但对保持时间没有影响。

这一点,在Vivado的时序报告中也可以看到。

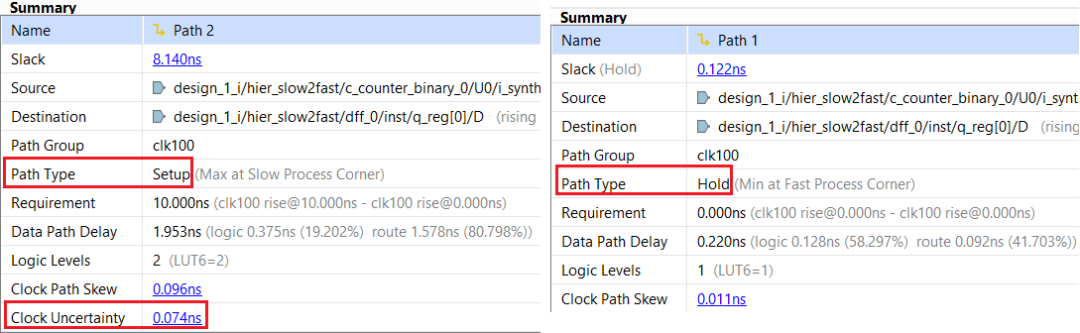

如下图所示,图中左侧为建立时间时序报告,可以看到Clock Uncertainty,而右侧为保持时间时序报告,是没有Clock Uncertainty。

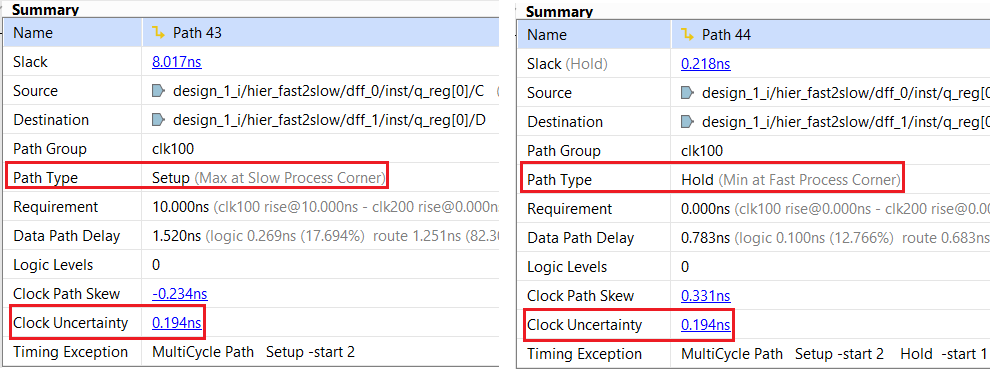

但如果发送和接收是不同的时钟,而且这两个不是异步时钟,那我们可采用多周期路径进行约束,这个时候,skew对建立和保持时间都是有影响的,也可以从时序报告中看出:

Q:定义一个parameter不指明位宽,工具在implemention时应该是会自动转换成最小位宽么?

A:如果parameter没定义位宽,vivado应该会默认为integer类型,parameter的参数应该不会在implemention看到,在综合之前就会把这些参数吃掉了。

Q:有什么好用的时序绘图工具?

A:WaveDrom是一个免费开源的在线数字时序图渲染引擎。它可以使用JavaScript, HTML5和SVG来将时序图的WaveJSON描述转成SVG矢量图形,从而进行显示。WaveDrom可以嵌入到任何网页中。

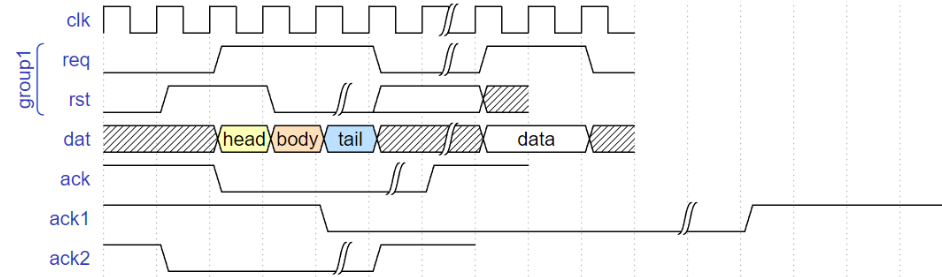

下图是WaveDrom画出来的时序图:

image-20230611175031176

image-20230611175031176

Q:fpga + dac输出波形,为何锯齿波的时候,频率稍微高一点,幅度下降,正弦波却不会下降?

A:这跟锯齿波的频谱有很大关系,如果我们画一下锯齿波的频谱,会发现它的频谱是很宽的,不像正弦波是单一的频点,所以当锯齿波信号带宽超过DAC的带宽时,输出的信号就会被削弱。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

进行RTL代码设计需要考虑时序收敛的问题2020-11-20 5061

-

UltraFast设计方法时序收敛快捷参考指南2021-11-05 6205

-

FPGA时序约束之Skew讲解2023-08-14 2257

-

哪些因此会导致时钟skew过大呢?FPGA中降低时钟skew的几种方法2024-03-13 3380

-

FPGA 高级设计:时序分析和收敛2024-06-17 2111

-

如何减小clock skew?2016-01-14 6896

-

有哪些方法可以解决时序收敛的问题?2021-04-26 3375

-

使用时钟PLL的源同步系统时序分析2010-10-05 1368

-

Skew Correction Using Delay Li2009-04-22 1567

-

fpga时序收敛2017-03-01 996

-

基于MCMM技术IC时序收敛的快速实现2017-10-20 1230

-

时序分析之useful skew的作用分析2018-07-23 19573

-

同步电路设计中CLOCK SKEW的分析说明2021-01-14 1402

-

RQS设计收敛建议ID RQS_CLOCK-122023-07-12 1387

-

RQS_CLOCK-12时钟设置建议2023-07-26 1756

全部0条评论

快来发表一下你的评论吧 !