东京电子成功开发400层堆叠3D NAND闪存技术

描述

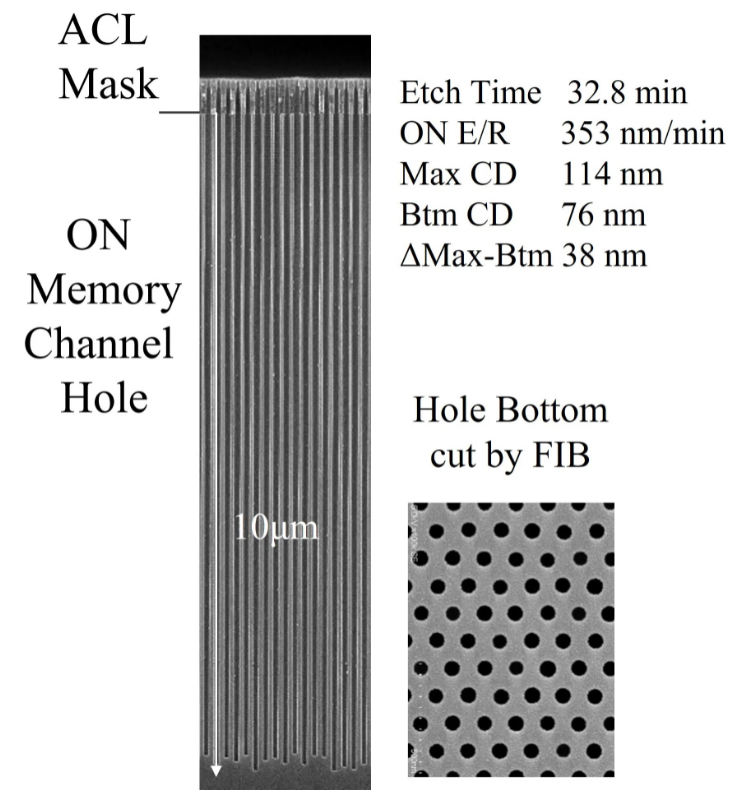

东京电子9日宣布,成功开发出了可以用于制造400段以上堆砌而成的3d nand闪存的“存储器洞蚀刻技术”。研究组开发的新技术首次使电蚀在低温下也能应用,发明了具有很高蚀觉速度的系统。

这一创新技术可在短短33分钟内完成10微米深度的刻蚀,比以往的技术大大缩短了时间。东京电子方面表示:“如果应用该技术,不仅有助于制造高容量3d nand,还可以减少84%的地球变暖危险。”

东京电子表示,开发该技术的小组将于6月11日至16日在日本京都举行的“2023年招待所集成电路技术及工程研讨会”上发表最新成果和报告书。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

3D NAND闪存来到290层,400层+不远了2024-05-25 6338

-

铠侠计划2030-2031年推出千层级3D NAND闪存,并开发存储级内存(SCM)2024-04-07 1548

-

三星将推出GDDR7产品及280层堆叠的3D QLC NAND技术2024-02-01 1504

-

东京电子3D NAND蚀刻新技术或挑战泛林市场领导地位2023-10-16 1579

-

浅谈400层以上堆叠的3D NAND的技术2023-06-15 3338

-

什么是3D NAND闪存?2023-03-30 4704

-

不要过于关注3D NAND闪存层数2020-12-09 3924

-

美光发布176层3D NAND闪存2020-11-12 4037

-

美光宣布了其第五代3D NAND闪存技术2020-11-11 3290

-

联芸成功实现基于4K LDPC纠错的第三代Agile ECC 3闪存信号处理技术的开发和验证 可极大延长NAND的使用寿命2020-04-14 2931

-

3D NAND开发竞争加剧 “5bit/cell”技术也出现了2019-08-10 8459

-

什么是3D NAND闪存?有什么优势?2018-05-28 51622

-

三星48层3D V-NAND闪存技术揭秘2016-07-13 7733

-

SanDisk:3D NAND闪存开始出击2013-07-25 1675

全部0条评论

快来发表一下你的评论吧 !