基于89C55和FPGA的最小系统频率特性测试仪

FPGA/ASIC技术

描述

频率特性是一个系统(或元件)对不同频率输入信号的响应特性,是一个网络最重要的特性之一。幅频特性和相频特性综合称为频率特性。测量频率的方法有点频法和扫频法。传统的模拟式扫频仪价格昂贵、体积庞大,不能直接得到相频特性,给使用带来诸多不便。为此,设计了数字扫频式频率特性测试仪。

1 方案论证与选择

1.1 方案的选择

1.1.1 信号发生模块

方案1:采用模拟分立元件或单片压控函数发生器。可同时产生正弦波、方波、三角波,但由于元件分散性太大,产生的频率稳定度较差、精度低、波形差,不能实现任意波形输出。

方案2:采用传统的直接频率合成器。这种方法能实现快速频率变换,具有低相位噪声以及所有方法中最高的工作频率。但由于采用大量的倍频、分频、混频和滤波环节,导致直接频率合成的结构复杂,并且它也无法实现任意波形输出。

方案3:采用锁相式频率合成器。锁相式频率合成是将一个高稳定度和高精度的标准频率经过加减乘除的运算产生同样稳定度和精确度的大量离散频率的技术,它在一定程度上解决了既要频率稳定精确,又要频率在较大范围可变的矛盾。但由于锁相环本身是一个惰性环节,锁定时间长,故频率转换时间长,频率受限。更重要的弱点是,不能实现任意波形的功能。

方案4:采用直接数字频率合成器(DDFS)。DDFS技术以Nyquist时域采样定理为基础,在时域中进行频率合成,它可以快速改变频率,并且通过更换波形数据可以实现任意波形功能。DDFS相对带宽高,输出相位连续,频率、相位和幅度均可以实现程控。充分利用FPGA内部资源,在其内设置所有逻辑电路实现DDS合成,理论上可达MHz,100 kHz的频段要求很容易实现,而且省去大部分硬件,只需D/A转换输出,避免硬件电路的分部影响。

为尽量减轻硬件负担,充分利用数字资源,在满足应用要求的基础上,选择方案4,在FPGA内部实现频率合成。

1.1.2 被测网络

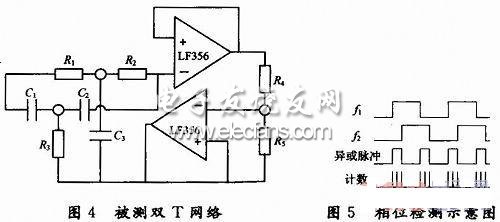

方案1:直接利用阻容双T网络。可以通过改变电容电阻的参数改变中心频率,但其传递函数形式已经固定,带宽大概是中心频率的4倍,Q值固定为0.25,陷波效果较差。

方案2;采用改进双T网络,网络输出经过射级跟随器反馈回网络,可以限制带宽,容易实现应用要求。为此选择方案2。

1.2 系统总体实现方框图

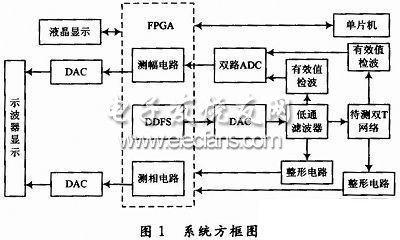

系统方框图如图1。

2 理论分析与计算

2.1 DDS原理分析

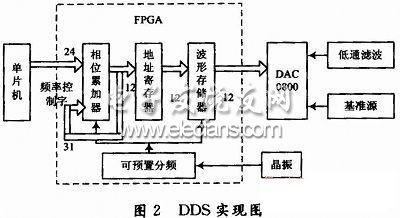

DDS是一种应用数字技术产生信号波形的方法,主要组成:相位累加器、波形存储器、D/A转换器和低通滤波器。基本工作原理是:在参考时钟信号的控制下,通过由频率控制字K控制的相位累加器输出相位码,将存储于波形存储器中的波形量化采样数据值按一定的规律读出,经D/A转换和低通滤波后输出波形。其FPGA内部实现框图如图2所示。

通过DDS技术实现频率合成前需要确定DDS的主要性能参数:

设参考频率源频率为fclk,采用计数容量为2N的相位累加器(N为相位累加器的位数),频率控制字为M,则DDS系统输出信号的频率为fout=fclk/2N×M,频率分辨率为△f=fclk/2N。若选取晶振频率为40 MHz,频率控制字为24位,相位累加器的位数为31位,此时的DDS模块逻辑框图如图3所示,这样的理论输出频率范围为0.02 Hz~312 kHz,步进约为0.02 Hz(40 MHz/231)。

2.2 双T网络

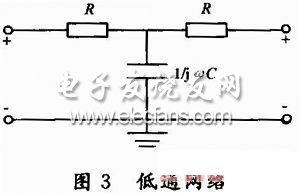

双T网络可看作由一个T型低通网络和一个T型高通网络组成。低通网络如图3所示。将其中的电阻、电容全转换成阻抗表示。传递函数H(jω)为:

2.3 相位测量

此模块采用多周期同步计数法。对输入信号周期进行填充式脉冲计数,具体做法为:利用D触发器产生一个宽度为整数个被测信号周期的同步闸门信号,将同步闸门信号和时钟脉冲信号相与后送入计数器1进行记数,计数值为N1;将同步闸门信号、鉴相脉冲和时钟脉冲三者相与后送入记数器2进行记数,计数值为N2,相位差为φx=(N2/N1)×180。这样可使量化误差大大减小,测量精度得到提高,如图5所示。

闸门的设置、脉冲间的运算、计数等问题在FPGA内部实现可增加系统的灵活性和测量精确度,并可减轻硬件方面的工作量。

3 主要功能电路的设计

3.1 DDS信号发生模块

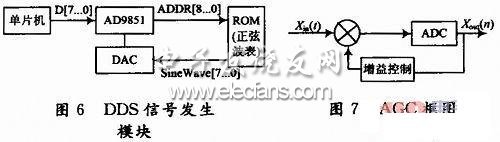

AD9851模块处理单片机送的频率控制字,输出地址值给ROM 1P模块,ROM 1P模块中存储正弦波表,输出幅度值给DA。具体在FPGA内实现如图6所示。

3.2 真有效值测量电路

采用典型真有效值一电流转换芯片AD637,其外围元件少,频带宽。对于有效值为200mV的信号,600 kHz;对于有效值为1 V的信号,-3 dB带宽是8 MHz,其后接12位高速低功耗串口模/数转换芯片ADS7818。为简化电路,并保持电路参数的对称性,仅采用一个ADS7818,通过电磁继电器,由单片机控制,在两路信号间周期性切换进行测幅。

3.3 放大整形及相位测量模块

由于经过双T网络输出的信号幅度衰减很大,而信号经过过零比较器的传输时间为

,式中,G0为过零检测器的直流增益;fP1是第一个响应极点;f为信号频率;VP是信号幅值。由该式可以看出,幅度与相移成反比,所以在经过比较器前要加一级放大,采用的是可变增益放大芯片AD603构成的自动增益控制电路,当输入信号峰一峰值在400 mV~7 V,频率在6 MHz以下,输出信号稳定平坦。在此次应用的实际电路中,将有效值从200 mV~3.5 V,频率从30 Hz~3 MHz的输入信号无失真的都放大到1.72 V。由于DDS输出电压为1.72 V,所以只需放大处理经过网络后的信号。另外,由于前级为双T网络中的射随,故不需做阻抗匹配。AGC(自动增益控制)电路如图7所示。

输出信号经过由LM311构成的零点附近的滞回比较器整形后给FPGA,进行相位测量。经过放大整形后的两路信号先经过一级极性判别电路,通过读取D触发器的输出电平来判断从双T网络输出的信号相位相对于原信号相位超前还是滞后,VOUT输出为高电平时超前,反之为滞后。同时将两个信号送入异或门,得到脉冲信号,测量脉冲信号的宽度,再通过计算就可以得到相位差。当脉冲的宽度很小时,为达到设计要求,标准脉冲的频率要求很高。设计时使用的是40 MHz的晶振,所以得到相位差的表达式为度。

3.4 示波器显示模块

将幅频相频信息加至y轴,频率锯齿波加至x轴。D/A转换采用12位串口电压输出型可程控偏压的数/模转换芯片TLV5638。

4 测试数据与分析

4.1 测试数据结果

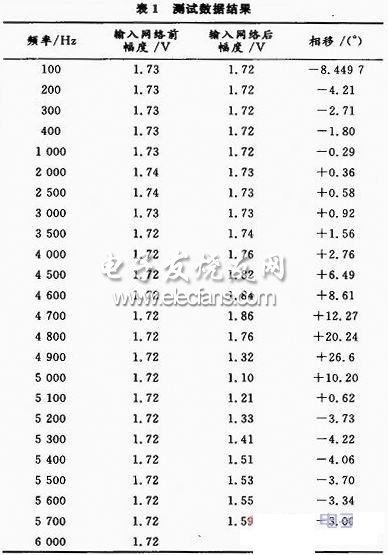

测试数据结果如表1所示。

4.2 数据分析

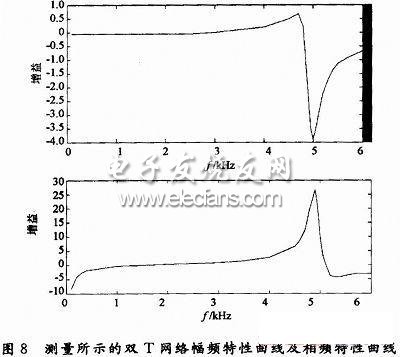

经过测量,双T网络的幅频及相频特性曲线如图8所示。在幅频特性曲线中,横坐标代表频率,一格代表1 kHz;纵坐标代表增益,一格代表0.5倍。在相频特性曲线中,横坐标代表频率,一格代表1 kHz;纵坐标代表相位,一格代表5°。

4.3 误差分析

4.3.1 相位测量误差分析

(1)计数误差。计数器总会存在±1的误差,这个误差是方案本身存在的,无法消除,采用改进的计数方案虽无法消除误差,但可减小误差的影响。

(2)前级处理引入的误差。采用计数法测相前需要对输入的两路信号进行限幅放大、电平转换等处理,由于难以保证处理两路信号的电路线形度完全一致,因此会引入误差。另外在电平转换时,比较器会影响转换的方波上升沿或下降沿不稳定,影响计数结果。

(3)两信号相异或后,用计数法测相位差,其标准时钟信号由晶振产生,采用40 MHz晶振,其晶振频率稳定度也会影响测量结果。

(4)相差测量精度还可以提高。如果相位差精度要达到0.1°,正弦波表数据应该至少储存360×10个点,但这里只储存了1 024个点。

(5)扫频DDS部分还可以提高扫频精度。可以提高FPGA内部时钟频率来提高扫频精度,扫频参考时钟采用10 MHz,因为D/A转换部分是采用转换速度为100 ns的DAC0800,因此完全可以进一步提高参考时钟的频率,DAC0800转换速度完全可以达到。

4.3.2 幅度测量误差分析

幅度测量是采用真有效值检波,AD637芯片本身在检测有效值时存在固定偏差,但对前后信号产生的偏差一致,而且可以通过软件对测量结果进行校准。

5 总结分析与结论

实验表明,DDS信号发生部分扫频范围100 Hz~100 kHz,频率步进10 Hz。用户可以通过按键选择定点测量或特定频率段扫频测量,并能通过LCD显示预置频率、网络前后信号幅值、相位差及其极性,还可在示波器上显示幅频特性和相频特性曲线。此外,可以方便地实现定点测量及特定频率段测量,能够很好地帮助理解频率特性,且其可扩展性好,设计出来的产品体积小,易携带,适合教学等领域的应用。

-

基于单片机和FPGA的频率特性测试仪的设计方案2019-07-22 1770

-

如何设计频率特性测试仪?2019-08-08 2018

-

频率特性测试仪的使用2009-03-08 2656

-

BT-3D频率特性测试仪2010-10-26 1290

-

基于单片机和FPGA的频率特性测试仪2010-12-19 1413

-

频率特性测试仪的设计和调试2009-06-22 4851

-

基于单片机AT89C52的频率特性测试仪设计2010-06-22 2481

-

基于DSP的低频频率特性测试仪2011-03-07 1661

-

简易频率特性测试仪(E题)2015-12-08 948

-

虚拟频率特性测试仪系统的设计2017-01-22 758

-

基于单片机和FPGA的频率特性测试仪的设计2017-11-24 2868

-

基于DDS和FPGA器件实现频率特性测试仪的设计2020-08-05 1806

-

如何使用单片机和FPGA为核心实现频率特性测试仪的设计2020-12-25 1036

-

基于AD9854与STM32设计的频率特性测试仪2021-02-12 6450

-

频率特性测试仪的详细解析2024-05-21 3004

全部0条评论

快来发表一下你的评论吧 !