RA6快速设计指南 [5] 时钟电路 (3)

描述

5

时钟电路

5.5 时钟设置示例

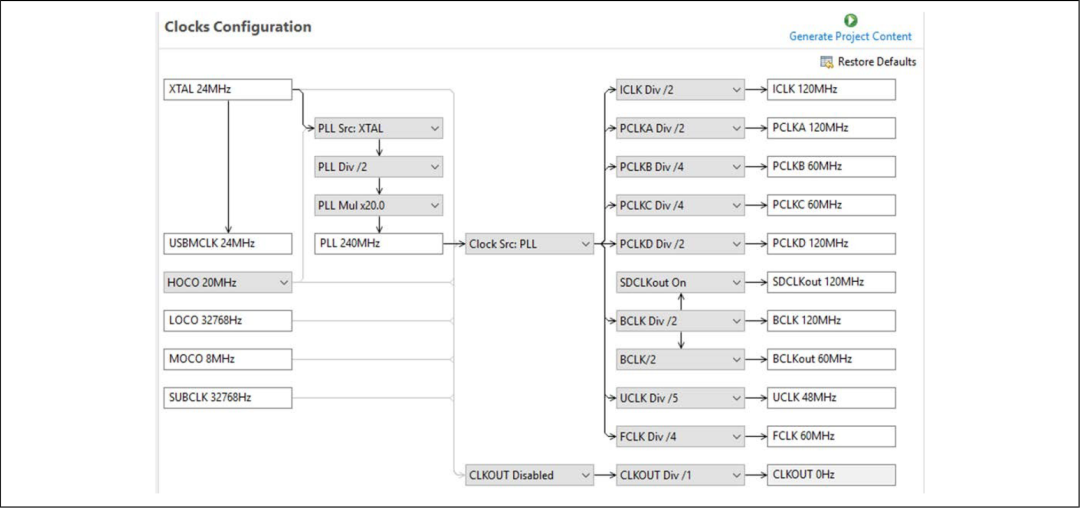

Renesas FSP为RA6 MCU提供了一个简单的可视化时钟配置工具,如下所示。

图11. 使用Renesas FSP配置器进行时钟设置

5.6 HOCO精度

内部高速片上振荡器 (HOCO) 的运行频率为16MHz、18MHz或20MHz,精度为+/-2%或更高。可以通过使能锁频环 (FLL) 功能来提高HOCO的精度,这可将时钟精度提高到+/-0.3%或更高。有关详细信息,请参见硬件手册中的“电气规范”章节。

HOCO可以用作PLL电路的输入。当以这种方式使用HOCO时,不需要外部振荡器。当因空间限制或其他限制而需要减少PCB设计中的元件数量时,这可能是一个优势。不过,此时会因时钟精度问题而产生性能影响和限制,因此应针对您的应用进行评估。

5.7 闪存接口时钟

对内部闪存(ROM和数据闪存)进行编程和擦除操作以及从数据闪存读取数据时,闪存接口时钟 (FCLK) 用作工作时钟。因此,FCLK的频率设置会直接影响从数据闪存读取数据所需的时间。如果用户的程序正在从数据闪存中读取数据,或者正在对内部闪存执行编程或擦除操作,则建议使用最大FCLK频率。

请注意,FCLK频率对读取ROM或对RAM进行读写操作没有任何影响。

5.8 电路板设计

有关使用CGC的更多信息和电路板设计建议,请参见《硬件用户手册》中“时钟生成电路 (CGC)”一章的“使用注意事项”部分。

通常,晶体谐振器及其负载电容应尽可能靠近MCU时钟引脚(XTAL/EXTAL、XCIN/XCOUT)放置。避免在晶体谐振器和MCU之间连接任何其他信号走线。尽量减少每条走线上使用的连接通孔数量。

5.9 外部晶体谐振器选择

外部晶体谐振器可以用作主时钟源。外部晶体谐振器可跨MCU的EXTAL和XTAL引脚连接。外部晶体谐振器的频率必须处于主时钟振荡器的频率范围内。

晶体谐振器的选择在很大程度上取决于各个独特的电路板设计。由于适合与RA6 MCU器件配合使用的可用晶体谐振器的选择可能很多,因此请仔细评估所选晶体谐振器的电气特性,以确定具体的实现要求。

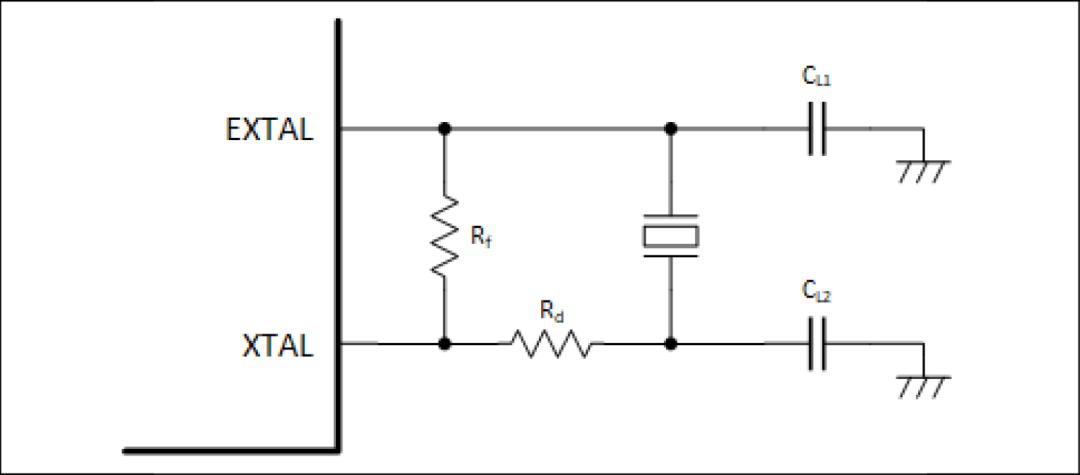

下图给出了典型的晶体谐振器连接示例。

图12. 晶体谐振器连接示例

选择晶体谐振器和相关电容时,必须仔细评估。如果晶体谐振器制造商有相关建议,可以添加外部反馈电阻 (Rf) 和阻尼电阻 (Rd)。

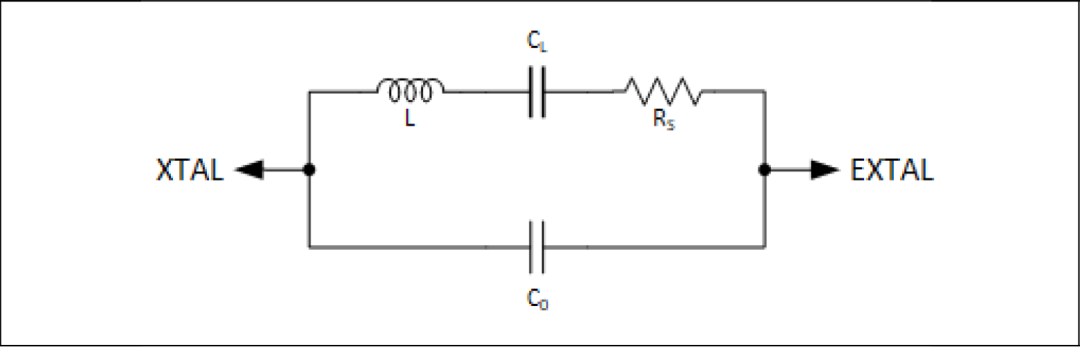

图13. 晶体谐振器的等效电路

CL1和CL2的电容值选择会影响内部时钟的精确度。要了解CL1和CL2值的影响,应使用上图中晶体谐振器的等效电路来模拟该电路。为了获得更准确的结果,还应考虑与晶体谐振器元件之间的布线相关的杂散电容。

下一章:复位要求和复位电路

-

RA2快速设计指南 [3] 时钟电路2023-10-24 1509

-

RA6快速设计指南 [11] 存储器 (3)2023-06-28 1730

-

RA6快速设计指南 [9] 存储器 (1)2023-06-21 2202

-

RA6快速设计指南 [8] 使用TrustZone®2023-06-19 1653

-

RA6 MCU设计之时钟电路2023-06-09 792

-

RA6快速设计指南 [1] 简介,电源,仿真器支持(1)2023-06-04 2424

-

瑞萨RA6系列芯片外扩SRAM方法2023-02-11 3230

-

EK-RA6M5 – 快速入门指南2023-02-02 545

-

EK-RA6M3G – 快速入门指南2023-01-30 548

-

瑞萨电子RA6系列创新套件的使用案例2022-04-22 2897

全部0条评论

快来发表一下你的评论吧 !