SoC设计:NoC 配置和实施流程

电子说

描述

随着SoC的容量和复杂性不断增加,交叉开关带来了路由拥塞、硅芯片面积过度使用和功耗等挑战。

在不久的过去,片上系统 (SoC) 设备与今天的产品相比相对简单。早期的 SoC 通常由 10 到 20 个IP块组成,每个块通常由大约 10,000 到 50,000 个逻辑门组成。大多数这些 IP,包括处理器和外围功能,都是从第三方供应商处获得许可的。开发人员通常只创建一个或两个 IP,其中包含使他们的 SoC 区别于其他竞争产品的“秘密武器”。 当需要有限数量的 IP 来相互通信的互连相对简单时,会使用经典的总线架构方法。负责极少数启动器 IP 的设计人员使用了这种方法,这些启动器 IP 将数据事务请求与响应这些请求的多个目标 IP 相结合。 随着 IP 数量和规模的增加以及它们承担起发起者的角色,采用交叉开关形式的更复杂的互连架构变得很有必要。交叉开关是有利的,因为它允许任何发起者 IP 与任何目标 IP 对话。

然而,随着 SoC 的容量和复杂性不断增加,交叉开关带来了路由拥塞、硅芯片面积过度使用和功耗等挑战。

输入NoC

今天的 SoC 可以包含数百个 IP 块,每个块都比前几代具有更多的逻辑门。通常,第三方供应商提供大部分 IP。除了数据总线宽度、控制总线功能和工作频率的变化之外,每个 IP 还可以采用多种接口协议中的一种——OCP、APB、AHB、AXI、STBus 和 DTL——这些协议已被 SoC 设计人员定义和采用. 应对当今 SoC 中 IP 数量不断增加的挑战的解决方案是采用片上网络 (NoC)。每个 IP 都配备了与 NoC 接口的套接字功能。在发起者触发写访问的情况下,套接字序列化和打包由该 IP 生成的数据,并将其传输到其预期目标。反过来,与目标关联的套接字将从数据包中提取要写入的数据,并将其转换为目标协议。可以同时有多个数据包。

什么是NoC?

NoC 可以通过多种拓扑结构实现,包括不规则树、规则环和网状或圆环结构。高维架构也可用于某些设计,包括三维立方体和四维和五维超立方体。 在大多数情况下,单个 NoC 是不够的,设计人员经常将其互连分解为数十个 NoC 的组合。虽然非高速缓存一致的 NoC 可以满足大多数外设的要求,但处理器和加速器等 IP 通常受益于高速缓存一致的 NoC 的功能。此外,SoC 的某些部分,例如人工智能/机器学习 (AI/ML) 处理节点阵列,可能会受益于网状 NoC 架构。因此,SoC 可以轻松地结合多个 NoC 拓扑以实现最佳结果。 除了用于将 IP 连接到 NoC 的套接字之外,网络还将包括必要的交换机和缓冲区。此外,随着用于实现 SoC 的工艺节点不断缩小,走线的电阻增加,导致信号在通过器件时出现电阻-电容延迟。因此,信号无法再在单个时钟周期内遍历设备的全部或部分。解决这个问题需要在信号通路中插入流水线寄存器。然而,优化它们的数量和位置是一项艰巨的任务。

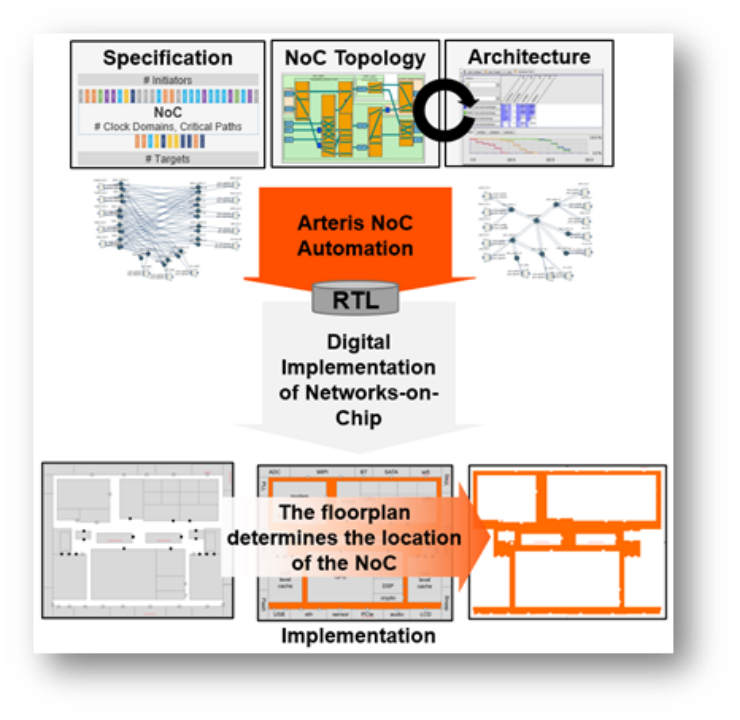

图 1这是典型 NoC 配置和实施流程的概览。来源:Arteris IP

SoC 的开发是双重的——前端(上游)和后端(下游)设计(见图1)。前端设计侧重于逻辑和功能方面,例如使用哪些 IP、如何连接它们以及如何构建网络以确保预期的吞吐量和延迟。另一方面,后端设计处理芯片的物理方面,包括 IP 相对于彼此的放置位置以及时序是否可以满足。只有在这个阶段,设计人员才会知道放置流水线寄存器的数量和位置。 执行完整的物理布局是一个耗时的过程。任何无法在后端解决的问题都必须在前端返工,这将重新启动耗时的物理布局过程(参见图 2)。能够在流程的早期主动插入流水线寄存器对于实现任务的收敛和整个项目的周转时间非常有价值。

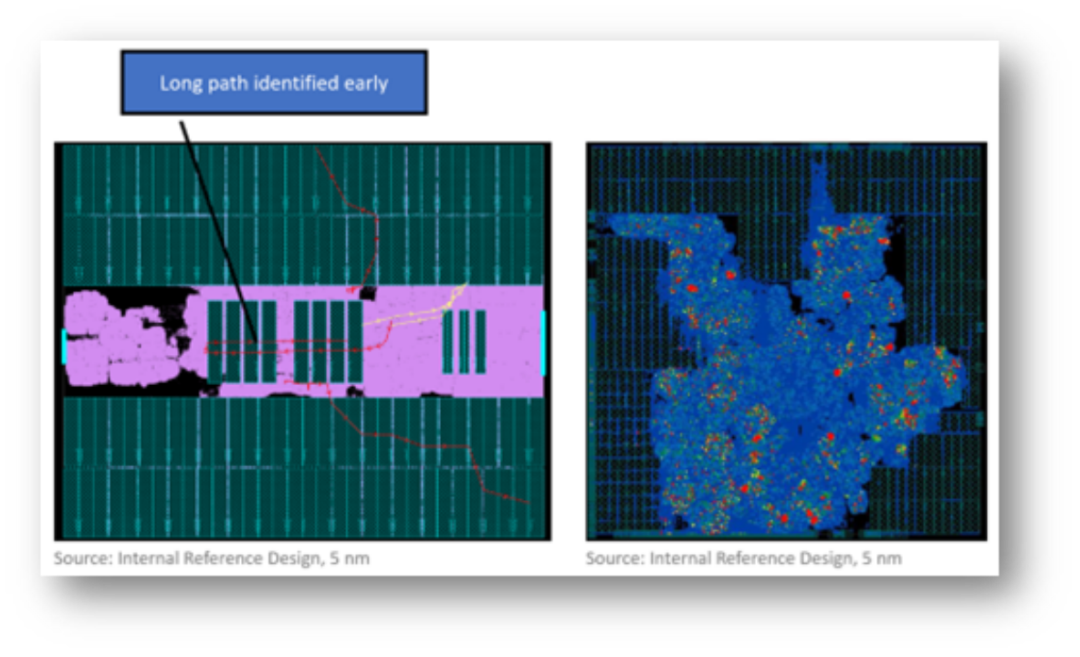

图 2长时序路径可以跨越整个 SoC。来源:Arteris IP

这给前端设计团队带来了很大压力,他们不一定拥有做出明智决策所需的所有信息。插入太少的流水线寄存器会导致 SoC 无法满足物理布局中的时序要求。这导致通过插入太多流水线阶段来过度设计问题的趋势。尽管可能会满足时序要求,但级数过多会增加延迟和功耗。 所有这一切的结果是,仅拥有套接字、开关、缓冲区和流水线寄存器形式的原始 NoC。为了验证性能和实现时序,NoC 的实现工具有必要了解它们将服务的环境。

物理感知NoC

在“物理感知”NoC IP 中,前端设计人员可以使用来自物理布局团队的早期 IP 布局信息来预测实现能力并解决任何潜在的时序问题。作为其中的一部分,NoC 工具可以自动定义 RTL 中流水线寄存器的理想数量和位置,并生成相关的实现约束。 当今的 NoC 技术远远超出了许多设计人员的预期。例如,NoC 生成器利用特定于工艺技术节点的几何和延迟信息。此信息使我们能够进一步完善时序估计并确定流水线寄存器要求和位置。 通过以这种方式改进前端设计并向后端工具提供更详细的信息,可以显著改进整个过程,尤其是第一个物理实现。这可以显著减少后端到前端的迭代次数,从而降低风险、提高生产率、降低成本并加快上市时间和资金周转时间。

编辑:黄飞

-

DCS控制系统的配置与实施流程2024-12-27 3543

-

NoC DDRMC LPDDR4上运行AMD Versal™ Adaptive SoC DCMAC设计示例2024-04-24 1935

-

AMD Versal AI Edge自适应计算加速平台之PL通过NoC读写DDR4实验(4)2024-03-22 15115

-

传智驿芯联手Arteris,利用创新NoC技术驾驭复杂SoC设计2023-09-18 1563

-

AMD Versal系列FPGA NoC介绍及实战2023-07-13 1647

-

从SoC到NoC:芯片架构的演进与变革2023-05-11 15349

-

SOC的多核启动流程详解2023-02-21 2482

-

SoC设计流程相关资料下载2021-11-11 2290

-

SoC芯片的开发流程有哪几个阶段2021-11-08 3694

-

SoC设计流程2021-11-06 1371

-

SOC设计与验证流程是什么?2021-06-21 2210

-

NoC是什么?NoC有哪些技术优势?2021-06-04 3835

-

基于标准单元的SoC芯片设计流程2021-01-26 3009

-

如何利用NoC资源去支撑FPGA中的创新设计2020-10-20 1694

全部0条评论

快来发表一下你的评论吧 !