浅谈Latch-up(一)

电子说

描述

ESD,EOS,Latch-up都是芯片在制造,运输,使用过程中的风险源,他们会对芯片造成不同程度的物理损伤。所以芯片在设计过程中不得不考虑这些因素。前几篇文章都聚焦于ESD防护,这一期讨论芯片Latch-up防护。

一.Latch-up定义

闩锁效应是指体CMOS集成电路中所固有的寄生NPN和寄生PNP组成的电路在一定条件下被触发而形成低阻通路,从而产生大电流,并且由于正反馈电路的存在而形成闩锁,导致CMOS集成电路无法正常工作,甚至烧毁芯片。——《CMOS集成电路闩锁效应》。在日常工作中,作者对闩锁现象分为两种,一种是IO端口电路发生闩锁(尤其是输出buffer),一种就是ESD器件Design Window设计不当发生的闩锁。

而Latch-up与ESD最大的区别在于, 闩锁主要发生在芯片正常使用过程中。 Latch-up测试时,VDD上电,VSS接GND,非测试引脚按要求接高低电位,对VDD/输出输入接测试电流/电压。而ESD主要发生在制造、运输过程中,使用过程。ESD测试时一个引脚接电流源,一个引脚接地,芯片不上电。

1.1 CMOS电路闩锁

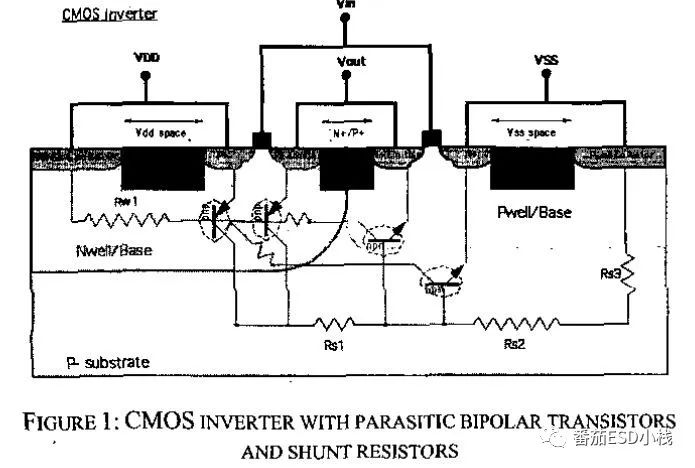

图一.CMOS寄生SCR结构图。

如图所示,CMOS器件里存在多个寄生SCR器件。VDD与GND之间;VDD/输出端口与GND;VDD/输出端口与输出端口;VDD与GND/输出端口。前几期已经介绍过SCR的工作原理,这里不再赘述。

图二.CMOS寄生SCR电路图。

- VDD出现浪涌,N-WeLL/P-WeLL发生雪崩击穿。 大量雪崩载流子经过阱电阻Rnw,Rpw产生压降,寄生SCR开启。寄生NPN与寄生PNP发生正反馈耦合,从而形成低阻通路,发生Latch-up。

2 .输出端电压过冲,寄生SCR中PNP三极管的射电极(输出端)电压高于VDD, 该PNP导通,Rpw产生压降,造成寄生NPN开启,NPN与PNP发生正反馈耦合,从而形成低阻通路,发生Latch-up。

- 输出端电流倒灌,大量电流由NMOS和PMOS的Drain端流入电路中。电流流经阱电阻Rnw和Rpw, 产生压降作用于寄生NPN和PNP的基级,造成寄生NPN和PNP的开启,NPN与PNP发生正反馈耦合,从而形成低阻通路,发生Latch-up。

- 输出端电压下冲,寄生SCR中NPN三极管的射电极(输出端)电压低于GND ,该NPN导通,Rnw产生压降,造成寄生PNP开启,NPN与PNP发生正反馈耦合,从而形成低阻通路,发生Latch-up。

1.2 ESD保护器件闩锁

ESD器件发生闩锁的情况有两种 一种是ESD器件内部寄生SCR的开启,还有一种是Design Window选取不合理。

图三.二极管ESD防护示意图。

如图三所示,使用GCNMOS作为Power Clamp时,端口的ESD防护会使用二极管,P-diode连接端口与VDD,N-diode连接GND与端口。N-diode与P-diode之间会存在寄生SCR器件,如图四所示。(GCNMOS前几期已经讲过,二级管的ESD防护后期也会提及)

图四.二极管寄生SCR示意图。(图源《CMOS集成电路闩锁效应》)

与上文中的CMOS中寄生SCR类似,P-diode与N-diode间也会存在寄生SCR器件且发生Latch-up的情况:

- VDD出现浪涌,N-WeLL/P-WeLL发生雪崩击穿。 寄生SCR开启,发生Latch-up。

- 端口电压过冲,寄生SCR中PNP三极管的射电极(P-diode阳极)电压高于VDD, 该PNP导通,Rpw产生压降,造成寄生NPN开启,发生Latch-up。

- 端口大电流,大量电流进入N-WeLL/P-WeLL, 经过阱电阻产生压降,发生Latch-up。

- 端口电压下冲,寄生SCR中NPN三极管的射电极(N-diode阴极)电压低于GND ,该NPN导通,Rnw产生压降,造成寄生PNP开启,发生Latch-up。

第二种情况就是ESD器件的Design Window设置不合理。 如果ESD器件的IV曲线进入电路的latch-up区,当ESD器件被误触发开启后,ESD器件会一直保持开启,直至损坏。

图五.用于不同电路中的ESD器件以及设计窗口。a)电源钳位电路与设计窗口b)CMOS输出级与设计窗口。c)栅极输入与设计窗口。

如图五所示,不同的防护需求的ESD器件有对应的设计窗口要求。

a)作用于VDD与GND之间的Power Clamp,其Holding Voltage不能小于VDD。VDD的驱动能力近似是无穷大的,如果ESD器件的Holding Voltage进入latch up区,使用过程中一旦VDD的扰动开启ESD器件,ESD器件的低阻通路会一直开启,直到烧毁。

b)作用于输出级的ESD防护器件,其Design Window中的Latch-up区为由PMOS的负载曲线,因为PMOS进入饱和区后存在沟道夹断效应,其过电流能力有限,所以Latch-up区的电流上限有限。ESD器件的Holding Voltage和Holding Current一旦进入PMOS的Latch-up区,PMOS会形成对ESD器件的持续上拉,带来失效风险。

c)作用于输入级的ESD防护器件,其Design Window中的Latch-up区为栅级负载曲线,大部分ESD器件都能避免Latch-up风险。

如果是ESD器件是作用于端口与VDD之间,其栅极输入的Design Window与端口对地一致,而输出级的Design Window需要关注NMOS的负载曲线,避免进入NMOS的下拉负载区内,形成导电通路。

-

jf_73412299

2023-11-13

0 回复 举报电流倒灌怎么引起的latch up 收起回复

jf_73412299

2023-11-13

0 回复 举报电流倒灌怎么引起的latch up 收起回复

-

Latch-Up White Paper2016-10-26 1656

-

CMOS的闩锁效应:Latch up的原理分析2020-12-23 62533

-

芯片设计都不可避免的考虑要素—闩锁效应latch up2023-12-01 6209

-

Latch UP2011-12-16 3451

-

寄生电路的效应:Latch-Up(锁定)2018-08-23 6088

-

静电放电/过度电性应力/闩锁试验 (ESD/EOS/Latch-up)2018-09-18 9848

-

ESD/Latch-Up Considerations wi2009-06-21 525

-

Latch-Up白皮书2017-09-14 1944

-

ADG5401:高伏特式Latch up,单片机SPST交换机2021-05-10 1471

-

USB Type-C应用中选错TVS造成的高度Latch-up风险2021-12-09 851

-

IC工艺和版图设计第八章Latch-up和GuardRing设计2022-02-10 1515

-

浅谈Latch-up(二)2023-06-12 12969

全部0条评论

快来发表一下你的评论吧 !