STM32单片机架构详解

控制/MCU

描述

今天打算继续总结stm32单片机的基础知识,巩固基础。这里呢,声明一下,《stm32单片机基础知识总结》主要基于stm32f1及stm32f4两个系列来做的。原因是stm32f1系列是Cortex-M3内核 ,stm32f4系列是基于Cortex-M4内核。我在项目开发中,主要用到了这两个系列的片子,所以算是对自己知识的一个巩固。另外,知识都是相通的。所以如果理解了这两种架构,那么如果需要的话,我们也能够快速地去学习其他的系统架构。

一、STM32单片机架构

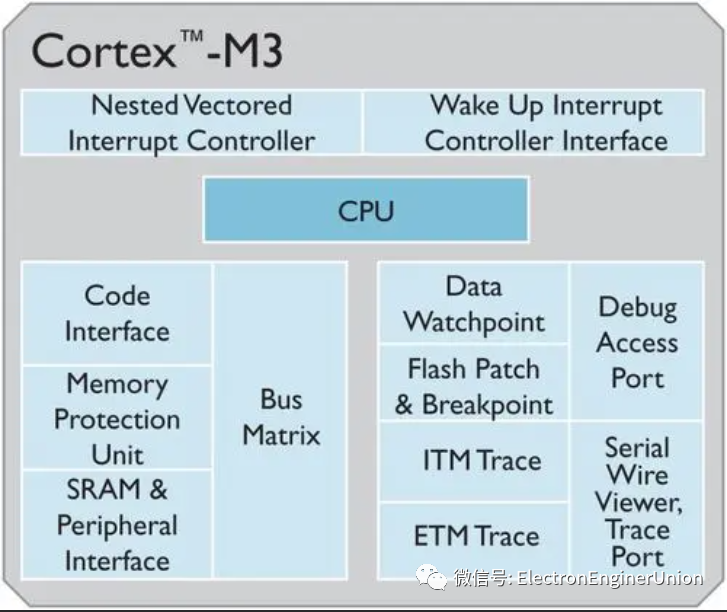

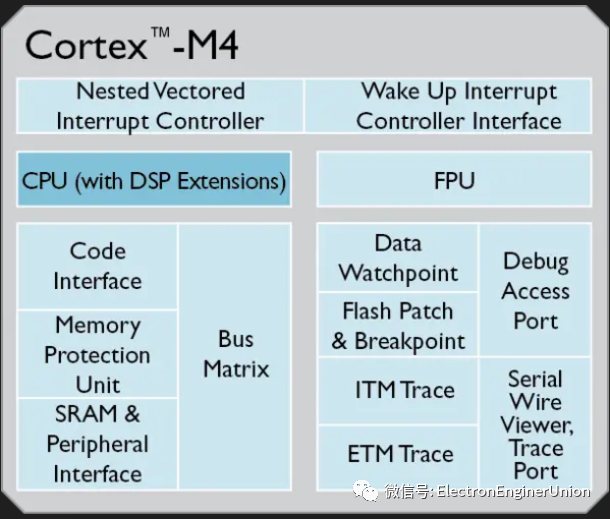

通过两张图片来对Cortex-M3 和Cortex-M4两个内核资源进行一个对比。

通过对此,我们可以看到有这样几个不同之处:

M4具有单精度浮点运算单元,F1没有浮点运算单元。

M4具备增强的DSP指令集。

然后其他共有的模块如下:

内核系统模块

nested vectored interrupt controller

嵌套向量中断控制器

wake up interrupt controller interface

唤醒中断控制器接口

DSP:数字信号处理单元,

FPU:浮点运算器

Memory Interface Unit(MPU):存储器保护单元

它可以实施对存储器(主要是内存和外设寄存器)的保护,以使软件更加健壮和可靠。在使用前,必须根据需要对其编程。如果没有启用MPU,则等同于系统中没有配MPU。

MPU有如下的能力可以提高系统的可靠性:

阻止用户应用程序破坏操作系统使用的数据。

阻止一个任务访问其它任务的数据区,从而把任务隔开。

可以把关键数据区设置为只读,从根本上消除了被破坏的可能。

检测意外的存储访问,如,堆栈溢出,数组越界。

此外,还可以通过MPU设置存储器regions的其它访问属性,比如,是否缓区,是否缓冲等。

SRAM &Peripheral interface:SRAM&外设接口

Bus Matrix:总线矩阵用于多主(Core,DMA等),多从(内部RAM,APB,外部总线等)的交联和仲裁。目的是为了提高不同主机访问不同外设情况下的带宽。

跟踪调试系统

Data Watchpoint:

用于实时变量监控,可用于定期输出PC或各种CPU内部计数器,从目标获取分析信息。

Flash Patch &BreakPoint:转换及断电单元

ITM Trace:

指令跟踪宏单元,一种针对MCU进行跟踪调试的新方法,与打断点(Breakpoint)不同,ITM方法不需要暂停程序运行,可以在程序全速运行的过程中实时输出变量的数值以便观察,即Trace功能

ETM Trace:集成跟踪选项

Debug Access Port:调试端口

Serial Wire Viewer ,Trace port :串行线查看器,跟踪端口

以上把所有的模块都简单翻译了一下,个别的稍加阐述。篇幅原因就不再进行深入了。感兴趣的朋友可以网上再查一查资料。我这里当是抛砖引玉了。

针对stm32f1与stm32f4,两个片子的框架,再进行一个简单总结。整个这些知识内容都是一些基础的东西,可能很多东西不懂也能够把代码写出来,调试也能通过。入门的话,也可以了。我个人觉得想走更远,应该知其然也知其所以然。虽然我水平一般,需要学习实践的地方有很多。但从多年的工作经历来说,我觉得做到大而广不难,做到大而广还要细就是很考验人的了。

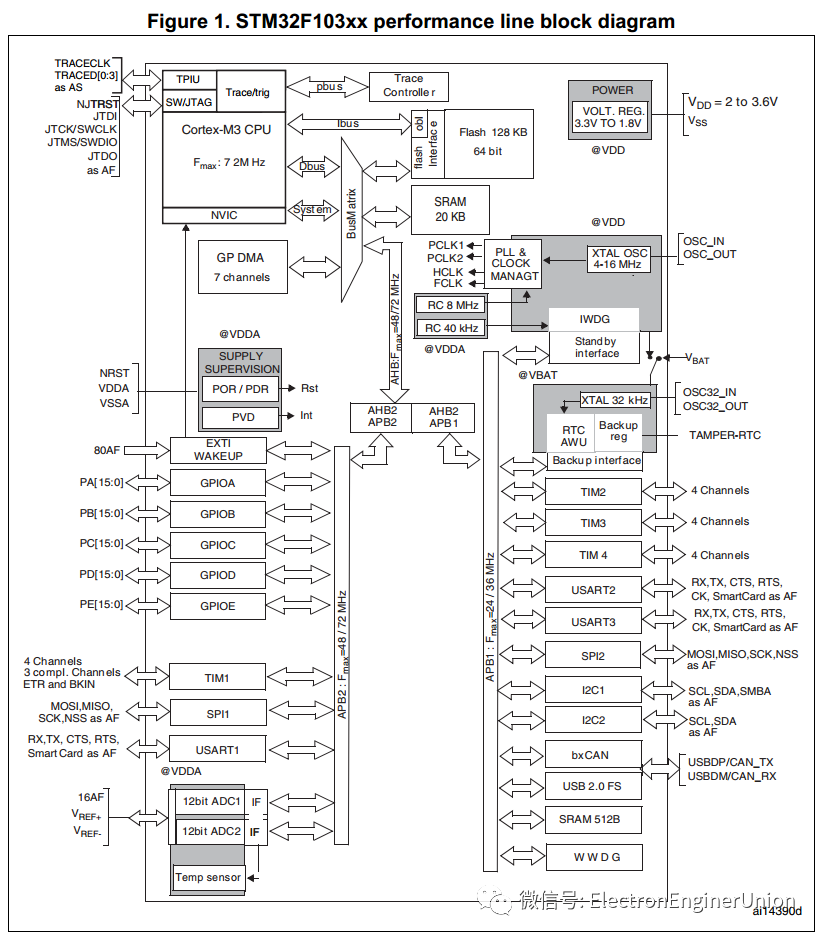

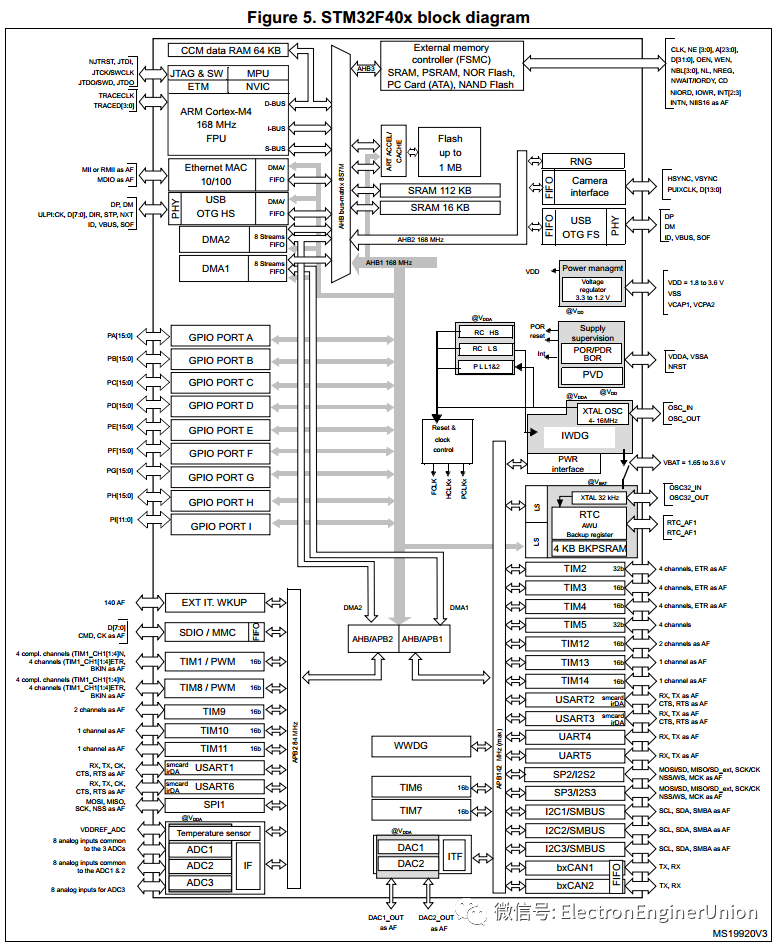

下面两张Block diagram 是我从ST官方文档上面截下来的。第一张是STM32f103。第二张是STM32F40x。STM32f103是基于Cortex-M3架构。STM32f40x是基于Cortex-M4架构。很明显STM32f40x芯片的内核所挂载的资源相当于STM32f103芯片所挂载的资源要丰富很多。

stm32f103内部架构图

stm32f40x架构图

从上面两张架构图中,我们可以读出很多信息。

1)stm32f1主频最高是72MHZ.stm32f4主频最高是168MHZ,且集成了FPU功能。

2)F1内部SRAM最大64K字节, F4内部SRAM有192K字节(112K+64K+16K)。

3)四个主动单元 :

M3内核的ICode总线(I-bus)、DCode总线(D-bus)、 系统总线(S-bus)、DMA(DMA1、DMA2、以太网DMA)

ICode总线 :

将M3内核的指令总线与FLASH指令接口相连,用于指令预取

DCode总线:

将M3内核的数据总线与FLASH数据接口相连,常量加载和调试

系统总线 :

将M3内核的系统总线与总线矩阵相连,协调内核与DMA访问

DMA总线:

将DMA的AHB主控接口与总线矩阵相连,协调CPU的DCode和DMA到SRAM、闪存、外设的访问

4)四个被动单元 :

内部SRAM、内部闪存、FSMC、AHB到APB桥

AHB桥:

AHB(Advanced High performance Bus),高性能总线。主要用于高性能模块(如CPU、DMA和DSP等)AHB 系统由主模块、从模块和基础结构(Infrastructure)3部分组成,整个AHB总线上的传输都由主模块发出,由从模块负责回应。

APB桥:

APB(Advanced Peripheral Bus),片上外设总线。主要用于慢速片上外设与ARM核的通讯。

例如UART、1284等,它的总线架构不像 AHB支持多个主模块,在APB里面唯一的主模块就是APB 桥。再往下,APB2负责AD,I/O,高级TIM,串口1;APB1负责DA,USB,SPI,I2C,CAN,串口2345,普通TIM。

cortex-M3、cortex-M4内核是由ARM公司提供的。芯片其余外围是由ST公司设计完成的。

篇幅有限,很多要点的内容也需要时间的沉淀。后续的工作学习中,再对这些知识点做补充优化。

-

基于51与STM32单片机架构2023-09-11 2209

-

一文详解GD32单片机和STM32单片机2023-08-09 13317

-

8051单片机架构类型有哪些2023-07-07 2732

-

详解STM32单片机和51单片机的区别2022-04-18 40383

-

详解STM32单片机的堆栈2022-02-08 1091

-

STM32单片机架构2022-01-05 1659

-

STM32单片机GPIO口简介2021-12-28 1477

-

总结下单片机的这几种架构2021-12-09 1533

-

hc05与单片机连接图_STM32单片机最小系统详解2021-11-17 1838

-

单片机入门--常见单片机PIC\STM322021-11-13 1641

-

51单片机与STM32单片机架构的区别在哪2021-07-01 1173

-

单片机的应用程序架构解析2021-04-02 1285

-

详细图文剖析STM32单片机串口一键下载电路与操作方法2017-12-31 48269

-

单片机程序架构详解篇2012-08-17 6532

全部0条评论

快来发表一下你的评论吧 !