EMC测试实质之共模传导性抗扰度

EMC/EMI设计

描述

在我们的EMC测试案例中,共模传导性抗扰度测试的例子还是很多的,例如:

- IEC61000-4-6 或 ISO11452-7 标准规定的传导抗扰度测试;

- 标准 IEC61000-4-4 规定的电快速瞬变脉冲群 ( EFT/B) 测试;

- 标准 IEC61000-4-5 规定的线对地浪涌测试;

- 标准 ISO11452-4 规定的BCI(Bulk current injection也称大电流注入法,是机动车电子电器组件的电磁辐射抗扰性限值和测量方法)测试

- 国军标GJB152A 中规定的 CS109、 CS114、 CS115、 CS116 测试。

其中标准IEC61000-4-4规定的EFT/B和 ISO11452-4 规定的 BCI 测试是最典型的共模抗扰度测试。

Part 1

共模干扰电流干扰原理

在共模抗扰度测试中,我们的测试方法和原理如下:

首先,我们通常会在被测产品的各种电源端口和信号端口上,叠加以共模干扰电压;

这种共模干扰电压通常会以共模电流的形式被注入到被测产品的内部电路中;

因为不同位置阻抗不同,所以共模电流会在电路中转换成差模干扰电压,而这种干扰电压,是很可能影响正常的电压信号的,具体过程下面会详细介绍。

另外,需要注意的是,产品的机械结构形式在EFT/B 共模电流的路径与大小上起着决定性的作用。

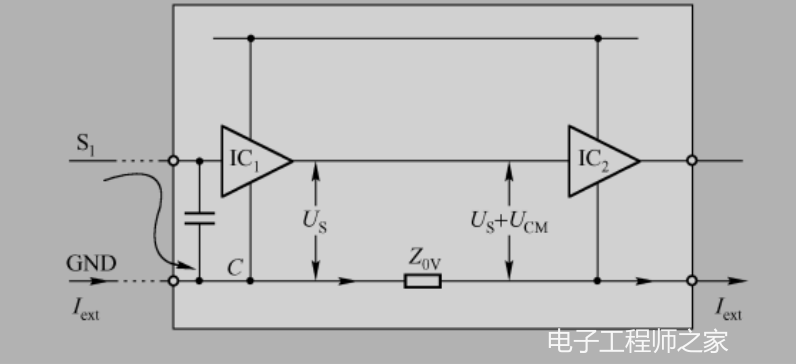

下图为共模干扰电流流过地阻抗产生压降的过程:

从图中我们可以得到如下信息:

当在信号线S1和GND上同时注入共模电流Iext时,由于S1的对地阻抗和比GND对地阻抗高,所以会在IC1输入端口形成差模干扰信号。

电容 C 起到滤波的作用,保护了芯片IC1,这也是我们常常在连接器接口附近加滤波电容的原因。

人往高处走,水往低处流,电流也像水流一样,会沿着低阻抗的路径进行传输,图中Z0V为两个芯片之间的地阻抗,US为有用信号。

UCM为Z0V两端的电压,也可以被称为干扰电压,其中

UCM≈Z0V*Iext.

由上面式子可以看出,当干扰电流一定时, 干扰电压 UCM的大小由 Z0V决定。

也就是说,要想干扰最小,就要尽量减少地平面阻抗,为此,我们可以在 PCB 中单独设置一个地平面。

例如, 一个完整 (无过孔、 无缝隙) 的地平面, 在100 MHz的频率时, 只有约3.7mΩ 的阻抗。

即使有 100A 的瞬态电流流过 3.7mΩ 的阻抗, 也只会产生 0.37 V 的压降, 种压降对于一般的信号电平来说不会造成影响。

但是,如果地平面存在1cm的缝隙就会产生1nH的电感效应, 当有 100 A 的电快速瞬变脉冲群共模电流流过这个裂缝时, 所产生的压降如下:

V = | L×dI/ dt |=1nH×100 A/5ns = 20 V

20V的压降就几乎对所有的常规信号造成影响了,这就是我们经常在设计中强调的设计规则:一定要保持地平面的完整性。

Part 2****共模干扰电流对差分电路的干扰原理:

如下图所示:

同前面单端信号类似,当共模电流 ICM流过地平面时, 必然会在地平面的阻抗 Z0V两端产生压降。

假设模电流ICM保持不变, 地平面阻抗越大, 压降就会越大。

图中UCM1 、 UCM2 、 UCM3 、 UCM4可以看成是由共模电流引起的差分线对参考地的共模干扰电压 。

图中Z1 、 Z2为差分线对与参考地之间的阻抗, ZS1 、 ZS2为IC的输入/ 输出阻抗,由于我们在设计中,不可能保证Z1 和 Z2,ZS1 和ZS2完全相等,这样就会造成UCM1 、 UCM2 、 UCM3 、 UCM4的值也不完成相同。

这样由于电路的不平衡,造成部分共模电压转化为差模干扰电压 U diff , 进而对差分信号电路产生干扰。

由此可见, 对于差分信号来说, 地平面的阻抗也同样重要。

同时, PCB 在Layout时, 一定要保证差分线对的各种寄生参数保持平衡一致,如有完整的参考地平面,过孔位置相同,保持等间距等规则一定要遵守。

-

从浪涌抗扰度的角度设计EMC前级电路2015-07-16 11859

-

EMC原理 之 传导(共模差模)辐射(近场远场)2015-08-03 7269

-

EMC检测技术研究(连载)射频场感应的传导骚扰抗扰度试验2015-08-05 7029

-

固定灭火系统控制装置传导骚扰抗扰度测试研究2015-08-06 2947

-

【下载】《EMC电磁兼容设计与测试案例分析(第2版)》2017-09-25 22708

-

EMC辐射传导租场测试多少钱一个小时?2018-04-11 3468

-

EMC中辐射抗扰度测试2019-06-09 3740

-

0Hz~150kHz共模传导骚扰抗扰度试验2016-07-20 1649

-

电磁兼容 试验和测量技术 0Hz~150kHz共模传导骚扰抗扰度2016-12-09 1359

-

七种EMC抗扰度测试方法2020-05-20 10190

-

电磁兼容之射频场感应的传导骚扰抗扰度2021-08-11 1267

-

如何使用EMC测试软件执行辐射抗扰度测试?(三)软件检查及手动模式2024-03-18 1813

-

EMC问题解决实战教学4——CS抗扰度问题解决!2024-06-04 3327

-

共模瞬变抗扰度(CMTI)的定义及重要性,影响因素测试方法及应用2025-10-30 885

全部0条评论

快来发表一下你的评论吧 !