超高速微控制器硬件增强串口功能

描述

本应用笔记介绍了达拉斯半导体DS89C430和DS89C450超高速微控制器的全新串行端口特性。增加时钟倍频器允许用户选择原始频率四分之一的晶体,以产生相同的波特率并降低EMI。

概述

与每个指令周期至少需要8051个时钟的原始12架构相比,超高速微控制器具有先进的8051内核架构,能够在短短一个时钟周期内执行指令。为了补充高性能内核,标准8051片上外设中集成了新的硬件功能。其中两个新功能,时钟乘法器和可选的高速时钟到定时器,可以直接影响串行端口的波特率生成。本文档的目的是解释这两个新功能与串行端口波特率生成之间的交互。

串行端口模式

DS89C430串行端口提供四种基本工作模式。模式 0 允许使用源自系统时钟的波特时钟对 8 位数据进行半双工同步通信。模式 1 允许 8 位数据与源自定时器 1 或定时器 2 的波特时钟进行全双工异步通信。模式 3 与模式 1 的不同之处在于支持 9 位数据传输和接收。模式2同样提供9位数据通信,但其波特时钟直接来自振荡器频率。为了支持模式 1、2 和 3 异步通信,起始位始终位于数据之前,停止位始终位于数据之后。每种串行端口模式的完整详细信息可在超高速微控制器用户指南中找到。

时钟乘法器

超高速微控制器集成了片上时钟倍频器,可在降低外部晶体时钟频率的情况下提供更高的性能。乘法器可以配置为生成双倍 (2X) 或四倍 (4X) 的内部系统时钟,由 2X/4X 特殊功能寄存器位 (PMR.3) 控制。请注意,由此产生的2倍或4倍乘法系统时钟仍不能超过数据手册中规定的最大工作频率。有关乘法器的完整详细信息,请参阅超高速微控制器用户指南。

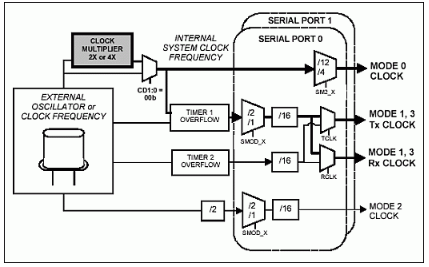

一旦时钟乘法器输出被选为内部系统时钟(CD1:0 = 00b),从系统时钟派生的某些串行端口波特率时钟(不再等于外部振荡器频率)将发生变化。图 1 突出显示了使用 2X 或 4X 乘法系统时钟时可能受影响的串行端口时钟。串行模式 0 波特率始终不同,串行模式 2 波特率永远不会不同,串行模式 1、3 波特率可能不同,具体取决于所使用的定时器和/或定时器输入时钟选择。如图1所示,表1表示哪些串行端口模式受时钟乘法器的影响。附录 A 包含使用 2X 或 4X 时钟乘法器模式时执行波特率计算的详细公式。

图1.串行端口时钟受时钟乘法器输出选择的影响 (CD1:0 = 00b)。

| 串口模式 | 波特时钟源 |

波特时钟取决于 内部系统时钟(时钟 倍频器选择) |

|

模式 0 (同步 - 8 位) |

系统时钟/4 系统时钟/12 |

是的 |

|

模式 1 (异步 - 10 位) |

小时 1 小时 2 |

是¹ 否² |

|

模式 2 (异步 - 11 位) |

振荡器时钟/32 振荡器时钟/64 |

不 |

|

模式 3 (异步 - 11 位) |

小时 1 小时 2 |

是¹ 否² |

|

¹ 仅当启用 4 分频或 1 分频定时器 1 输入时钟时(T1M = 1 或 T1MH = 1)。为了与原始 8051 兼容,默认定时器 1 输入时钟 (T1MH, T1M = 00b) 固定为振荡器时钟除以 12。 ² 仅适用于串行端口 0 上的波特率生成。 |

||

优点:更快的波特率,更低的EMI

使用时钟乘法器时,应用优势可能很大。一个原始频率四分之一的外部晶体时钟可用于产生与以前相同的串行模式 0 和(定时器 1 生成)模式 1、3 波特率,但 EMI 大大降低。或者,当内部乘以 2 倍或 4 倍时,相同的外部晶体现在可以生成高达四倍的波特率!

高速输入时钟至定时器

为了使片上定时器对应用最有用,每个定时器都应能够以相当于最小指令周期的速率跟踪时间。对于以 8051 个振荡器时钟执行指令的原始 12 架构,定时器以振荡器频率除以 12 速率计时。当达拉斯半导体公司推出其高速微控制器时,该微控制器缩短了四个振荡器时钟的机器周期,为每个定时器提供了一个可选择的振荡器频率除以4个输入时钟控制。当高速微控制器系列中添加时钟乘法器功能时,可选择的4分频被修改为系统时钟的函数,而不是振荡器时钟。现在,超高速微控制器具有单时钟周期指令执行功能。同样,每个片上定时器都进行了升级,集成了可选系统时钟除以1个输入。

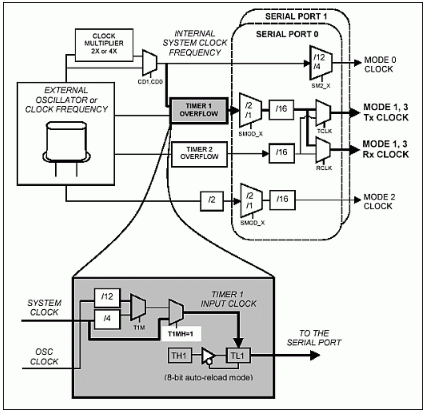

CKMOD (0h) SFR 中包含的 T1MH、T2MH 和 T96MH 位分别使系统时钟除以 1 个输入到定时器 0、定时器 1 和定时器 2。启用定时器的高速系统时钟输入 (TxMH = 1) 将自动覆盖系统时钟除以 4 个输入 (TxM = 1) 设置。新的系统时钟除以 1 个定时器输入,如系统时钟除以 4 个输入,在使用定时器1时会影响波特率的产生。图2突出显示了可能受选择定时器1高速时钟输入影响的串行端口时钟。

图2.串行端口时钟受高速定时器1输入(T1MH = 1)选择的影响。

优点:波特率更快,波特率分辨率更高

相对于串行端口操作,除以1个输入时钟功能可转化为两个用户优势。首先,在系统时钟频率相同的情况下,使用定时器1时,现在可以为串行模式3和1生成四倍的波特率。其次,时钟定时器1的速度更快,可实现更高的波特率分辨率,从而可能减少与应用已使用的波特率相关的误差,或者使新的波特率在应用使用的可接受误差范围内。

例如,假设用户当前有一个以 20MHz 系统时钟频率运行的达拉斯高速微控制器应用程序。该应用程序使用其中一个串行端口与PC进行RS232通信,并要求两者之间的波特率不匹配<3%。如果使用定时器1(在8位自动重新加载模式下)生成波特率,下面的表2给出了Dallas高速微控制器与新型超高速微控制器的“良好”波特率样本。不可接受的波特率(不匹配> 3%)已用灰色阴影显示。表3对25MHz的系统时钟频率进行了相同的“良好”波特率比较。可以清楚地看到,启用高速定时器1输入时钟可提供更精细的波特率分辨率。附录 A 包含利用定时器1 (T1MH = 1) 的系统时钟输入时执行波特率计算的详细公式。

| 电脑 UART (8250/16450) | 高速微控制器(T1M = 1 的定时器 1 用于波特率生成,SMOD_x = 1) | 超高速微控制器(T1MH = 1 的定时器 1 用于波特率生成,SMOD_x = 1) | ||||

| 重新加载 | 波特率 | 波特率 (TH1) | % 误差 | 波特率 (TH1) | 错误 | |

| 1 | 115200 | 104166 (FD) | -9.6 | 113636 (F5) | -1.4 | |

| 2 | 57600 | 62500 (FB) | 8.5 | 56818 (EA) | -1.4 | |

| 3 | 38400 | 39062 (F8) | 1.7 | 37879 (DF) | -1.4 | |

| 4 | 28800 | 28409 (F5) | -1.4 | 29070 (D5) | 0.9 | |

| 5 | 23040 | 22321 (F2) | -3.1 | 23148 (加利福尼亚州) | 0.5 | |

| 6 | 19200 | 19531 (F0) | 1.7 | 19231 (BF) | 0.2 | |

| 7 | 16457 | 16447 (ED) | -0.1 | 16447 (B4) | -0.1 | |

| 8 | 14400 | 14204 (EA) | -1.4 | 14368 (A9) | -0.2 | |

| 9 | 12800 | 13020 (E8) | 1.7 | (12755) (9E) | -0.4 | |

| 10 | 11520 | 11574 (E5) | 0.5 | 11574 (94) | 0.5 | |

| 11 | 10472 | 10417 (E2) | -0.5 | 10417 (88) | -0.5 | |

| 12 | 9600 | 9469 (DF) | -1.4 | (9615) (7E) | 0.2 | |

|

电脑 UART (8250/16450) |

高速 微控制器 (T1M = 1 的定时器 1 用于波特 率生成,SMOD_x = 1) |

超高速 微控制器 (T1MH = 1 的定时器 1 用于波特 率生成,SMOD_x = 1) |

|||

| 重新加载 | 波特率 | 波特率 (TH1) | % 误差 | 波特率 (TH1) | 错误 |

| 1 | 115200 | 130208 (FD) | 13.0 | 111607 (F2) | -3.1 |

| 2 | 57600 | 55803 (F9) | -3.1 | 57870 (E5) | 0.4 |

| 3 | 38400 | 39062 (F6) | 1.7 | 38110 (D7) | -0.8 |

| 4 | 28800 | 27901 (F2) | -3.1 | 28935 (加利福尼亚州) | 0.5 |

| 5 | 23040 | 22978 (EF) | -0.3 | 22978年(公元前) | -0.3 |

| 6 | 19200 | 19531 (欧共体) | 1.7 | 19290 (AF) | 0.5 |

| 7 | 16457 | 16276 (E8) | -1.1 | 16447 (A1) | -0.1 |

| 8 | 14400 | 14467 (E5) | 0.5 | 14335 (93) | -0.5 |

| 9 | 12800 | 12600 (E1) | -1.6 | 12807 (86) | 0.1 |

| 10 | 11520 | 11489 (德语) | -0.3 | 11489 (78) | -0.3 |

| 11 | 10472 | 10557 (分贝) | 0.8 | 10487 (6B) | 0.1 |

| 12 | 9600 | 9527 (D7) | -0.8 | 9586(5D) | -0.1 |

应用示例 #1

SPI 模式 (1,1) 接口,使用同步串行模式 0

虽然可以通过“位敲击”端口引脚与SPI™器件接口,但使用同步串行模式0可减少软件开销并实现更快的通信速度。同步串行工作模式在 TXD 引脚上提供移位时钟,并在移位时钟 (TXD) 的每个上升沿处在 RXD 引脚上写入/读取串行数据。由于 TXD 处于高电平状态,因此同步串行模式与 CPOL = 1、CPHA = 1 SPI 模式紧密对齐。由于同步串行模式不需要每个位的 3 样本多数投票方案(如异步串行模式),因此它能够比任何其他串行模式更快地实现波特率。下图显示了DS89C430微控制器与SPI模式(1,1)兼容EEPROM器件之间的接口。

图3.SPI兼容外设的串行端口接口示例。

串行端口 0 首先置于模式 0,并配置为产生系统时钟除以 4 波特时钟。根据所连接的SPI外设的时序限制,可能需要选择降低的系统时钟或系统时钟除以12波特时钟。在外部,TXD引脚(P3.1)提供串行时钟并连接到EEPROM的SCK输入。RXD 引脚 (P3.0) 通过连接到 EEPROM 的 SI 输入和 SO 输出来处理所有 SPI 数据事务。使用共享 SI/SO 配置的能力将取决于连接的 SPI 外设的 I/O 时序。第三个微控制器端口引脚未链接到片上串行端口硬件,用作SPI外设芯片选择输入。在本例中,端口引脚P3.2将连接到EEPROM/CS输入,并由软件手动置位和取消置位。由于串行端口首先通信LSB,而SPI外设希望首先通信MSB,因此在大多数情况下使用查找表进行字节转换。

已经创建了两个例程,XRAM_store 和 XRAM_recall,并且完全按照它们的名字简单地执行。XRAM_store例程将内部1kB SRAM的电流内容写入指定的1kB范围的EEPROM,而XRAM_recall将指定的1kB范围的EEPROM读取到DS89C430片内SRAM中。此代码仅用作示例,可轻松调整为访问微控制器或EEPROM存储器的不同地址范围,以较小或较大的块。

应用示例 #2

使用异步串行模式 485 的 RS-3 网络

异步串行端口模式以与普遍接受的RS-232协议兼容的格式发送和接收数据。超高速微控制器以其最大系统时钟频率(33MHz)运行时,并使用系统时钟定时器输入(T1MH = 1),可以实现超过2Mbaud的异步波特率。(超高速微控制器包含一个表格,显示每种串行模式的最特率)。遗憾的是,为了符合RS-232标准的物理要求,RS-232发送器必须提供±5V的最小输出电压摆幅,但不能超过30V/μs的压摆率。这些限制通常将RS-232兼容通信限制在较慢的波特率和较短的线路长度下。但是,当需要更高的传输速率时,与RS-232标准相关的限制不应妨碍异步串行模式的使用。首先,ADI公司目前提供RS-232“兼容”(不兼容)收发器,能够进行兆波特™操作。有关MegaBaud RS-232兼容收发器的详细信息,请访问ADI公司网站(www.analog.com)。其次,多个微控制器和/或其他异步串行设备之间的点对点连接允许创建能够以更快的波特率进行通信的用户定义网络。此外,还有物理层协议(例如RS-422和RS-485)支持更远距离的高速异步串行通信。

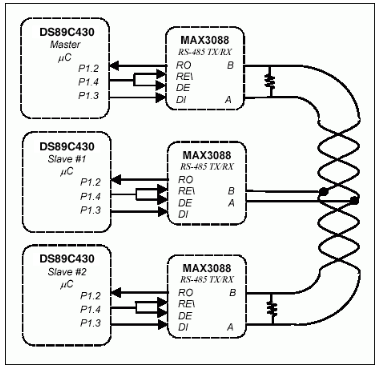

图4.使用硬件串行端口接口的RS-485网络示例。

上图显示了(485)个DS3C89微控制器之间的RS-430网络接口。异步串行模式使用 TXD 引脚进行传输,使用 RXD 引脚进行接收。这些引脚直接连接到RS-485收发器的DI(数据输入)和RO(接收输出)引脚。第三个微控制器端口引脚P1.4连接到DE(数据使能)和/RE(接收使能),并将用作半双工收发器的方向控制。网络使用主/从架构(1个主站,2个从站),其中每个从设备都有自己唯一的地址,在总线上传输之前必须首先由主设备寻址。所有器件均以 22.1184MHz 系统时钟频率运行,并使用定时器 1 产生 1.38M 波特率。生成此波特率所需的设置可在图后的表4中找到。

| 系统时钟(兆赫) | 外部晶体或时钟频率 (MHz) | 时钟乘法器模式² | 计时器 1 重新加载值 | ||||

| FB | 足球俱乐部 | FD | 铁 | FF | |||

| 7.3728 | 7.3728 | - | 92,160 | 115,200 | 153,600 | 230,400 | 460,800 |

| 10.0000 | 10.0000 | - | 125,000 | 156,250 | 208,333 | 312,250 | 625,000 |

| 11.0592 | 11.0592 | - | 138,240 | 172,800 | 230,400 | 345,600 | 691,200 |

| 14.7456 | 7.3728 | 2 倍 | 184,320 | 230,400 | 307,200 | 460,800 | 921,600 |

| 16.0000 | 16.0000 | - | 200,000 | 250,000 | 333,333 | 500,000 | 1,000,000 |

| 18.4320 | 18.4320 | - | 230,400 | 288,000 | 384,000 | 576,000 | 1,152,000 |

| 20.0000 | 10.0000 | 2 倍 | 250,000 | 312,250 | 416,667 | 625,000 | 1,250,000 |

| 22.1184 | 11.0592 | 2 倍 | 276,480 | 345,600 | 460,800 | 691,200 | 1,382,400¹ |

| 25.0000 | 25.0000 | - | 312,500 | 390,625 | 520,833 | 781,250 | 1,562,500 |

| 29.4912 | 7.3728 | 4 倍 | 368,640 | 460,800 | 614,400 | 921,600 | 1,843,200 |

| 32.0000 | 16.0000 | 2 倍 | 400,000 | 500,000 | 666,667 | 1,000,000 | 2,000,000 |

| 33.0000 | 33.0000 | - | 412,500 | 515,625 | 687,500 | 1,031,250 | 2,062,500 |

|

¹ 应用示例 #2 中使用的波特率。 ² 时钟乘法器用于说明,不需要生成这些系统时钟频率。 |

|||||||

代码示例:主代码

主器件初始化为发送器,并驱动其收发器的DE(/RE引脚)至逻辑高电平。发送从地址后,主机将收发器置于接收模式。从机接收到两个数据字节后,主机将收发器返回到其发送模式。如果在一定时间内未从寻址从站接收到两个数据字节,则主站使用 13 位定时器0 超时。在对另一个从站寻址之前,主站将从地址和接收的数据字节(或指示未收到响应)发送到串行端口0。

代码示例(续):从站#1,#2代码

从器件最初配置为接收器,驱动其各自收发器的DE、低电平RE引脚至逻辑低电平。两个从属微控制器都使用多处理器通信模式,以便将网络上的地址传输与数据传输区分开来。寻址时,从设备成为发射器,并通过发送两个数据字节来响应主设备。发送这些字节后,从站将收发器返回到接收模式,并开始监控网络的地址。

审核编辑:郭婷

-

深入剖析DS89C420超高速微控制器:性能、特性与应用全解析2026-04-01 599

-

高速性能之选:DS89C430/DS89C450超高速闪存微控制器深度解析2026-03-24 158

-

超高速微控制器硬件增强串口功能2023-02-21 1845

-

超高速闪存微控制器软件SPI2023-01-10 2083

-

超高速USB3.0主机和设备控制器接口应用方案2022-09-05 4486

-

超高速电机控制方式讨论2021-08-27 1281

-

USB 3.0超高速集线器控制器RTS54112021-08-02 2063

-

具有超高速控制的2MHz PWM 2A降压稳压器2020-08-10 1944

-

超高速大电流有源滤波器LDO控制器2020-03-19 2282

-

基于FPGA的超高速FFT硬件实现2009-06-14 7934

-

从高速微控制器系列向超高速闪存微控制器的升级2008-07-27 1359

全部0条评论

快来发表一下你的评论吧 !