了解PuISAR ADC支持电路

描述

Martin Murnane 和 Chris Augusta

逐次過近型(SAR)模数转换器(ADCs)使用了许多新技术来改善分辨率。了解这些器件的工作原理对于预防故障和错误很重要。本应用笔记将从一般意义上讨论使用SAR ADCs时易犯的错误,以及更重要地,如何预防这些问题。

PuISAR的工作原理

ADI公司PulSAR®系列ADC使用内部开关电容技术将SARADCs的分辨率扩展到18位。这意味着在CMOS工艺上,不需要进行成本高吊的薄膜激光调整。

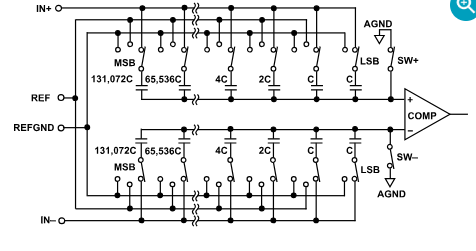

图1显示了AD7643的简化输入级。AD7643是一款18位ADC,转换速率可达1.25MSPS,它基于电荷再分配型数模转换器(DAC),这在较新式SAR ADCs中颇为流行。SAR算法需要两个阶段来确定ADC输出码。第一个阶段是采集阶段,SW+和ISW-最初是关闭的。所有开关均连接到IN+和IN-模拟输入,因此各电容用作采样电容,以在输入处采集模拟信号。第二个阶段是转换阶段,SW+和SW-是打开的。输入与内部电客断开,而作用于比较器输入上,这将导致比较器不稳定。从MSB开始,切换REF与REFGND之间元件阵列的各元件(这里将不详述SAR算法),使比较器重新回到平衡状态,由此将产生代表模拟输入信号的输出码。

图1. AD7643简化原理图

基准电压

在分析图1的基准电压部分时,我们将聚焦于使用PulSARADCs设计电路时易犯的错误。请注意,当计算输出码时,输人已与ADC的内部元件断开。这一点很重要, 它意味着在转换阶段,输入(IN+和IN-)上出现的任何噪声都不会影响所获得的输出码。

在转换阶段,REF引脚与内部开关电容结构相连,因为基准电压输入处没有采样保持电路。此处出现的任何噪声(在转换阶段)都会对输出码产生直接影响。如果因为在位检验期间噪声增加,致使其中一位设置不正确,例如第6位应当是0但被设置为1,则所有后续位将被设置为1,以将DAC输出降至正确的值。因此,输出计算将不正确,导致输出码低6位为一串1,这些位一般被称为“粘连位”(Stuck Bit)。为避免出现粘连位,采用一个极为稳定的基准电压至关重要。

可以使用哪种类型的精密基准电压?

在PulSAR数据手册“技术规格”部分中出现的-种误解是外部基准电压与耗用电流。通常,对于低采样率PulSAR(AD7685为250 kSPS),耗用电流值在数+μA范围内;对于较高采样率PulSAR(AD7621为3 MSPS),耗用电流值可达数百μA。这是平均电流,转换器输入驱动是由基准电压驱动电路提供ADC要求的最大电流。这可能是-FS或+FS,具体取决于ADC。实际上,任何基准电压都能提供数百μA电流,但有些基准电压在PulSAR高分辨率转换器中并不实用。

低功耗基准电压(ADR12x、ADR36x)

低功耗基准电压一般是不可接受的,因为在权重最高有效位(MSB)判断期间,它们通常缺乏能力建立。与相应的缓冲式基准电压(如AD780、ADR43x和ADR44x)相比,这些基准电压的输出阻抗通常较大。基准电压电路的动态部分基本上是一RLC储能电路,其中R位于ADC内部(一些串联开关电阻),C为基准电压储能或去耦电容,L为基准电压本身的电感。在L来自精密基准电压源(如AD780)的情况下,PulSAR ADC设计师选用某一组R和C。使用这些值的结果是:当系统被激励后(激励发生在位判断过程中),系统达到临界阻尼状态。如果使用电感高得多(比好的缓冲式基准电压高100倍以上)的低功耗基准电压,将导致RLC电路处于欠阻尼状态,从而引起上述粘连位行为。

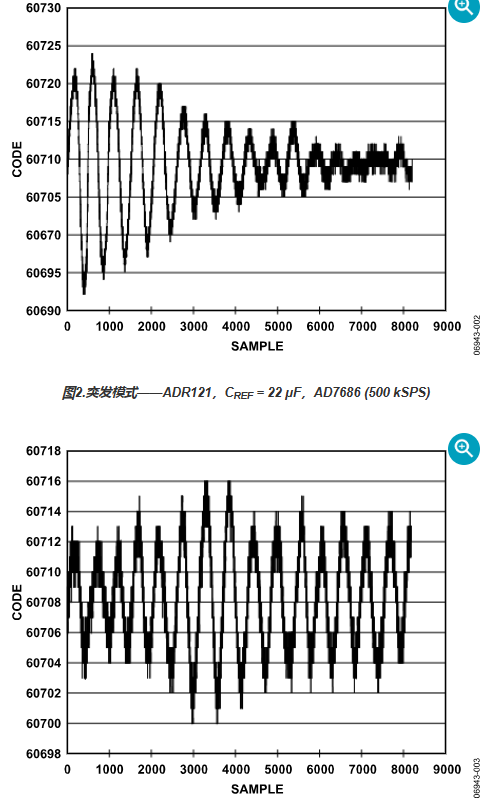

图2至图7显示了一些低功耗基准电压的表现。请注意,这些图中的术语“突发模式”是指这样一种模式,即转换控制信号保持非活动状态,直至采集到8192个样本之时才激活。这是对基准电压的最低要求,因为当ADC不进行转换时,基准电压中便不存在动态部分。我们使用了16位、500 kSPS PuISAR AD7686来获得图2至图7中的数据。

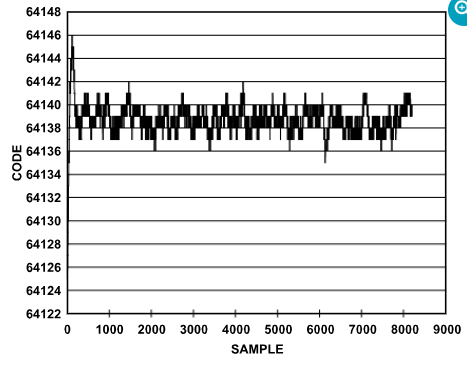

直流测量数据一般以柱状图形式显示,这对于显示码字跃迁(或跃迁噪声)及峰峰噪声非常有意义。不过,图2和图3则以时域显示,以证明被测试的基准电压在动态SAR转换期间不能建立这一理论。

图3.连续模式——ADRI21,CREF = 22 μF,AD7686 (500 kSPS)

图2显示了突发工作模式下欠阻尼RLC电路的经典范例。图3显示了连续模式范例。如这两幅图所示,此基准电压从未完全建立至16位性能。在连续模式下,峰峰输出码仍与AD7686数据手册中规定的性能相差约16采样数或约4倍。

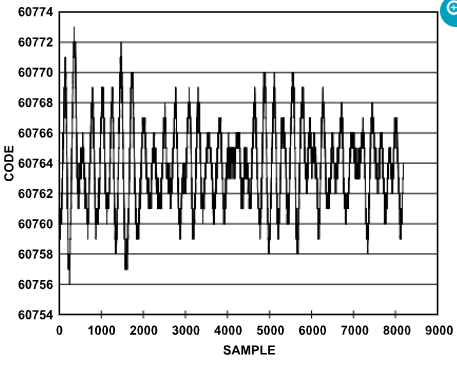

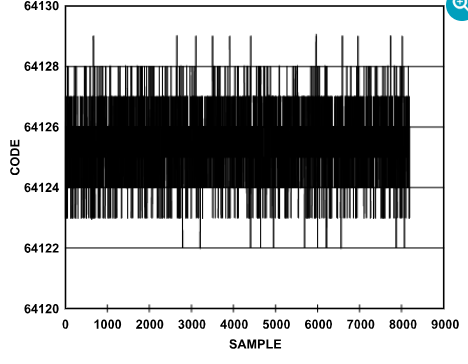

图4显示了使用ADR365时AD7686的性能。突发模式或连续模式对此基准电压而言并没有真正不同,因为它同样从未完全建立至16位性能。峰峰输出码同样比AD7686的额定性能大4倍左右。

图4. ADR365,CREF = 22 pμF,AD7686 (500 kSPS)

缓冲基准电压

几乎任何基准电压都可以使用适当的放大器(如AD8031或AD8605)进行缓冲,以便获得足够的驱动能力,因为此时较高带宽放大器的输出中存在动态部分。图5显示了把经过AD8301缓冲的ADR365作为AD7686的基准电压进行测试的输出。

图5.突发模式——ADR365, CREF = 22 μF,AD7686 (500 kSPS)

缓冲外部基准电压又会引发原来的功耗要求问题。较简单的解决方案是使用具有足够驱动的较佳基准电压,如AD780、ADR43x或ADR44x等。这种情况下可以使用任何低功耗基准电压,因为这些缓冲的串联电感(通常)都很低。一个缓冲可以用来驱动许多PulSARADC,因此这对多转换器系统很有用。此外,在多转换器应用中,最佳方法是使用星形结构的基准电压迹线,每个转换器使用其自己的基准电压储能电容。不建议从一组ADC中的第一个ADC开始进行菊花链连接,因为ADC基准电压可能会发生串扰。

低功耗基准电压(采样率小于10 kSPS)

在低功耗、较低采样率应用中(例如必须使用低功耗基准电压的10 kSPS或更低应用),可以在ADC的基准电压输出之间使用一个小串联电阻,如100。在突发工作模式下,为了让流过这个电阻的电流趋于稳定,最初几次转换可能需要丢弃。对于较高采样率,通常无法进行突发转换,因为需要丢弃的转换太多。此外,随着流过此电阻的电流增大到稳态值,此电阻上的压降在时域中表现为一个斜率,一般称其为基准电压下降。

图6显示了在500kSPS较高采样率应用中使用202串联电阻时的基准电压下降问题。请注意,最初几百次转换是在欠阻尼情况下,随着采样数增加,斜率表现为一个小的负值。

图6.突发模式——ADR365,CREF = 22 μF,串联电阻 = 20 Ω,AD7686 (500 kSPS)

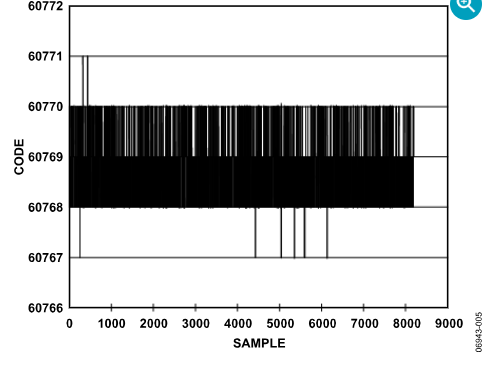

图7显示10kSPS较低采样率的情形。此时不存在欠阻尼问题,峰峰噪声为5采样数,在性能上与AD7686很接近。

图7.突发模式——ADR365,CREF = 22 μF,串联电阻 = 20 Ω,AD7686 (10 kSPS)

为什么要使用较大去耦电容?

选定适当的基准电压(或适当的基准电压与缓冲电路)后,查看缓冲(运算放大器)的数据手册,发现它建议避免使用大容性负载。但是,PuISAR ADC要求10 μF或更大的基准电压去耦电容(REF CAP)。 初看起来,这两个要求自相矛盾。

选定适当的基准电压(或适当的基准电压与缓冲电路)后,查看缓冲(运算放大器)的数据手册,发现它建议避免使用大容性负载。但是,PuISAR ADC要求10 μF或更大的基准电压去耦电容(REF CAP)。 初看起来,这两个要求自相矛盾。事实上,“去耦”这一术语有多种含义,用户看到的PulSARADC基准电压(REF)引脚上的10 μF电容与电源(VDD、AVDD、DVDD、VIO、 OVDD)上的其它10 μF电容并不是回事。REF上的电容不是旁路电容,而是SAR ADC的——部分,这个电容不适合放在硅上。在位判断期间,由于各位会在数十纳秒或更快的时间内建立,因此此处所示的储能电容(REF CAP,参见图8)是用来补充内部CDAC的电荷,从而与内部电容阵列上的电荷一起平衡比较器。随着二进制位加权过程的向前进行,将从此电容中不断提取少量电荷。当然,内部电容阵列只是其中(约为15 pF至60 pF,取决于ADC)的很小一 部分,但这些较大值储能电容需要满足SAR位判断建立时间要求。关于在位判断过程中电荷发生了什么事情等一些错综复杂的细节问题,这不属于本应用笔记的讨论范围。

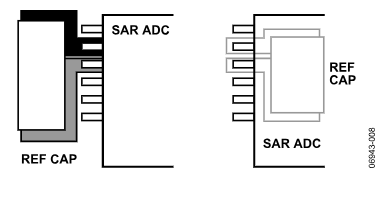

图8.基准电压电容位于SAR ADC同侧或位于PCB后侧

储能电容大小不足也会引起粘连位问题。电容的放置和类型同样很重要。为避免基准电压下降,需要使用等效串联电阻(ESR)低的电容。近年来,已经有非常好的陶瓷X5R介电电容可以在0603封装尺寸下提供10正容值。对于许多PulSAR ADC,通过降低某些性能要求,即微分非线性(DNL), 可以减小基准电压电容值。

布局

建议将一个电容直接放在ADC的基准电压引脚上,用来消除开关电容瞬变。要求使用高质量电容(例如钽电容或X5R型陶瓷电容,不推荐使用NPO电容),因为这是一个电荷存储电容,而不是旁路电容,电容值可以在4.7 μF至22 μF范围内。请注意,某些数据手册规定了开启建立时间,这表明REF引脚上使用了一个特殊基准电压电容。请参考相关PulSAR数据手册的“技术规格”部分以了解详细信息。

布局开始时,考虑具有SAR ADC器件的PCB布局,并考虑在ADC基准电压引脚上放置一个电容。首先将该电容放在这些引脚附近,然后将基准电压放在电容附近,最后放在放大器附近(参见图8)。

布局中还需要一条粗迹线,以减小电路中的阻抗。ADC的基准电压输入具有动态输入阻抗,意味着对此引脚的输入必须用低阻抗源驱动。请注意,如果基准电压是经缓冲进入REF引脚,则缓冲输出阻抗必须很低。这也同样适用于模拟输入引脚。

放大器选择

大部分PulSAR数据手册都对放大器做了详细说明。需要注意的一些主要问题是低噪声电平和低输出阻抗。输入信号建立时间也是一项重要参数,因此要求放大器具有高压摆率性能。符合这一要求的放大器有:ADA4841-1、AD8021、ADA4899-1、AD8099和ADA4941-1。

ADA4841-1和AD8021能驱动PuISAR ADC,具有高带宽和良好的压摆率,是出色的ADC驱动器选择。ADA4899-1也是不错的替代之选,具有出色的压摆率和良好的带宽,但需要消耗更多电流。还有其它放大器也适合各种应用,例如AD8099,它具有极低的噪声密度,因此适合18位ADC应用。但是,这款器件不是单位增益稳定型,虽然可以将其配置成单位增益稳定型,但它的电流消耗很高(16 mA)。不过,它具有一个(禁用 )功能,可以利用该功能减小电流消耗,以适合便携式应用。ADA4941-1是单端转差分应用的另一个选择,具有5 V输入电压,例如可用于PuISAR 18位ADC AD7982。

结论

了解SAR ADC的工作原理对于避免新设计中易犯的错误非常重要。本应用笔记所列出的问题在新设计中是很常见的。

审核编辑:郭婷

-

了解并延续∑-ΔADC的安全运行2023-11-23 415

-

了解模数(ADC)驱动器的功能2023-05-06 4596

-

了解PulSAR ADC支持电路2023-02-17 1984

-

你了解ADC吗jf_95215556 2022-07-31

-

一文了解Σ-Δ型ADC拓扑结构的基本原理2022-02-23 4399

-

MS-2124:了解高速ADC的交流行为2021-05-17 620

-

DN1013-了解时钟抖动对高速ADC的影响2021-05-11 878

-

利用您需要的支持导出受控ADC2021-04-22 540

-

AN-931: 了解PulSAR ADC支持电路2021-03-20 683

-

了解时钟抖动对高速ADC的影响2019-07-17 1608

-

高速ADC时钟抖动的影响的了解2017-05-15 1678

-

【绝对干货】高精度逐次逼近型ADC支持电路的设计和故障排除2015-08-25 6898

-

ADC外围电路设计方法2012-03-15 10066

-

ADC外围电路的设计2011-02-11 5332

全部0条评论

快来发表一下你的评论吧 !