RISC-V以评估ISA将如何继续发展

描述

随着RISC-V欧洲峰会的结束,本文将回顾各公司如何利用这次活动作为平台,展示他们利用开放指令集架构(ISA)的最新创新。这些创新既包括硬件也包括软件,对许多领域的设计师都很重要。

自2015年发布以来,RISC-V一直是一个开放的标准,支持自定义硬件和软件创新。ISA使用预先存在的知识来加速开发,并在设计过程中提供改进的灵活性。

RISC-V欧洲峰会的三个亮点可以为不需要在架构的最低级别操作的设计人员提供新的抽象层。本文将介绍峰会上的这些亮点,并讨论每个创新如何为设计师提供工具,使开发更简单,同时缩短上市时间。此外,我们将研究不断发展的RISC-V生态系统,以评估ISA将如何继续发展。

自定义矢量核

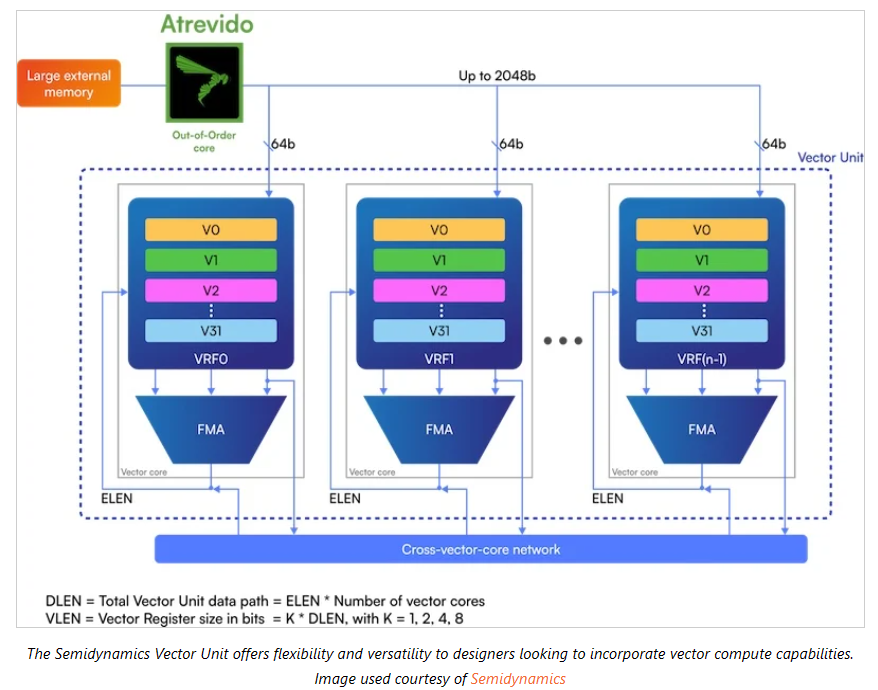

为了迎接RISC-V欧洲峰会,Semidynamics发布了“最大的、完全可定制的”矢量处理RISC-V处理器。随着矢量计算在人工智能或计算机视觉应用中变得越来越重要,硬件矢量支持可以成为许多开发人员在高性能系统上工作的宝贵设计工具。随着RISC-V国际公司2021年的矢量扩展,预计ISA的矢量处理将随着需求而增长。

Semidynamics的矢量单元是可定制的,用来适应应用程序的需求,允许设计人员根据需要定义数据路径长度,矢量长度或数字格式。同时在单个单元中集成了4到32个矢量内核,即使是计算最密集的应用程序也可以使用其矢量单元。矢量单元与Atrevideo和Avispado RISC-V内核一起提供,展示了RISC-V ISA的多功能性。

RISC-V矢量加密

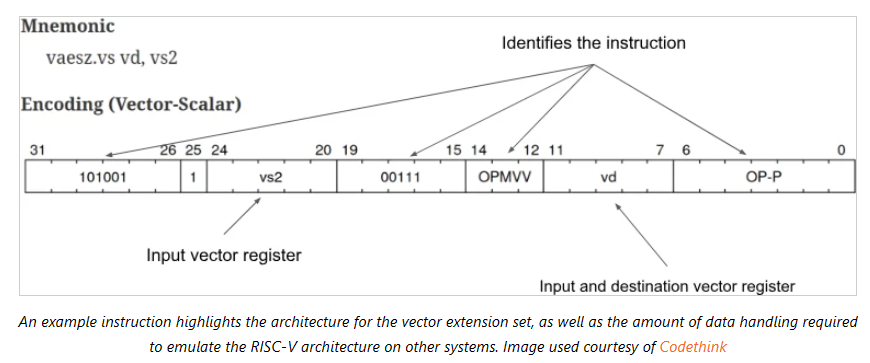

随着硬件矢量可用性的提高,Codethink已经将RISC-V矢量加密扩展集全面集成到仿真软件QEMU中。虽然仿真可能不是实现矢量加密设计的直接要求,但它是RISC-V规范中的要求。

基于过去在RISC-V设备上的经验,Codethink在QEMU模拟器上的开发最终将使矢量加密技术更接近RISC-V标准化。

软件定义芯片

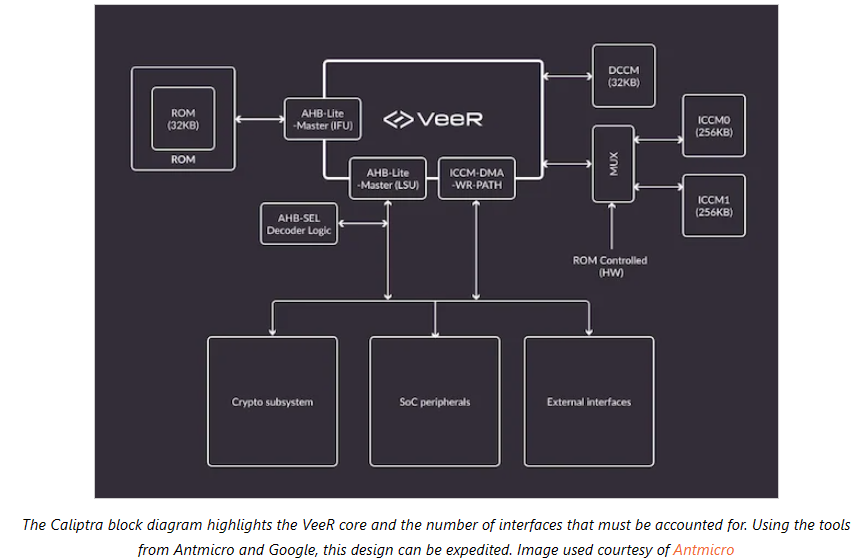

一些芯片联盟成员,包括AntMicro和谷歌,提出了改进的数字设计工具,用于使用RISC-V内核的集成。这些工具(Verible和Kythe)可以与高效的RISC-V (VeeR)核心家族一起使用,以简化设计过程,并允许在组织内部和组织间的工作中进行开放协作。

这些在Caliptra项目中得到了突出体现,该项目利用VeeR核心家族提供现代处理器所需的安全性。除了设计和验证工具之外,Antmicro还提供了一个视觉系统设计器,让人们相信很快可以在RISC-V设计器体验到一个新的抽象层次。

High-level RISC-V

虽然RISC-V欧洲峰会讨论了更多的发展,但本文中的发展代表了RISC-V处理器增加可用性和市场份额的趋势,设计RISC-V处理器可能很快就会成为一项更容易的任务。

随着软件和硬件的创新,如视觉系统设计、矢量核心支持或专用的RISC-V模拟IP,高级开发和集成的新机会似乎即将到来。除了降低进入RISC-V生态系统的门槛之外,这也从另一方面印证了RISC-V趋势不可阻挡。

审核编辑:刘清

-

RISC-V有哪些优缺点?是坚持ARM方向还是投入risc-V的怀抱?2024-04-28 2274

-

risc-v的发展历史2024-07-29 1644

-

为什么选择RISC-V?2020-07-27 5004

-

RISC-V ISA是怎样进行命名的2021-12-09 1692

-

RISC-V基础知识:模块化开放式的ISA CISC和RISC代码区别2022-12-23 2239

-

RISC-V简介2023-02-27 1345

-

risc-v是什么意思2023-03-30 2200

-

RISC-V架构2023-04-03 2012

-

RISC-V 发展2023-04-14 1067

-

方之熙博士任命RISC-V基金会主席,热切关注加速中国RISC-V ISA应用2018-11-08 9158

-

RISC-V ISA 命名规范2021-11-26 1431

-

什么是RISC-V,RISC-V与其他ISA有何不同?2022-12-27 5849

-

RISC-V,迎来新创新2023-06-13 1268

-

ISA ARM 对比 RISC-V2024-09-10 2984

-

大湾区RISC-V生态全景展示:RISC-V生态发展论坛、开发者Workshop和生态应用专区2025-10-13 720

全部0条评论

快来发表一下你的评论吧 !