低静态功耗PS7A20 LDO芯片设计

电源/新能源

描述

今天和大家分享一颗低静态功耗的LDO芯片-TPS7A20相关知识分享。 TPS7A20是TI公司的一颗超低噪声的一颗LDO,有人问过我为何LDO输出能力这么小,还有人用,原因就是选择一颗芯片的指标不仅仅是其某一方面的能力,而是尽可能低成本满足设计的需要,LDO的成本较低,而且输出纹波较小,而且静态功耗低,特别适合于很多不需要较大电流的应用电路,在一些小型且有低功耗要求的控制器上面使用较多。 1,LDO芯片TPS7A20的主要特点: (1)低输出噪声,可实现低于7μVRMS的水平. (2)6.5uA的静态功耗。 (3)输入电压范围相对窄一些,仅为1.6V-6V,不过对于5V,3,3V系统也够用。 (4)输出电压范围为0.8V-5V,精度为1,5%。 (5)封装可选,最小可达0.616mm方形BGA封装,可减小产品尺寸。 (6)具有独立的EN引脚,可以控制输出和关断。 2.芯片的应用场景:

可用于消费类电子,如平板电脑,手机等,IP网络设备,便携式医疗设备,智能电表和可穿戴设备等。

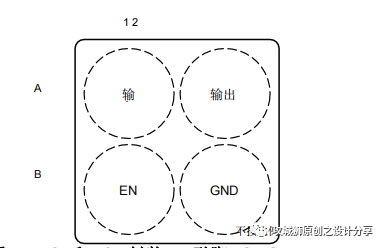

3.TPS7A20的引脚定义和设计参数【BGA封装】

A1: 芯片的电压输入引脚,建议放置一个100nf陶瓷电容滤波。 A2: 芯片的输出引脚,推荐使用低ESR电容,PCB靠近输出引脚放置。陶瓷电容或者钽电容均可,尽量避免使用电解电容。 B1: 芯片输出使能引脚,高电平打开输出,低电平关闭输出。如果有上电时序控制,可以通过控制这个EN引脚实现。 B2: 接地引脚,GND,要可靠接地。 【SOT23封装】

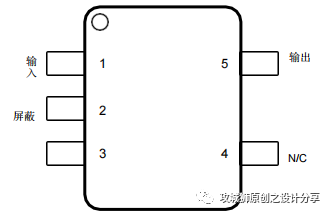

PIN.1: 芯片的电压输入引脚,建议放置一个100nf陶瓷电容滤波。 PIN.2: 芯片输出使能引脚,高电平打开输出,低电平关闭输出。如果有上电时序控制,可以通过控制这个EN引脚实现。 PIN.3: 接地引脚,GND,要可靠接地。 PIN.4:空 PIN.5: 芯片的输出引脚,推荐使用低ESR电容,PCB靠近输出引脚放置。陶瓷电容或者钽电容均可,尽量避免使用电解电容。

设计指导:

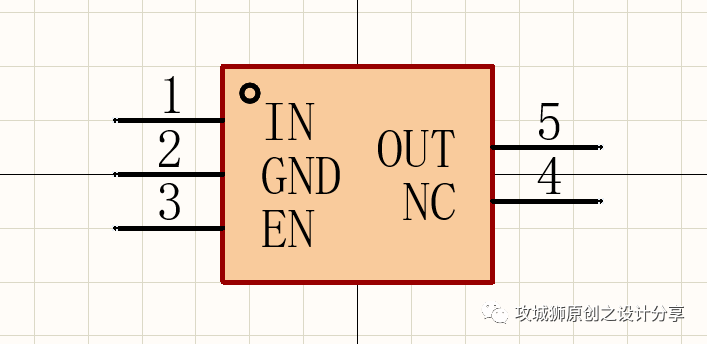

在使用这课LDO还要关注一些不易关注的点: (1)关注输入电压是否干净,如果高于6V的输入,可能会损坏芯片。 (2)选型时关注这可芯片的最小压降,也就是输入和输出最低电压差,根据求选择。 (3)关注芯片的热性能,LDO体积小带来的散热性能会需要额外关注(热阻计算不会算的去搜索一下我前几天发布的热阻计算方法-硬件设计之芯片热分析知识分享与应用) (4)在使用芯片时,打开和关闭输出都是需要时间的,尽量不要频繁去开关芯片的输出。 (5)输入输出要有电容滤波,且布局要靠近芯片的引脚放置。 (6)如果不是特别要求尺寸,还是建议使用SOT23-5封装。 (7)关注一下芯片的交期,量产以后买不到芯片比什么都难受,懂的都懂。 4.TPS7A20的原理图和PCB封装【SOT23-5封装为例】 原理图封装:

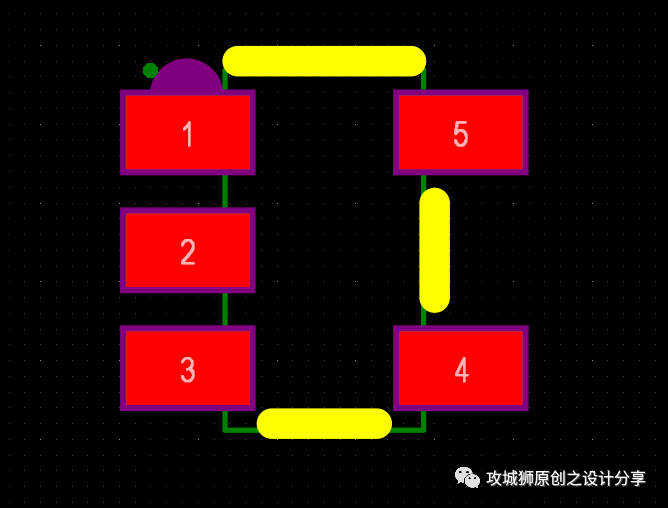

PCB封装:

编辑:黄飞

-

150mA输出,低静态电流电压可选LDO MIC53042019-03-07 1912

-

150mA输出低静态电流电压可选LDO MIC53042019-03-11 2067

-

噪声最低的SOT-23 LDO具有20μA静态电流,20μVrms噪声2019-05-16 1726

-

3A静态电流LDO的LT30092020-03-06 2898

-

MCP1703A低静态电流LDO稳压器的典型应用2020-05-25 1640

-

20V转5V,20V转3.3V,20V转3V的降压芯片和LDO芯片2020-10-15 1360

-

DN220-最低噪声SOT-23 LDO静态电流为20µA,噪声为20µVrms2021-04-27 748

-

300 mA、超低噪声、低 IQ、高 PSRR LDO TPS7A20数据表2024-02-29 620

-

300 mA、超低噪声、低IQ、高PSRR LDO TPS7A20数据表2024-03-25 574

-

技术资料#TPS7A20U 75mA、超低噪声低 IQ高 PSRR 低压差 (LDO) 线性稳压器2025-02-26 1153

-

TPS7A20 具有高 PSRR 的 300mA 超低噪声、低 IQ 低压差 (LDO) 线性稳压器数据手册2025-02-28 1380

-

Texas Instruments TPS7A20U低压差 (LDO) 线性稳压器数据手册2025-07-21 994

-

Texas Instruments TPS7A20C低噪声LDO线性稳压器数据手册2025-07-22 981

-

Microchip TC1302A/B:低静态电流双输出LDO的卓越之选2026-03-15 553

-

MIC5236:低静态电流μCap LDO稳压器的卓越之选2026-03-31 249

全部0条评论

快来发表一下你的评论吧 !