信号完整性之时域和频域学习

电子说

描述

时域和频域

广义上讲,信号完整性是指在电路设计中互连线引起的所有问题,它主要研究互连线的电气特性参数与数字信号的电压电流波形相互作用后,如何影响到产品性能的问题。主要表现在信号反射、串扰、开关噪声、地/电源弹、损耗、容性负载、电磁干扰等因素对信号质量以及总线时序的影响。

低速系统中这些问题并没有表现出来,而到了高速系统我们将不能忽视这些信号完整性问题了。

所有这些信号完整性问题都会在信号的时域波形上有所体现,比如说由反射产生的过冲、振铃、边沿不单调等,以及由损耗产生的码间干扰、由容性负载导致的信号边沿变缓等问题。一些问题我们可以通过结合PCB布线来分析时域的波形使问题得以解决,但总有一些问题从时域入手可能并不会有很好的效果,这个时候就需要引入频域的分析。

我们可以这样 理解频域 ,它只是一种数学构造并不是真实存在的,但频域却为解决一些SI问题提供了便捷。在射频以及高速数字设计中会非常频繁的通过频域手段来解决产品设计中的问题,掌握好频域的分析方法非常重要。由数字信号处理方面的知识可以知道频域中唯一存在的波便是正弦波,而之所以在频域中使用正弦波是因为任何时域波形都可以用正弦波来合成,并通过傅立叶变换转换到频域。

例如,一个周期为T(=2π/ω)的周期函数。由傅立叶级数的知识我们知道它可以用一系列以T为周期的正弦函数An*sin(nωt + ϕn)组成的级数来表示,记为:

f(t) = A0 + ⅀(n=1,∞)An*sin(nωt + ϕn),

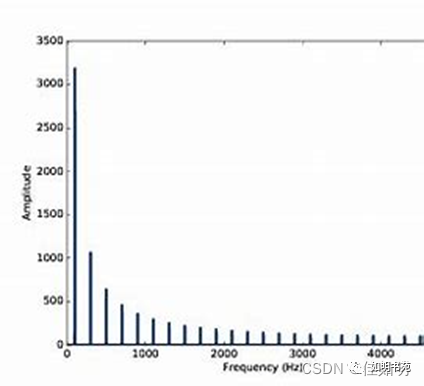

其中,A0、An、ϕn都为常数,ω表示交频率,ϕn表示相位。在工程上我们把这种展开叫做谐波分析。其中,A0称为f(t)的直流分量;A1sin(ωt + ϕ1)为f(t)的一次谐波(又叫做基波);而A2sin(2ωt + ϕ2)、A3*sin(3ωt + ϕ3),…依次为二次谐波、三次谐波,等等。这样我们就把时域中的数字信号分解成直流分量、基波以及多次谐波分量,而每一个谐波分量都是频率为基波整数倍的正弦波。在频域中仅仅用一个点就可以描述一个频率的正弦波的所有信息(频率、幅度、相位),这样就成功将时域信号转换到频域。我们把正弦波的频率分量及其幅度的集合称为频谱。

理想方波的频谱

同样也可以通过将频域上的谐波分量转化到时域从而重构时域的波形。重构时域波形时所包含的频域分量越多所得到的时域波形越接近真实的数字信号。当然要想得到完全真实的信号波形是不可能的,我们无法将所有频域分量集合来重构信号波形,信号完整性分析往往需要考虑精度和效率的平衡。

不同频率分量叠加所形成的时域信号

总结一下,

- 时域,是真实存在的域;

- 一种数学构造,便于分析解决问题;

- 频域中唯一存在的波便是正弦波;任何时域波形都可以用正弦波来合成并通过傅立叶变换转换到频域。

信号的带宽

说到这里我们需要介绍一下带宽的概念。我们引入频域的概念是找到解决互连过程中出现的信号完整性问题的捷径,通过带宽这一频域概念就可以很好的将信号特性和传输信号的无源传输通道的特性结合起来,同时也可以将时域的信号特性和频域的参数指标结合起来形成一个系统的信号完整性分析方法。

实际上并不存在理想的方波,一个数字信号完成从0到1或者从1到0的跳变都需要一定的时间,即边沿的上升下降时间。数字信号的频谱永远都是低次谐波包含的能量要占绝大部分,也就是说越是高次谐波所包含的能量越小,对从频域到时域重构信号波形的贡献越小,能量小到一定程度我们就可以将后面的更高次谐波忽略。我们将这个临界的谐波分量称为有效的最高正弦波频率分量。

怎样界定“有效”?通常通过和理想方波的相同谐波做比较来确定。当该谐波的能量不小于理想方波相应频率谐波能量的50%,也就是幅度不低于理想方波相应频率谐波70%时,我们才认为该谐波是“有效的”。

时钟信号频谱

信号的带宽(BWsignal)用来表示数字信号频谱中有效的最高正弦波频率分量,是为了充分近似时域波形特征所需要包含的最高的频率分量,所有高于带宽的频率分量都可以忽略不计。

对于数字信号来说,信号的边沿越陡,合成其时域波形所需使用的谐波分量就越多,也就是说频谱所包含的有效谐波次数越高,即信号的带宽越高;相反信号的边沿越缓,合成其时域波形所需使用的谐波分量就越少,也就是说频谱所包含的有效谐波次数越低,即信号的带宽越低。也就是说信号的带宽与信号上升下降时间有关。我们在研究、解决信号完整性问题时通常只关注信号的自身带宽内的频谱即可,超出带宽的频谱范围对信号时域波形影响是比较小的,我们认为可以忽略其影响。

** 带宽的概念就把信号的时域特征和频域特征联系在了一起。带宽和上升时间的关系如下:**

BW=0.35/Trise,

其中,BW表示信号带宽,Trise表示信号20%-80%上升时间。很多器件输出buffer给出的都是10%~90%上升时间,此时带宽BW = 0.5/Trise。需要注意这里介绍的带宽和上升时间的关系为经验公式,在实际的设计中最好能够留出一定的裕量。

有的书中对带宽还有另一种表述,叫做转折频率Fkeen 。

- Fknee =0.5/Tr( 10%--90%上升时间)

- 在DC ~ Fknee范围内的频率成分能量以-20dB/10倍频程速度下降;

- 高于Fknee后,能量下降速度急剧增大;

- Tr越小,Fknee越高;

- Tr越大,Fknee越低.

这个转折频率其实和带宽的概念并不冲突,可以说就是带宽。只不过在计算带宽和转折频率时用的Tr取值不同,带宽是用的20%--80%上升时间,而转折频率用的是10%--90%上升时间。带宽这个概念也比转折频率更通用。因此,在后面的介绍中我们都使用带宽这个概念。

对于实际的数字信号,驱动器发出的信号可能是比较完好的,有自己的带宽。但随着其在互连线上传输就会受到了互连线的影响,就一定会表现出信号的失真。此时其带宽就不能简单由上升时间计算得到了。下图所示,存在过冲、振铃的信号高频分量的能量明显要比没有振铃情况的信号高频分量包含的能量要高。

过冲和振铃对信号频谱的影响

在有振铃的情况下信号的带宽约等于振铃频率,振铃的频率往往要比信号本身的频率以及带宽都要高很多。振铃增大了信号频谱中的高频能量,这些高频能量很可能是非常危险的,很可能会增加对相邻信号的串扰、导致产品的EMI辐射超标。

因此,在产品的设计中往往都是尽量优化传输通道,降低振铃、过冲这些信号的失真。振铃、过冲这些失真往往是由于信号传输链路上存在阻抗突变点、或者驱动器阻抗和传输线阻抗不匹配从而产生反射导致的,消除振铃的方法就是对传输线进行阻抗控制以及在驱动器和接收器上采用必要的匹配策略来消除反射。

-

什么是信号的时域和频域?2025-06-03 3992

-

信号完整性分析-时域与频域2023-09-28 4194

-

信号完整性设计测试入门2023-09-21 3297

-

如何将频域和时域建立联系方便的分析解决信号完整性问题?2023-06-14 3012

-

利用时域和频域巧解信号完整性/电源完整性的问题2023-05-14 2466

-

何为信号完整性?信号完整性包含哪些2021-12-30 2877

-

信号完整性与电源完整性的仿真2021-09-29 1649

-

电子书下载|《信号完整性与电源完整性分析》——高速PCB人员的必备书籍,EMI经典之作2019-11-13 4842

-

高速电路常用的信号完整性该怎么测试?2019-08-26 2830

-

常用信号完整性的测试手段和实例介绍2019-06-03 2276

-

信号完整性测试与仿真2017-11-22 5951

-

【下载】《信号完整性与电源完整性分析》——高速PCB人员的必备书籍,EMI经典之作2017-08-08 68513

-

信号完整性与电源完整性仿真分析2011-11-30 2109

-

常用信号完整性的测试手段和在设计的应用2009-06-30 1037

全部0条评论

快来发表一下你的评论吧 !