介绍一下基于带宽的信号完整性分析方法

电子说

描述

信号完整性分析的两个维度--时域和频域,而带宽是连接时域和频域的桥梁。同样,带宽也将信号的特性、传输通道、测试设备联系在一起,可见带宽是信号完整性分析中非常重要的一个概念。这一节就为大家介绍一下基于带宽的信号完整性分析方法。

设计目标

我们面对一个SI分析项目,首先我们要通过对系统方案的了解以及datasheet的阅读等渠道知道待分析的信号的特征:

- 是什么类型的接口,DDR还是Serdes?

- 数据速率有多高?

- 驱动器和接收器的电平标准?

弄明白这些问题,我们就大概知道信号的带宽,就能够对无源通道的设计提出具体明确的要求;我们也能驱动器和接收器的信号质量、时序的需求,也就能够正确的判别时域仿真结果是否能够满足要求。

此外就是获取芯片厂家提供的仿真模型,为时域的电路仿真做准备。一般来说厂家的模型无论是IBIS还是Spice模型都是和信号带宽相匹配的,我们是可以放心使用的。

确立设计目标的过程其实也是为后续的频域建模和时域的仿真做准备的过程。

建立模型

** 建模其实是一个频域分析的过程。

**

对于无源链路需要工程师借助仿真软件进行建模。

第一,建模的过程中必须保证模型的准确度,也就是模型必须能够准确地反映了无源链路的真实特征。这就要求SI工程师能够根据所设计的总线接口的特性选择合适的软件工具(2D、2.5D、3DEM工具)以及仿真建模方法(hfss建模端口的设置为lumped port还是wave port、设置在什么位置)。

第二,无源链路的性能要能够满足信号带宽的要求。SI工程师需要通过对模型进行仿真优化使模型在信号的带宽范围内具有良好的损耗和反射性能,如果无源链路的性能不能满足要求,工程师就需要对无源链路的材料或者结构进行调整以提高模型带宽。

通常情况下,对于DDR等并行总线并没有对无源通道的频域特性给出特殊的要求,只给出了信号质量的要求(眼图、过冲等)。因此这一步可以省略,直接进行时域电路仿真,如果信号质量不满足要求再回过头来优化传输通道以及芯片的OCD、ODT的配置。

对于Serdes接口,比如PCIe、Ethernet等接口的spec中都定义了插损(insert loss)、回损(return loss)等无源通道的指标。我们就需要根据这些指标对无源channel进行优化直到满足Spec要求为止。

第一点就是保证模型的准确,保证使用这个模型进行仿真的结果和实际测试结果的偏差可控。第二点包含的意思就是我们需要通过对无源链路的优化来达到信号完整性最优的效果。

如果无源链路的模型带宽太低会出现什么情况呢?

为了解释这个问题,我们再来看一下带宽的计算公式:BW= 0.35/Trise,

可以导出Trise = 0.35/BW。应用在互连线模型中,Trise就代表了互连线的本征上升时间。互连线的带宽为1GHz,那么它能传输信号的最短上升时间就是350ps,这个350ps就是这条互连线的本征上升时间。驱动器输出一个上升时间为Trise_drv的信号输入到一条本征上升时间为Trise_interconnect的互连线,在接收器处接收到的信号上升时间为Trise_rev,则有如下关系:

不难看出,由于互连线的本征上升时间导致接收器接收到的信号上升时间Trise_rev相对于Trise_drv增大了,我们通常也说信号经过互连线传输之后发生了边沿退化。如果互连线的带宽太低,其本征上升时间就会比较长,那么接收器接收到的信号上升时间就会比较大,也就是说信号在传输过程中发生的边沿退化就越严重。

仿真分析

通过前面两个步骤我们已经准备好了驱动器和接收器的仿真模型,也对无源通道进行了建模,那么我们就可以搭建出完整的时域仿真电路。

时域仿真分析就是在无源模型上加入激励源进行仿真从而观测时域仿真结果。对于信号完整性仿真将芯片的有源模型(IBIS、Spice或者AMI模型)、传输路径的无源模型搭建成仿真电路,在驱动器端添加激励在接收器端直接观测信号波形和眼图,并对仿真结果进行分析。对于电源完整性则需要加入电流负载以及VRM模型仿真观测负载端的电源噪声。有些情况下无法获取芯片的电流模型,此时就不能进行精确的电源完整性时域仿真,此时要求PI频域仿真有足够的裕量,时域仿真也是可以缺省的。

我们需要知道,时域仿真结果是SI的最终评判标准,时域仿真分析目的有两个:

一是更加直观地判断信号、电源质量是否满足要求;

二是确定芯片buffer选型、加重、均衡等各项参数配置为后续测试调试工作提供参考。

测试验证

测试验证是在产品生产完成后,在实际的系统中进行信号质量测试。测试验证的目的有两个,一是验证接收端信号质量是否满足要求;二是与前期的仿真结果进行对比进行差异分析,优化仿真建模方法。

测试仪器会对测试结果产生影响。对于高速信号的测试要选择带宽高、本征上升时间最够小的探头。

测试验证要得到正确的测试结果需要注意以下事项:

- 根据信号带宽选择合适的示波器和探头;

- 测试点位置选择需靠近接收芯片管脚,往往选择PCB上的过孔。但我们选择的测试点并不是芯片实际的接收端,因此测试波形会受到封装内部布线的影响。此时需要使用“去嵌入”技术消除封装内部布线的影响。

**基于带宽的SI设计流程

**

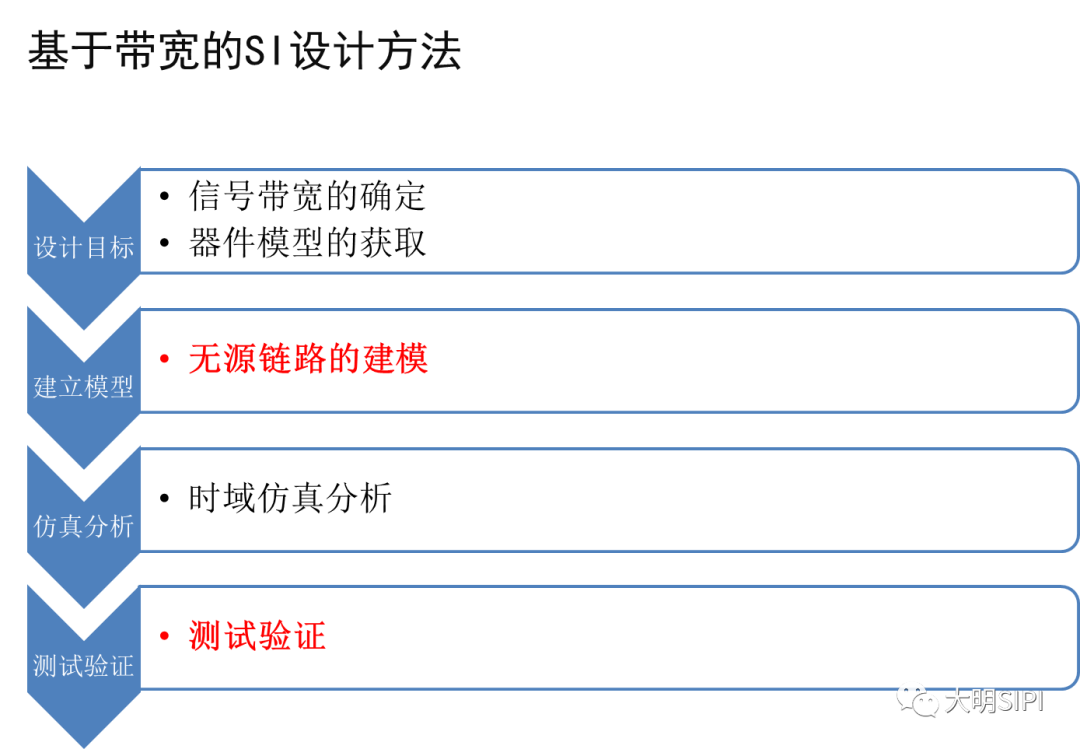

基于面的介绍,我们这里对信号完整性分析设计流程进行归纳总结,整个过程大体可分为前期准备(确定设计目标、获取模型)、无源链路建模、时域仿真分析、测试验证四个环节。其中前期准备是基础、无源链路建模和时域仿真分析是核心、并通过测试验证形成闭环。后续篇幅会针对高速并行总线、高速串行总线的信号完整性、以及电源完整性设计详细介绍设计流程。

-

信号完整性与电源完整性-电源完整性分析2024-08-12 3511

-

信号完整性分析科普2023-08-17 9345

-

什么是信号完整性!信号完整性分析2017-11-03 88753

-

【下载】《信号完整性分析》2017-09-19 25558

-

电地完整性、信号完整性分析导论2016-02-22 1453

-

信号完整性与电源完整性的仿真分析与设计2015-01-07 7138

-

高速信号的电源完整性分析2012-08-02 3643

-

高速电路信号完整性分析与设计—高速信号完整性的基本理论2012-05-25 2133

-

信号完整性与电源完整性仿真分析2011-11-30 2159

-

2011信号及电源完整性分析与设计2010-12-16 3589

-

信号完整性原理分析2009-11-04 1312

-

基于信号完整性分析的高速数字PCB的设计方法2008-06-14 5983

全部0条评论

快来发表一下你的评论吧 !