远程等离子体选择性蚀刻的新途径

电子说

描述

引言

为了提供更优良的静电完整性,三维(3D)设计(如全围栅(GAA)场电子晶体管(FET ))预计将在互补金属氧化物半导体技术中被采用。3D MOS架构为蚀刻应用带来了一系列挑战。虽然平面设备更多地依赖于各向异性蚀刻,但是3D设备在不同材料之间具有高选择性,需要更多的各向异性蚀刻能力。

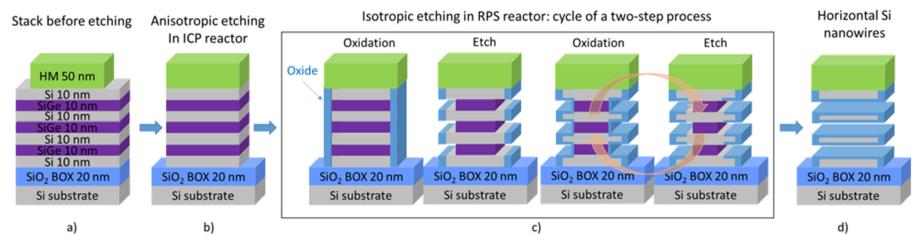

图1描述了一种制造GAA器件水平堆叠纳米线的典型方法。它使用了在绝缘体(SOI)衬底上的硅,并通过外延生长产生一堆Si/SiGe超晶格。这个工艺可能需要通过Si选择性或SiGe选择性各向同性蚀刻能力,来分别设计隔离的SiGe或Si纳米线。本文更具体地研究了SiGe的选择性和各向同性蚀刻用以制造Si纳米线。

图1:GAA器件用堆叠硅纳米线的制备方法

实验与讨论

叠层的各向异性构图由几个等离子体步骤组成:首先使用CF4等离子体工艺打开SiO2 HM,然后使用O2等离子体去除剩余的抗蚀剂,最后,使用HBr/Cl2/He-O2等离子体工艺对各向异性蚀刻Si/SiGe进行多层叠层。在此步骤之后,SiGe层可用于在RPS反应器中进行的各向同性蚀刻。

暴露于NH3/ NF3/O2 RP的Si和SiGe膜的蚀刻动力学表明,在膜被蚀刻之前有一段时间的流逝(图1)。该延迟对应于远程等离子体反应的中性粒子吸附在表面,然后与底物发生反应。

硅上的孵化时间(22秒)比硅锗上的孵化时间(4秒)要长,一旦该延迟过去,SiGe蚀刻速率是138 nm/min的常数。关于硅膜,观察到约60秒的瞬时蚀刻状态,在此期间,以约13.3纳米/分钟蚀刻硅,然后在稳定状态下,硅蚀刻速率减慢至3.9纳米/分钟。

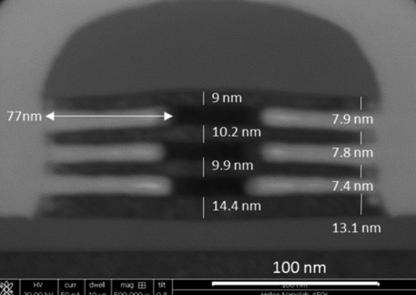

通过四个循环的氧化/蚀刻步骤,经过RP选择性和各向同性过程后的图案化Si/SiGe异质结构的扫描透射电子显微镜(STEM)图像显示了实现高选择性蚀刻的潜力(图2)。

图2:异质结构STEM图像

结论

英思特提出了使用RPS工艺来实现选择性蚀刻的新路线。它包括循环表面处理步骤和蚀刻步骤的两步工艺。这个概念是受到原子层沉积(ALD)领域中已经进行的选择性沉积的启发。ALD目前的趋势是将分子直接化学键合到表面,以抑制反应位点,然后阻止ALD前体分子之间的进一步反应。通过选择性地使存在的材料表面功能化,从而可以获得选择性沉积。

江苏英思特半导体科技有限公司主要从事湿法制程设备,晶圆清洁设备,RCA清洗机,KOH腐殖清洗机等设备的设计、生产和维护。

审核编辑 黄宇

-

金属蚀刻残留物对对等离子体成分和均匀性的影响2022-05-05 1599

-

等离子体蚀刻和沉积问题的解决方案2022-05-19 2649

-

PCB多层板等离子体处理技术2013-10-22 2621

-

PCB电路板等离子体切割机蚀孔工艺技术2017-12-18 3156

-

PCB板制作工艺中的等离子体加工技术2018-09-21 2977

-

微波标量反射计可测量大范围的等离子体密度2019-06-10 1579

-

低温等离子体废气处理系统2022-04-21 12444

-

TDK|低温等离子体技术的应用2022-05-17 3150

-

等离子体应用2022-05-18 3815

-

低温等离子体技术的应用2023-02-27 2151

-

载体晶圆对蚀刻速率、选择性、形貌的影响2023-05-30 1670

-

真空等离子清洗机的制造商正在引入氧和氢等离子体来蚀刻石墨烯2022-06-21 1676

-

铝等离子体蚀刻率的限制2023-06-27 1467

-

什么是电感耦合等离子体,电感耦合等离子体的发明历史2024-09-14 3588

-

等离子体的定义和特征2024-11-29 8867

全部0条评论

快来发表一下你的评论吧 !