介绍一些信号完整性常用存储接口的电平标准

存储技术

描述

内存在一个系统中的作用相当于一座桥梁,用以负责处理器与诸如硬盘 、主板、显卡等设备进行数据交换。可以说内存的容量和数据吞吐量从很大程度上就决定了一个系统的性能。今天介绍一些常用的存储接口的电平标准,包含HSTL、SSTL和POD等等。

HSTL电平

HSTL(High – speed Transceiver Logic)、SSTL (Stub Series Terminater Logic)电平都是应用于存储器接口的单端信号电平,它们的输入输出结构都有很大的相似之处。HSTL电平应用于大部分SRAM以及QDR、QDRII SRAM高速存储器接口,支持工作频率一般都在200MHz以上。

工作电压

HSTL电平的输出是反相器结构,输入是差分结构其中一个输入端接输入信号另一个在芯片内部连接到外部由用户提供的参考电压上。HSTL工作需要四个电压:

1.HSTL芯片的功率供电电压VDD。VDD电压并没有在JEDEC规范中明确指出不同的芯片可能会不同,3.3V、2.5V或者1.8V、1.5V都有可能。

2.芯片输出buffer供电电压VDDQ,JEDEC规定了HSTL电平的VDDQ典型值为1.5V这就决定了其输出电压的摆幅0~1.5V。

接收器buffer的参考电压VREF。通常情况下VREF电压为VDDQ/2 = 0.75V,但是由于HSTL输出buffer种类的不同、采用端接方式不同,VREF电压也会不同。参考电压VREF作为输入信号的判别标准,HSTL电平的VIH的最小值和VIL的最大值都是依据VREF设定的,因此VREF电压对噪声要求非常严格一般需要控制在1~2%以内。

接收端的端接电压VTT。VTT电压并非是必须的,对于数据信号芯片内部可能已经集成了片上端接,对于地址控制线在拓扑结构简单的情况下完全可以只用源端匹配或者直连的方式实现。

HSTL电平的四个工作电压

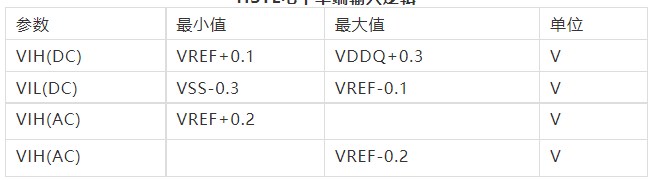

HSTL电平的输入逻辑

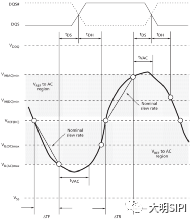

HSTL的单端输入逻辑电平定义了AC和DC两个值,AC规范在DC规范外面100mV。这种定义对于高增益差分接收器是非常重要的。AC限值表明了接收器必须满足的时序规范电平,即只有信号的边沿超过了AC的限值才会被认为是有效电平。DC电平的意义就在于清晰的定义最终的逻辑状态,也就是说信号在维持稳定电平时只有高电平不跌落到VIH(DC)的最小值以下、低电平不超过VIL(DC)的最大值就能够保证接收器能够正确的接收数据。

HSTL电平单端输入逻辑

VREF电平为参考定义,在对称模式下(VREF=0.75V)HSTL电平的高低电平的噪声余量都能够达到0.65V。这就使得我们能够采用并联端接来解决信号完整性问题,而对于TTL、CMOS电平在前面第二章将阻抗匹配时已经提到一般不能采用并联端接,这也是为什么HSTL电平能够应用于高速存储器的原因。

HSTL电平也支持差分输入,相比单端信号需要额外关注的参数为差分幅值VDIF(AC) VDIF(DC)、共模噪声VCM(DC)、以及交叉点的范围VX如下表所示:

HSTL电平差分输入逻辑

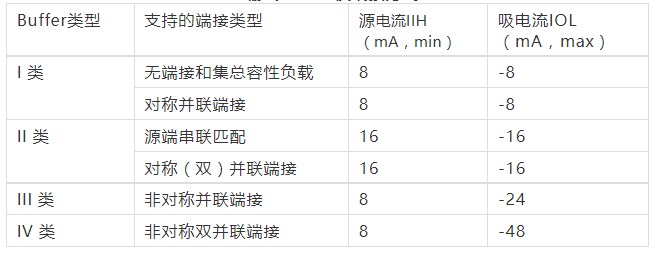

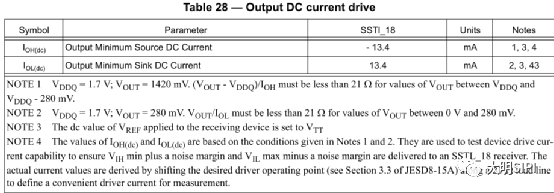

HSTL有四类输出Buffer类型,其主要不同在于输出电流的驱动能力以及支持的端接和匹配方式。表3中列出了四类输出Buffer各自支持的端接、匹配方式。

HSTL输出Buffer及端接方式对比

VREF电平来说,在对称的端接时VREF = VDDQ/2,此时VTT = VDDQ/2;非对称端接中VREF =0.9V,此时VTT =VDDQ。并联端接指的就是末端接上拉电阻到VTT,双并联端接指的是源端和末端都需要上拉电阻到VTT。

由上表可以看出:

I类输出buffer驱动电流最小且端接匹配方式最为简单,适用于负载比较轻不需要太大驱动能力的情况;

对于II类输出Buffer只是在I类的基础上增大了驱动能力(或者减小了输出阻抗),此时接收端信号如果存在过冲就可以使用远端串联匹配;

对于II类输出Buffer可以使用对称并联匹配,或者对称双并联端接,需要注意的是双并联端接肯定会降低接收信号的幅值有可能会使噪声余量变小。同时双并联端接增加了器件个数不利于高密单板的设计;

使用并联端接无疑要增加一个VTT电源,也可以采用戴维南匹配的方式等价实现VTT端接的效果;

由于III类输出Buffer的VTT=VDDQ这就导致其吸电流会比对称端接情况要大,IV类Buffer的双并联端接吸电流相比III类buffer的还要增大一倍;

并不是说所有的HSTL电平芯片都会定义四种输出Buffer类型,最常用的就是I类和II类。

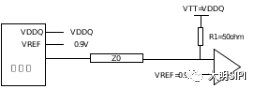

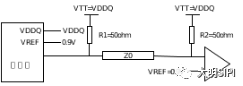

下图为III类buffer的非对称并联端接和IV类的非对称双并联端接示意图。

(左)III类buffer,非对称并联端接;(右)IV类buffer,非对称双并联端接

SSTL电平

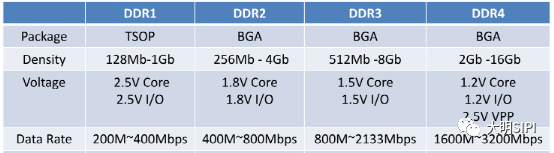

SSTL电平是为了保证存储器系统更高的数据吞吐率而定义的,它的优点就是能够驱动多个负载,提供更小的信号摆幅、更快的信号边沿。专门为高速存储器的应用开发而制定,特别针对于单双沿采样的SDRAM,如DDR SDRAM、DDR2、DDR3等,支持的工作频率在333MHz以上,其中DDR3的最高速率已经达到了2133Mbps,更高速率的DDR4也是采用SSTL电平和POD电平。

SSTL电平的输入结构基本上和HSTL相同,也是采用差分输入结构。差分一端接输入信号,另一端需要一个参考电压信号VREF。参考电压信号由所有存储器件和控制器共享,设计时需要保证控制器和存储器之间的压差要足够小,一般噪声都控制在1~2%范围内。类似HSTL电平,SSTL电平的输入门限也定义了AC和DC两个值,且都是参考VREF进行定义。

对于SSTL电平供电电压需要和HSTL电平基本相同。标准中并没有指定芯片功率供电电压VDD一般要求VDDQ要小于VDD。其中VTT是可选项,只是为解决DDR地址控制线的信号完整性问题所准备;VREF电源可以用分压电阻对VDDQ进行分压获得。在某些不需要使用VTT的情况下可以只用一个VDDQ电源输出芯片就可以进行DDR、DDR2等存储器接口的设计。

上面介绍了SSTL电平的输入结构、供电电压等共性的特征。实际上随着存储器的发展、以及通信系统对存储器容量、数据速率要求的越来越高,JEDEC定义了一系列的SSTL标准,有3.3V、2.5V、1.8V、1.5V甚至很多DDR3芯片都会兼容1.35V、1.2V的电平。SSTL_3SSTL_2的SSTL标准中也会分为I类和II类输出buffer用于驱动不同的负载。而对于SSTL_18SSTL_15 ,JEDEC没有在定义不同的输出类型,但是有些特殊的控制器自身也会定义不同的输出阻抗或者驱动电流,例如xilinx的virtex系列的FPGA、TI的DSP处理器,存储器芯片也会定义不同的输出阻抗供用户选择,如DDR3都会定义34ohm、40ohm两种输出阻抗。下面对这几种类型的SSTL电平分别进行介绍。

SSTL_3

SSTL_3采用3.3V供电,主要应用于DDR SDRAM存储器,其速率一般限制在333MHz以内。其VREF为1.5V(或者0.45*VDDQ)、VTT = VREF 。在典型应用中,在1.5V±200mV建立DC输入门限,在1.5V±400mV建立AC输入门限。

SSTL_3电平单端输入逻辑

SSTL_3理想情况下,高电平噪声余量1.6V、低电平噪声余量为1.3V,都要比3.3V电平的LVTTL/LVCMOS电平大了很多,使得SSTL_3能够应用于DDR SDRAM等存储器中。

SSTL_3的输出Buffer按照驱动电流的不同分为I类和II类两类。I类输出源电流和吸电流分别为±8mA,而II类的源电流和吸电流分别为±16mA。两种类型的输出Buffer对应了不同的驱动负载的能力,当负载比较小时可以使用I类输出buffer并采用直连或者源端串联匹配的方式,当负载比较重时需要考虑末端VTT并联端接。

SSTL_2

SSTL_2和SSTL_3类似主要有两点区别。VDDQ减小为2.5V,响应的VREF、VTT电平也都减小为0.5*VDDQ。另一不同就是SSTL_2可以支持差分输入和输出,能够应用于更高速率的DDR2存储器,而SSTL_3电平只支持单端输入输出。SSTL_2电平的单端AC和DC输入逻辑电平如下表所示:

SSTL_2电平的单端AC和DC输入逻辑

VDDQ电平的降低使SSTL_2的高低电平噪声余量都有所降低,在一定程度上提高了对信号完整性的要求。DDR2存储器中都设置ODT(on die terminate),即存储器芯片上的并联端接,端接阻值有50、75、150ohm三种类型,用户可以在MR(mode register)寄存器中进行设置,DDR2接收buffer内部的ODT电路结构如下:

DDR2内部的ODT电路结构图

DDR2存储器定义了ODT管脚,配合MR寄存器来控制SW1、SW2、SW3三组开关的通断。当ODT信号电平为高时使能ODT功能,具体使用何种阻值的ODT需要通过MR寄存器进行设置。工程师可以根据阻抗匹配情况、SI仿真结果进行选择。

SSTL_2电平差分输入逻辑

SSTL_2的输出Buffer两种类型和SSTL_3类似。源电流和吸电流的最小值差别很小,I类±8.1mA,II类±16.2mA,用于驱动不同类型的负载。

SSTL_18和SSTL_15

为了解决存储器速率不断提高功耗不断降低带来的挑战,SSTL电平引入了SSTL_18 SSTL_15甚至更低电平的标准。SSTL_18 SSTL_15规范的定义和SSTL_2非常类似,主要的区别就在于输入输出接口的供电电压有2.5V降低到1.8V和1.5V,由此而引起的VREF、VTT以及AC和DC输入门限的变化。

SSTL_18电平的单端AC和DC输入逻辑

而SSTL_15电平不仅参考VREF定义了±100mV的DC输入门限,而且还根据速率等级的不同定义了多个AC输入门限标准。对于地址控制、命令信号速率在800Mbps到1600Mbps定义了AC150和AC175两种输入门限VREF±150mV、VREF±175mV,当速率超过1600Mbps后则定义了AC125和AC135两种输入电平门限VREF±125mV、VREF±135mV;对于数据信号速率在800Mbps1066Mbps时使用AC150和AC175门限VREF±175mV,1333Mbps1600Mbps时使用AC150门限VREF±150mV,当速率在1866Mbps~2133Mbps是使用AC135门限VREF±135mV,详细内容参见下表。

SSTL_15电平的单端AC和DC输入逻辑

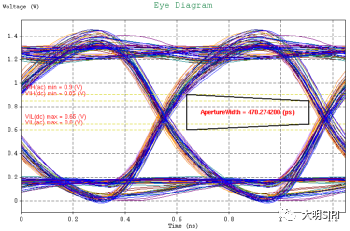

之所以如此定义SSTL_15的AC和DC门限,有些工程师可能会产生疑问:这样岂不是说AC135的门限要求就比AC175的门限要求更宽松呢?实际上并不是这样,而是要结合了建立保持时间的要求来看。也就是说AC175、AC150、AC135、AC125这些门限的定义都对应着不同的建立保持时间要求。表XX所描述的就是DDR3芯片的建立、保持时间要求。其中Base(specification)表示以AC175、AC150等AC门限为标准测量的建立时间tDS要求,而VREF@1V/ns表示1V/ns的slew rate情况下以VREF为标准测量的建立时间、保持时间要求。

DDR3建立保持时间要求

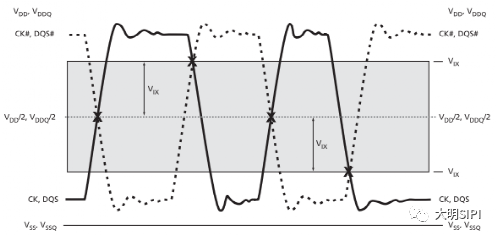

对于数据信号的建立时间tDS的测量是测量VIL(AC) 、VIH(AC)到DQS和DQS#的交叉点的延时,而保持时间tDH是测量从DQS和DQS#的交叉点到VIL(DC) 、VIH(DC)的延时。基于这种对建立保持时间的测量方法,我们可以得到DDR3眼图的一般测量方法。以VIL(AC) 、VIH(AC)和高低电平起始的最后一个交点做垂直于时间轴的直线,以VIL(DC) 、VIH(DC)和高低电平结束的第一个交点做垂直于时间轴的第二条直线。第一条直线和VIL(AC) 、VIH(AC)的两个交点以及第二条直线和VIL(DC) 、VIH(DC)的两个交点,这四个点构成一个梯形,我们便可以以此梯形为基准来描述眼图的眼宽和噪声裕量。

DDR3数据信号建立保持时间的测量

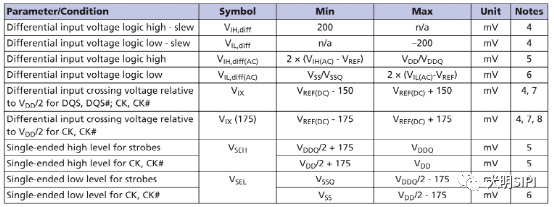

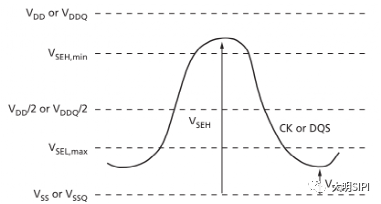

同样对于差分输入电平SSTL_15除了对单端信号的逻辑定义外也对差分逻辑、以及单端信号的交叉点范围进行了定义,如下表所示。

SSTL_15电平差分输入逻辑

DDR4的电平标准

前面花了很长时间介绍了HSTL和SSTL电平,但我想大家应该都很清楚,目前在市场上占主导地位的内存是DDR4。为什么画这么多的篇幅来讲已经过时的东西呢?其实就是想让大家尽量了解存储器电平发展的来龙去脉。通过前面的介绍我们大体可以知道,电平接口的发展要解决的两个主要问题:

(1)速率的提升,以达到足够高的吞吐量,满足CPU和外设直接的高速数据交换和处理;

(2)功耗的降低,不断的降低接口的IO电压来达到更低的功耗要求。

那么DDR4在这两方面又有什么样的改进呢?DDR4将速率提升到1.6—3.2Gbps,并为进一步降低功耗DDR4的数据信号采用了新的电平标准POD-12,地址控制信号仍然是SSTL电平,只不过电压降低到了1.2V。下面我们来看一下什么是POD电平,它和SSTL电平到底有什么不同。

POD电平

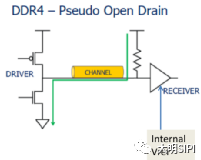

POD是Pseudo Open Drain的缩写,字面理解就是“伪开漏极”电平。那为什么是“伪开漏极”呢?让我们看一下它的结构。

(左)SSTL电平(右)POD电平

如上图所示,可以看出POD电平的输出电路和SSTL电平并没有差别,差别仅仅在于POD和SSTL电平的所采用的终端端接方式(ODT)和Vref不同。SSTL电平的Vref是固定值0.5倍的VDD,终端采用标准的戴维南端接;而POD电平的Vref是芯片内部确定,外部的端接只用一个上拉电阻。

首先,我们先看Vref。理想的Vref位置应该位于数据眼图的中央,即Vref = Vmid = 0.5*(Vhigh + Vlow)。对于DDR4的数据信号理想的Vref位置示意如下:

然而在实际中,由于驱动器、传输通道以及ODT的非理性特性,眼图的中央位置很难计算出来。每个DQ信号的驱动、传输通道、和ODT都会有偏差,所以每个DQ的Vref都可能各不相同。因此,需要一种自适应的training机制来寻求最优的Vref。

这种自适应的training机制为DDR4的DQ信号在更低的电平下获得足够的噪声余量提供了有利条件。

同时对比SSTL和POD电平,我们可以发现:POD电平只有在低电平时才会有功耗,高电平由于Tx和Rx是等电位的几乎没有电流因此功耗几乎为零。这就是POD电平的另一个优势,使得DQ信号的功耗几乎降低了50%。

DDR4和与DDR3的比较

DDR4相比DDR3还有一些其它方面的改进,在这里也做一些简单的介绍。

DBI_N

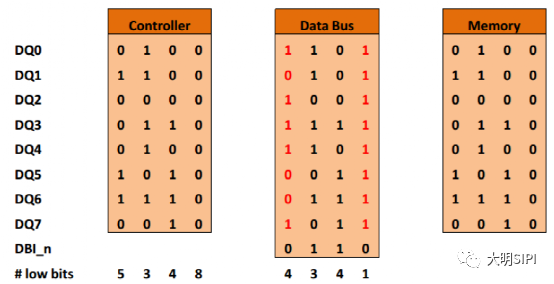

为了进一步降低功耗,DDR4定义了一个新的管脚DBI_N。DBI是data bus inversion的缩写。目的在于平衡DQ信号中的0和1的数量。

如上所示,当DQ信号中0的数量超过1的数量时,DBI_N信号拉低,让DQ信号的bit翻转,这样只有打开DBI功能DQ信号中0的数量总是比1的数量少。这就意味着更低的功耗和更好的SSN性能。

DBI功能也有自身的缺点,因为Memory接收数据需要对DBI进行翻译,需要额外的延时,对数据吞吐量稍有影响。

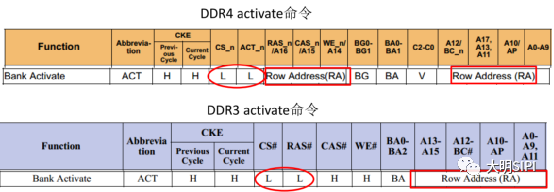

ACT_N

DDR4相比之前的DDR3,除了速率的提升、电压的降低,存储容量也有了很大的提升。理论上存储容量的提升就需要更低的地址信号来寻址。

为此,DDR4引入了ACT_N信号,用来指明activate命令,拓展行地址,来实现更大的容量。如下所示,当ACT_N为低电平时,RAS、CAS、WE为地址信号。

DDR4的校验机制

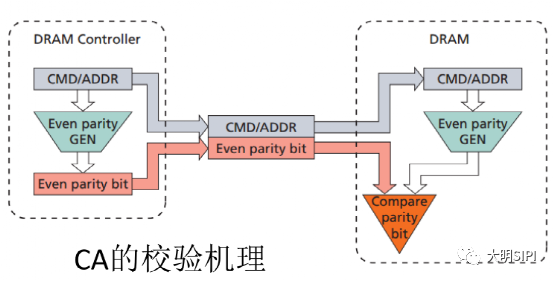

1、Address/Command信号的校验

增加了PAR管脚,为Address/Command信号的奇偶校验位。DDR4采用偶校验,也就是所有bit中1的个数是偶数。校验的过程使得系统产生额外的延时。

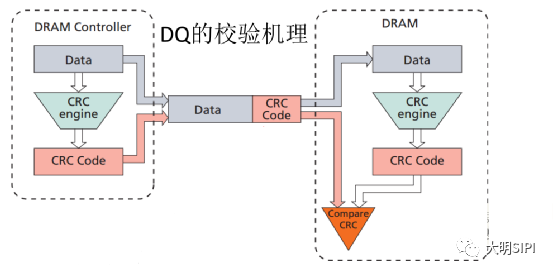

2、DQ信号的校验

DQ信号采用CRC校验。CRC校验机制如下图所示,与CA信号的奇偶校验不同,CRC不需要额外的管脚。但是CRC编码需要占用额外的数据带宽,此外,CRC也会产生额外的系统延迟。

3、ALER_N

DDR4增加了Alert_N信号,指明数据的传输是否发生了错误,包含Data的CRC Error或者Address/Command上的奇偶校验错误。

正是由于DDR4的这种校验机制,使得自适应的training变得成为可能。前面介绍了VREF需要自适应的training,其实水平方向的时间轴上也需要training。

4、DQ信号的skew的training

在时间轴上,每个DQ信号的眼图并不能完全对齐。尽管你十分小心的调整了所有DQ信号的skew,补偿了封装的布线,但还会有驱动器的输出能力偏差、ODT的偏差、PCB加工的偏差、码型的影响、其它信号的干扰等等我们无法穷尽的影响因素。

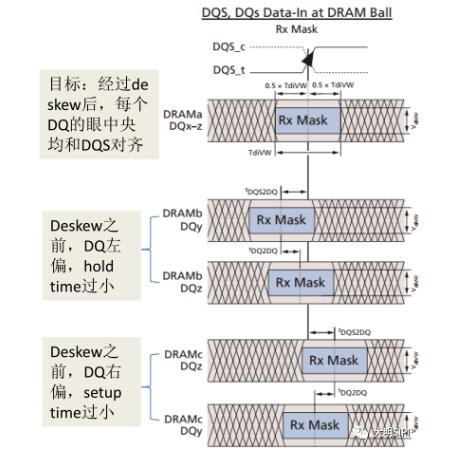

DDR4的速率已经达到了serdes的速率,它的时序余量已经非常小,它的设计难度显然更高。因此,需要一种自适应的training的机制,来保证每个DQ信号的眼在DRAM的die处都是对齐的,这种DQ时间轴的对齐机制又叫做per bit de-skew。

DDR4还有其它的一些特性,但与信号完整性关系不大,因此这里不做详细的介绍。目前DDR5颗粒已经开始商用,相比DDR4,DDR5无论在数据速率还是功耗上又是一次提升,后面有机会也会做一些介绍。

-

高速信号的电源完整性分析2012-08-02 3623

-

信号完整性2019-02-14 1918

-

常用信号完整性的测试手段和实例介绍2019-06-03 2276

-

信号完整性的三大测试的那些事儿(建议收藏)2020-04-10 2001

-

简单总结一些造成电源完整性的问题2021-10-29 2216

-

电源完整性PI的一些原理2021-11-15 1757

-

信号完整性基础指南2010-08-05 1221

-

常用信号完整性的测试手段和在设计的应用2009-06-30 1037

-

信号完整性分析2011-11-30 7846

-

提高信号完整性的PCB材料2018-02-05 1971

-

常用的三种测试信号完整性的方法2020-10-30 3361

-

信号完整性常用的测试方法有哪些2020-12-25 1768

-

信号完整性常用的三种测试方法2020-12-26 6612

-

信号完整性常用的一些测试方法和使用的仪器2022-06-10 8739

-

什么是信号完整性?2023-06-27 3614

全部0条评论

快来发表一下你的评论吧 !