基于Chiplet方式的集成3D DRAM存储方案

存储技术

描述

作者邵乐峰

新能源汽车、5G、可穿戴设备等领域的不断发展,对芯片性能的需求越来越高,采用先进封装技术的 Chiplet 成为了芯片微缩化进程的“续命良药”。

在边缘计算领域里,对 DRAM 带宽的要求远高于容量,此时采用 Chiplet 方式集成 3D DRAM 存储方案,就可以同时提供高带宽和低功耗。

今年2月,在正式加入 UCIe (Universal Chiplet Interconnect Express) 产业联盟之后,华邦电子随即宣布其创新产品 CUBE: 3D TSV DRAM 和 3DCaaS (3D CUBE as a Service) 一站式服务平台,将成为公司向客户提供优质定制化内存的首选解决方案。

芯片微缩化的“续命良药”

CUBE 是 Customized/Compact Ultra Bandwidth Elements,即“半定制化紧凑型超高带宽 DRAM” 的简称。华邦电子次世代内存产品营销企划经理曾一峻在向《电子工程专辑》说明 CUBE 核心价值时表示,新能源汽车、5G、可穿戴设备等领域的不断发展,对芯片性能的需求越来越高,但如果采用诸如“直接在 5nm SoC 裸片上堆叠 7nm SRAM 裸片”的做法,会因为带入太多 TSV 工艺架构而导致芯片成本暴涨。

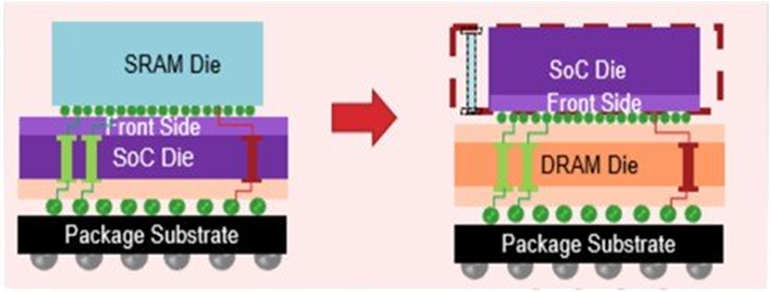

于是,采用先进封装技术的 Chiplet 成为了芯片微缩化进程的“续命良药”。“这也是华邦解决方案的思路”,按照曾一峻的解释,在边缘计算领域,华邦将 SoC 裸片置上,DRAM 裸片置下,省去了 SoC 中的 TSV 工艺(图中虚线部分所示),从而大幅降低了SoC 裸片的尺寸与成本。与此同时,3D DRAM TSV 工艺又可以将 SoC 信号引至外部,使它们成为同一颗芯片,进一步缩减了封装尺寸。

另一方面,考虑到现在的 AI 芯片都有着很高的算力需求,SoC 裸片置上也可以带来更好的散热效果。因此,华邦方面认为,按照这样的方式进行 CUBE 3D DRAM 裸片堆叠可以带来高带宽、低功耗和优秀的散热表现,这也是华邦 CUBE 解决方案主要面向低功耗、高带宽、中低容量内存需求应用的主要原因。

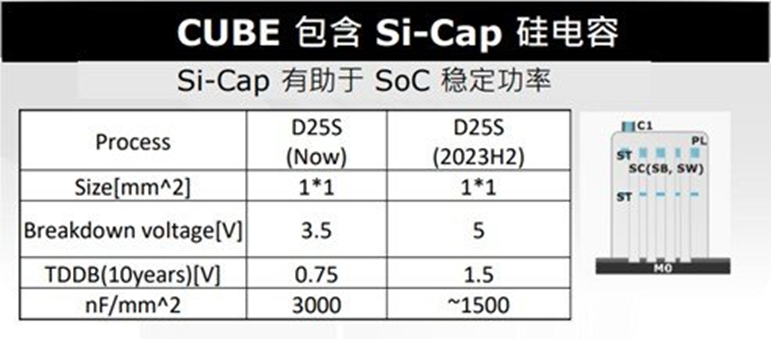

众所周知,DRAM 裸片中都会包含电容,华邦 CUBE 芯片也不例外。目前,先进制程 SoC 芯片的核心电压约为 0.75V-1V,运行过程中电源产生的波动会影响功耗和信号稳定性。但 CUBE 芯片所采用的硅电容(Si-Cap) 却可以有效降低电源波动带来的影响。

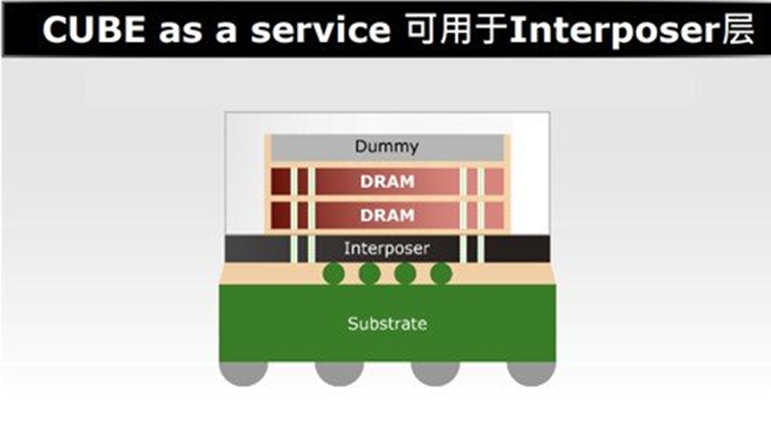

再来关注一下华邦 DRAM 堆叠和中介层(Interposer) 架构的演进。如图所示,由于中介层也是华邦提供,因此客户可以得到一个包括 DRAM、中介层、硅电容在内的整体解决方案,这也是华邦加入 UCIe 后做出的贡献之一。

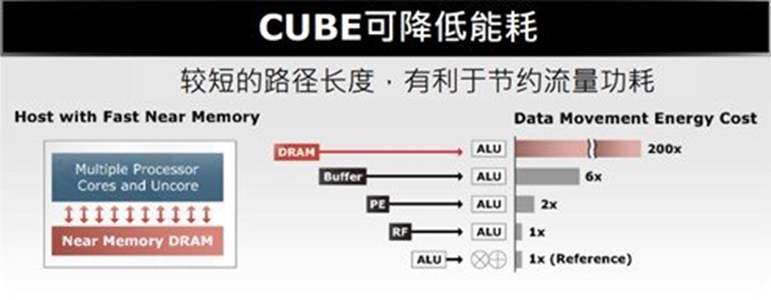

另一个值得关注的优势来自功耗的降低。由于 SoC 裸片和 DRAM 裸片堆叠的时候,相比于传统的引线键合(Wire Bonding),微键合(Micro Bonding)工艺可以将 1000 微米的线长缩短至 40 微米,仅有传统长度的 2.5%,在未来的混合键合(Hybrid Bonding)封装工艺下,线长甚至可以缩短至 1 微米。这意味着在芯片内部,信号所经过的传输距离更短,功耗自然也得到相应的降低。此外,当采用混合键合工艺时,两颗堆叠的芯片其实可以被看作同一颗芯片,因此内部传输信号和 SIP 表现会更优秀。

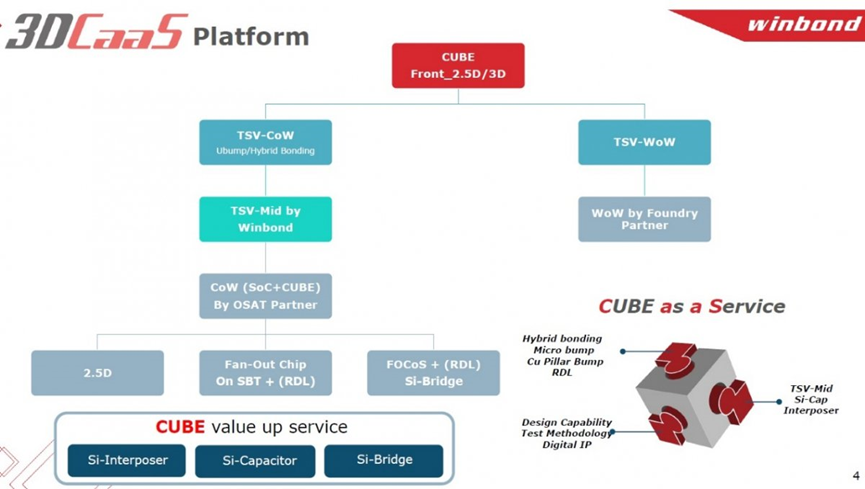

与 CUBE 同时出现的还包括 3D CaaS 平台,也就是 CUBE as a Service。这意味着对于客户来说,华邦不仅仅提供 3D TSV DRAM KGD 内存芯片和针对多芯片设备优化的 2.5D/3D 后段工艺(采用CoW/WoW),还可获取由华邦的平台合作伙伴提供的技术咨询服务,是一套完整且全面的 CUBE 产品支持,并享受 Silicon-Cap、interposer 等技术的附加服务。

CUBE 应用架构

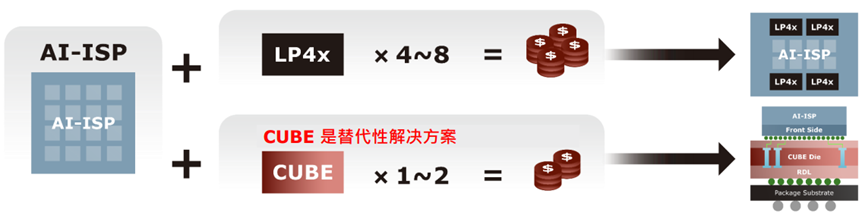

ChatGPT 的面世带动了 AI 应用领域的再次火热,而 CUBE 就可以应用到 AI-ISP 架构中。

上图中的灰色部分代表 AI-ISP 中的神经网络处理器(NPU),如果 AI-ISP 要实现大算力,就需要很大的带宽,或者是 SPRAM 加持。但目前来看,在 AI-ISP 上使用 SPRAM 成本高昂,转而使用LPDDR4 则需要 4-8 颗,如果用到传输速度为 4266Mhz 的高速 LPDDR4,还需要依赖 7nm 或 12nm 的先进制程工艺。

相比之下,CUBE 解决方案就可以允许客户使用成熟制程(28nm/22nm)获得类似的高速带宽。简单而言,CUBE 芯片可以通过多个 I/O (256 或者 512个)结合 28nm SoC 提供 500MHz 运行频率,以及最高 256GB/s 带宽。据透露,华邦在未来可能会和客户共同探讨 64GB/s 带宽的合作可能性,如果成功,I/O 数量和裸片尺寸都将进一步缩小。

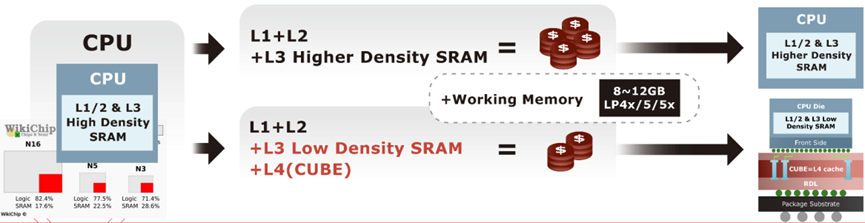

在下面的应用场景中,CPU 的高速运算需求对制程的要求从 16nm、7nm、5nm 到 3nm,越来越高。但不难发现,尽管制程工艺越来越先进,图中红色部分所代表的 SRAM 占比并没有同比例缩小,因此当需要实现 AI 运算或者高速运算的情况下,就需要将 L3 缓存 SRAM 容量加大,即便采用堆叠方式达到几百 MB,也会导致高昂的成本。

华邦的做法是将 L3 缓存缩小,转而使用 L4 缓存的 CUBE 解决方案。这并不意味着 CUBE 解决方案的时钟传播延迟(Latency)等同于 SRAM,而是可以作为 L4 缓存。原因在于 CUBE 可以进行定制化的设计,使得时钟传播延迟比一般的 DRAM 还要短。同时,考虑到AI模型在某些情况下需要外置一定容量的内存,例如在某些边缘计算场景下会需要 8-12GB LPDDR4/LPDDR5,因此在需要的情况下,也可以外挂高容量工作内存(Working Memory)。

“在边缘计算领域里,对 DRAM 带宽的要求远高于容量,此时采用 Chiplet 方式集成类似 CUBE 的存储方案,就可以同时提供高带宽和低功耗。”但曾一峻也同时强调称,毕竟 Chiplet 芯片需要兼容多个接口协议才能避免造成信号偏差,因此,如何进一步缩小 3D DRAM 的裸片尺寸,如何更好的实现不同芯粒间的互联互通,是绕不开的挑战。

华邦 DRAM 技术路线图

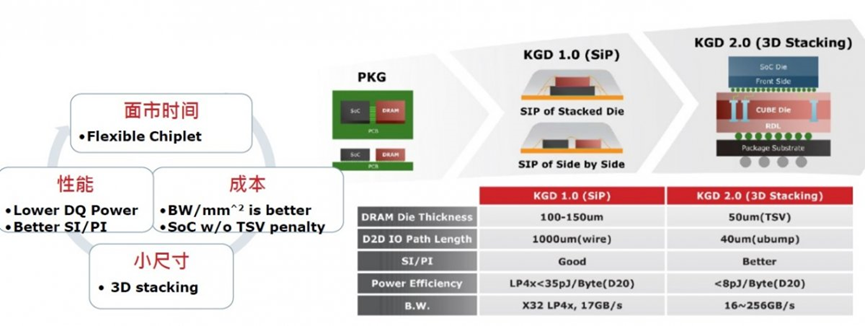

相对于市场上三大头部内存厂商而言,华邦主要专注于利基型内存,产品容量一般最大为 8GB,其特点是不需要非常先进的制程,并以 KGD 为主,便于与 SoC 进行合封。

在 KGD 1.0 (SiP) 中,DRAM Die 厚度约为 100-150 微米,裸片至裸片 (Die to Die) 的 I/O 路径为 1000 微米,目前这种性能的 KGD 信号完整性/电源完整性 (SI/PI) 是主流的,也是够用的。华邦方面曾经对 LPDDR4 的电源效率进行过估算,其小于 35pJ/Byte,带宽方面 X32 LPDDR4x 每 I/O 为17GB/s。

当进化到 KGD 2.0 (3D堆叠) 后,得益于 TSV 的深宽比能力,DRAM Die 厚度可以达到 50 微米的深度,未来,通过 Hybrid Bonding 工艺还可以实现 1 微米的距离。同时,信号完整性/电源完整性 (SI/PI) 性能更好,功耗更低,可以达到甚至低于 LPDDR4 的四分之一 (为8pJ/Byte),而带宽可以实现 16-256GB/s。

目前,华邦拥有两座 12 寸晶圆厂,一座是位于台中的 Fab 6 工厂,另一座是在高雄新建的第二座工厂,其产能为 1 万片/月左右,后续将逐渐提升至 1.4 万片 - 2 万片/月。

从制程工艺角度来看,高雄工厂投产后,华邦会将一些先进制程的 DRAM 产能转移至高雄厂,台中厂的中小容量 DRAM 制程会维持在 65nm、46nm、38nm 和 25nm,且无意再向更小制程演进,而是专注于成熟制程产品。高雄厂已经量产的包括 25nm 2GB 和 4GB 两种产品,20nm 产品预计在今年年中进入量产阶段,并继续向 19nm 制程演进。

华邦电子大陆区产品营销处处长朱迪再次强调了华邦对于 DDR3 的生产和支持。尽管他认为像三星这样的大厂逐渐舍弃 DDR3 和中小容量 DDR4 是一个大概率的事件,但从实际使用情况来看, 4Gb DDR3 产品将有望继续被广泛采用至少到 2027-2028 年,尤其在工业和汽车领域需要长期支持。而且,相同容量相同速度下,DDR3 较 DDR4 更具成本效益(相同制程下,与 DDR3 相比,Die 尺寸 DDR4 增加 10%,LPDDR4 增加18%),DDR4 将会持续向更高容量发展,并随着 PC 和服务器市场的需求迁移至 DDR5。

根据规划,DDR3 仍将保持 1Gb、2Gb、4Gb 和 8Gb 四种容量,并计划在 2025 年演进至 16nm;DDR4 方面,当 20nm 制程就绪之后,高雄厂会在 2024 年初量产 DDR4 DRAM 芯片。

“利基型存储市场大约只占整个存储市场的 10%,它的供需相对而言是比较平衡和稳定的。在当前终端客户、代理商、以及原厂库存都比较低的情况下,确实有可能会出现缺货的情况,但对具体时间节点做出判断为时尚早,需要做进一步的观察。”朱迪说。

编辑:黄飞

-

为了延长DRAM存储器寿命 必须短时间内采用3D DRAM2017-03-17 3914

-

2.5D集成电路的Chiplet布局设计2025-02-12 2675

-

3d全息风扇灯条|3D全息风扇方案|3d全息风扇PCBA2019-08-02 2259

-

芯片的3D化历程2020-03-19 2235

-

3D XPoint的原理解析 NAND和DRAM为什么拼不过它2018-04-19 52512

-

关于3D超级DRAM技术简单剖析2018-10-28 5749

-

硅3D集成技术解决方案在传感器应用中的主要挑战2020-01-16 1710

-

如何看待3D DRAM技术?2023-05-31 1258

-

3D封装正当时!2023-06-21 1319

-

当芯片变身 3D系统,3D异构集成面临哪些挑战2023-11-24 2317

-

3D 封装与 3D 集成有何区别?2023-12-05 2559

-

三星电子新设内存研发机构,专攻下一代3D DRAM技术研发2024-01-29 1285

-

三星电子在硅谷设立下一代3D DRAM研发实验室2024-01-31 1466

-

三星电子:2025年步入3D DRAM时代2024-04-03 1220

-

3D DRAM进入量产倒计时,3D DRAM开发路线图2024-04-17 1955

全部0条评论

快来发表一下你的评论吧 !