RA6快速设计指南 [6] 复位要求和复位电路 (上)

描述

6

复位要求和复位电路

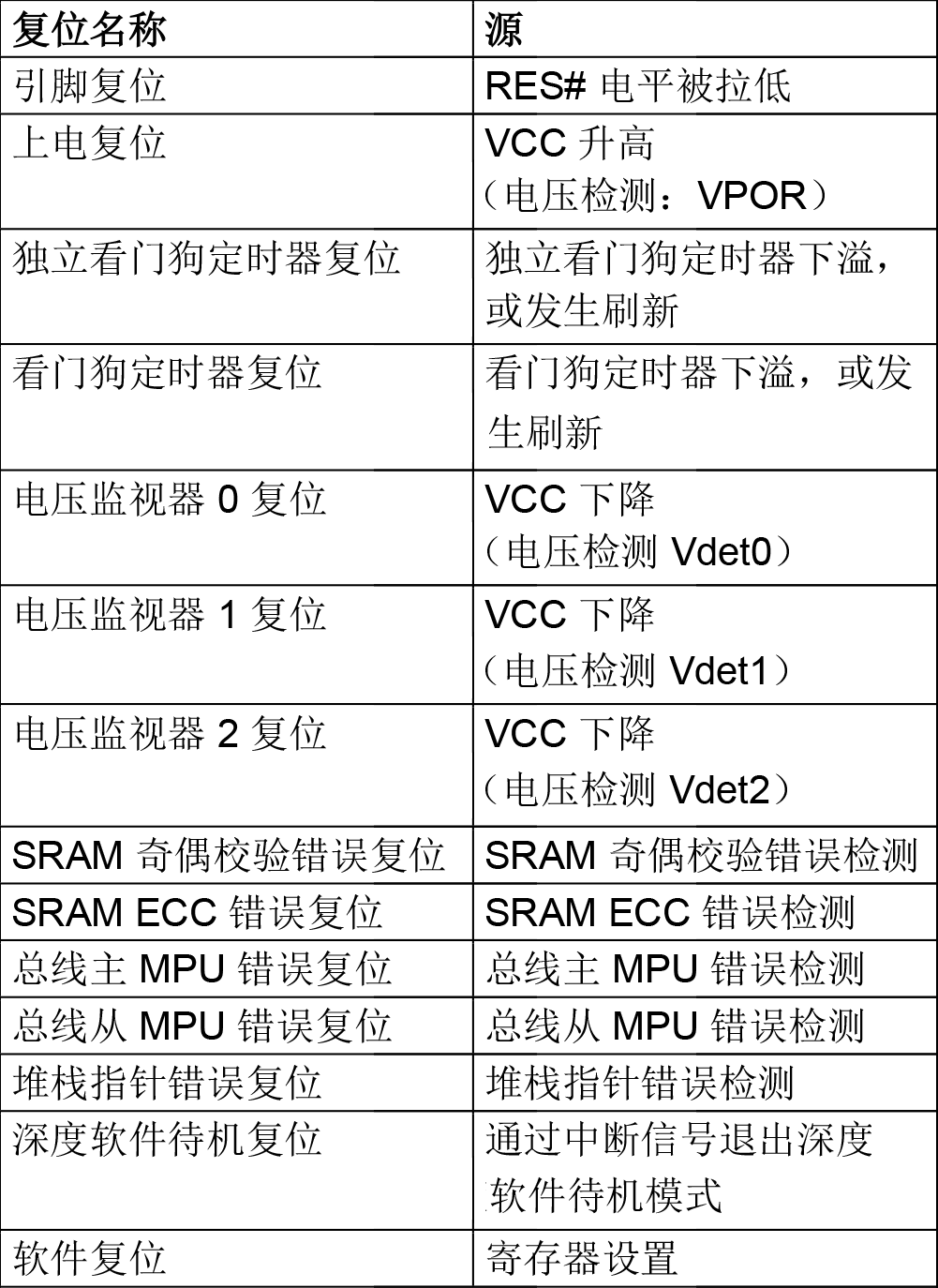

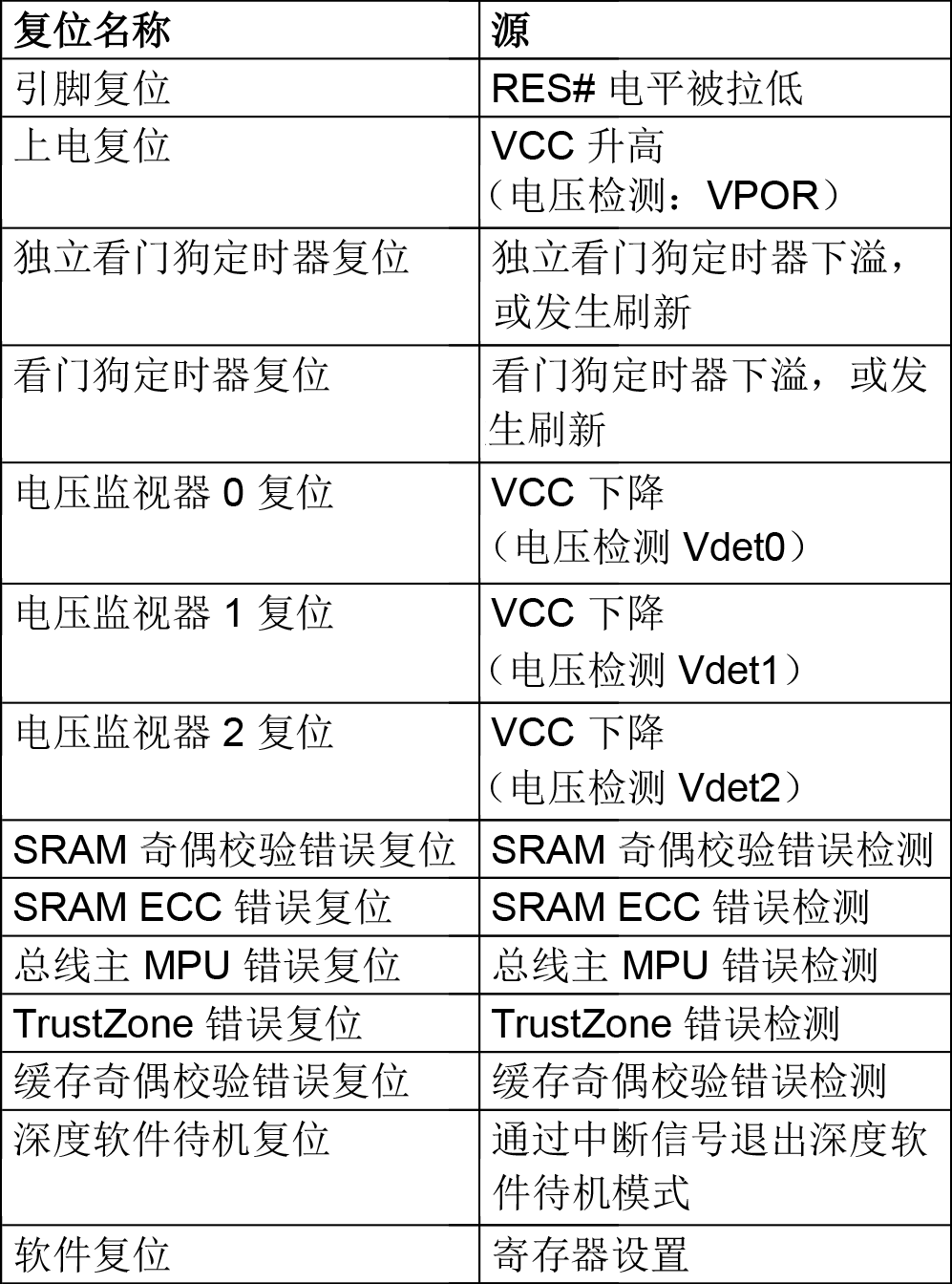

共有十四种类型的复位。这些复位在Arm Cortex-M4器件和Arm Cortex-M33器件之间略有不同。

表11. Arm Cortex-M4器件复位

表12. Arm Cortex-M33器件复位

6.1 引脚复位

当RES#引脚电平被拉低时,所有处理都将中止,MCU进入复位状态。要在运行中复位MCU,应在指定的复位脉冲宽度内将RES#保持为低电平。有关时序要求的更详细信息,请参见《硬件用户手册》中“电气特性”一章的“复位时序”部分。另请参见本系列文章的第2节“仿真器支持”,了解与调试支持相关的复位电路的详细信息。

无需在RES#线路上使用外部电容,因为POR电路在内部将其保持为低电平以实现良好的复位,并且需要最小的复位脉冲来启动此过程。

6.2 上电复位

有两种情况会产生上电复位 (POR):

1

如果RES#引脚在接通电源后处于高电平状态。

2

如果RES#引脚在VCC低于VPOR时处于高电平状态。

在VCC超过上电复位电压 (VPOR) 并经过上电复位时间 (tPOR) 之后,芯片将从上电复位状态释放。上电复位时间是允许外部电源和MCU达到稳定状态的时间。有关电压大小和时序的详细信息,请参见《硬件用户手册》中“电气特性”一章的“POR和LVD特性”部分。

由于POR电路依赖于RES#与VCC同时为高电平,因此请勿在复位引脚上放置电容。这将减慢RES#相对于VCC的上升时间,从而妨碍POR电路正确识别上电条件。

当电源 (VCC) 降至不超过VPOR时,如果RES#引脚为高电平,则会产生上电复位。在VCC上升到VPOR以上并且经过tPOR之后,芯片将从上电状态释放。

上电复位后,RSTSR0中的PORF位置1。引脚复位后,PORF清零。

6.3 独立看门狗定时器复位

这是由独立看门狗定时器 (IWDT) 产生的内部复位。

当IWDT下溢时,可以选择产生独立看门狗定时器复位(可以改为产生NMI),并且RSTSR1中的IWDTRF位置1。短暂延迟(通常为320µs)后,将退出IWDT复位。

6.4 看门狗定时器复位

这是看门狗定时器 (WDT) 产生的内部复位。

当WDT下溢时,可以选择产生看门狗定时器复位(可以改为产生NMI),并且RSTSR1中的WDTRF位置1。短暂延迟(通常为320µs)后,将退出WDT复位。

-

RA2快速设计指南 [4] 复位要求和复位电路2023-10-24 1395

-

RA6快速设计指南 [17] 外部总线,一般布线实践 (上)2023-07-14 1447

-

RA6T1 CPU 卡快速入门指南2023-07-05 460

-

EK-RA6M2– 快速入门指南2023-07-04 488

-

EK-RA6M3G – 快速入门指南2023-07-03 492

-

RA6快速设计指南 [10] 存储器 (2)2023-06-26 1712

-

RA6快速设计指南 [9] 存储器 (1)2023-06-21 2173

-

RA6快速设计指南 [8] 使用TrustZone®2023-06-19 1644

-

RA6快速设计指南 [7] 复位要求和复位电路 (下)2023-06-16 1840

-

RA6快速设计指南 [5] 时钟电路 (3)2023-06-12 1571

-

RA6 MCU设计之时钟电路2023-06-09 786

-

RA6快速设计指南 [1] 简介,电源,仿真器支持(1)2023-06-04 2407

-

RA2快速设计指南 [5] 复位要求和复位电路2023-04-03 2159

-

EK-RA6M5 – 快速入门指南2023-02-02 540

全部0条评论

快来发表一下你的评论吧 !