一文详解GPIO的输入配置

应用电子电路

描述

GPIO-1---GPIO的输入配置

引言:GPIO,即General purpose input output,通用输入输出端口,是可以根据实际使用场景需求来用软件来配置的引脚。需要注意的是,一款芯片的引脚分为其实分为很多域,比如仅为芯片供电的引脚群称为电源域,还有类似复位,地址配置等等称为逻辑域,还有原生支持I2C,SPI等等通讯的称为通讯域,搭建小系统用的引脚称为系统域。本节我们主要讲述不具有特定功能的GPIO域。(本节和下节是所有的GPIO配置类型,但有的芯片GPIO不全都支持,这类GPIO叫裁剪型GPIO,使用芯片时需要查看其Pin List,不能默认都是全功能的GPIO)

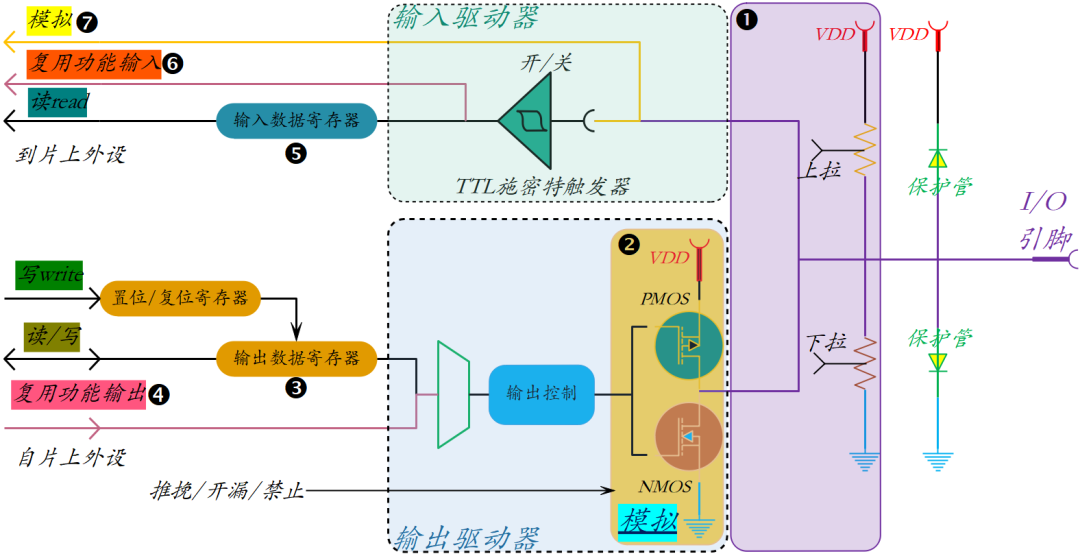

1.GPIO的一般结构

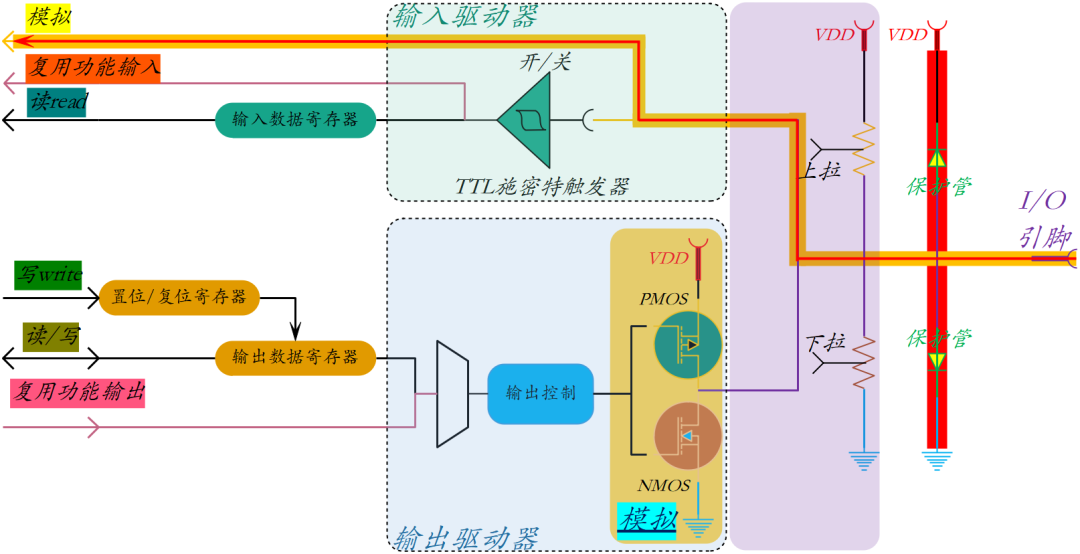

如图1-1所示为GPIO的一般结构,由七大部分组成:上下拉+推挽MOS+输出数据寄存器+复用功能输出+输入数据寄存器+复用功能输入+模拟输入,其中保护管二极管不是每一个芯片都有。

1.保护二极管

比如芯片的引脚电平为0/3.3V,引脚的两个保护二极管可以在一定程度上防止引脚外部过高或过低的电压输入损坏引脚。当引脚电压高于3.3V时,上方二极管导通钳位,防止过高电压进入芯片内部。同理当引脚电压低于GND(负电压)时,下方二极管导通,防止电压过低从芯片内部抽取电流。

2.施密特触发器

施密特触发器有两个阈值,高于上面的阈值就输出固定高电平,低于下面的阈值就输出固定低电平,有效去除输入信号的波动效应。

图1-1:GPIO的一般结构

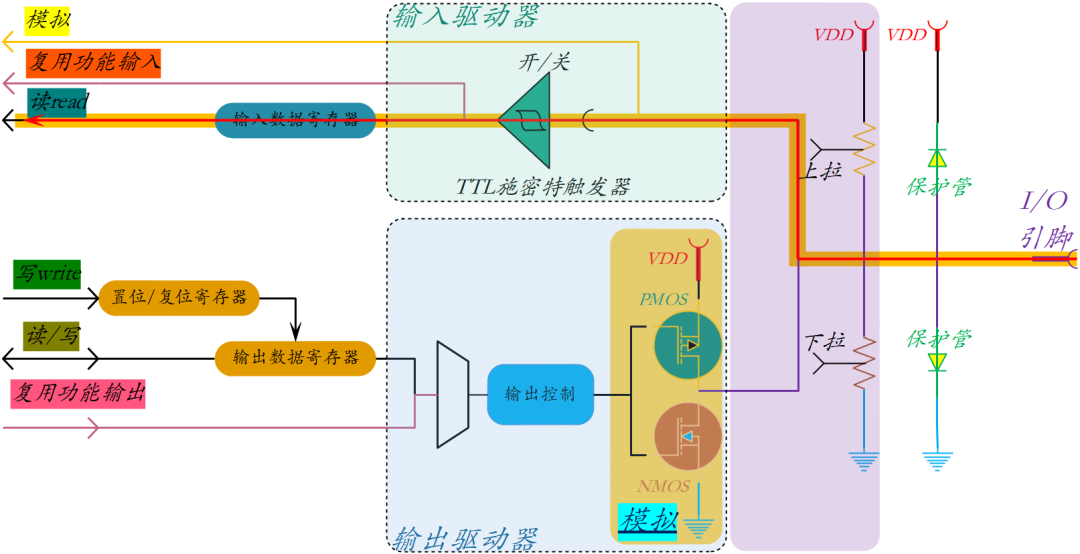

2.浮空输入模式

浮空输入模式为数字输入模式,可读取引脚电平,如果引脚悬空,则电平不确定,在浮空输入模式时,施密特触发器会打开,此时输出驱动器被禁止。

图1-2:浮空输入模式路径

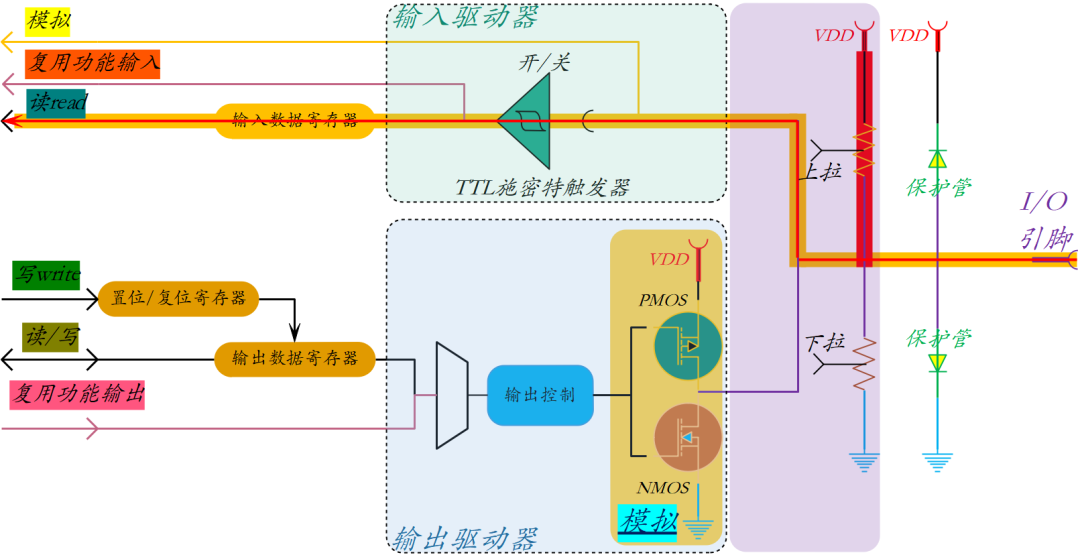

3.上拉输入模式

上拉输入模式为数字输入模式,可读取引脚电平,此时内部上拉电阻使能激活,IO口被上拉电阻连接到VDD,当引脚悬空时默认高电平。在上拉输入模式时,施密特触发器会打开,此时输出驱动器被禁止。

图1-3:上拉输入模式路径

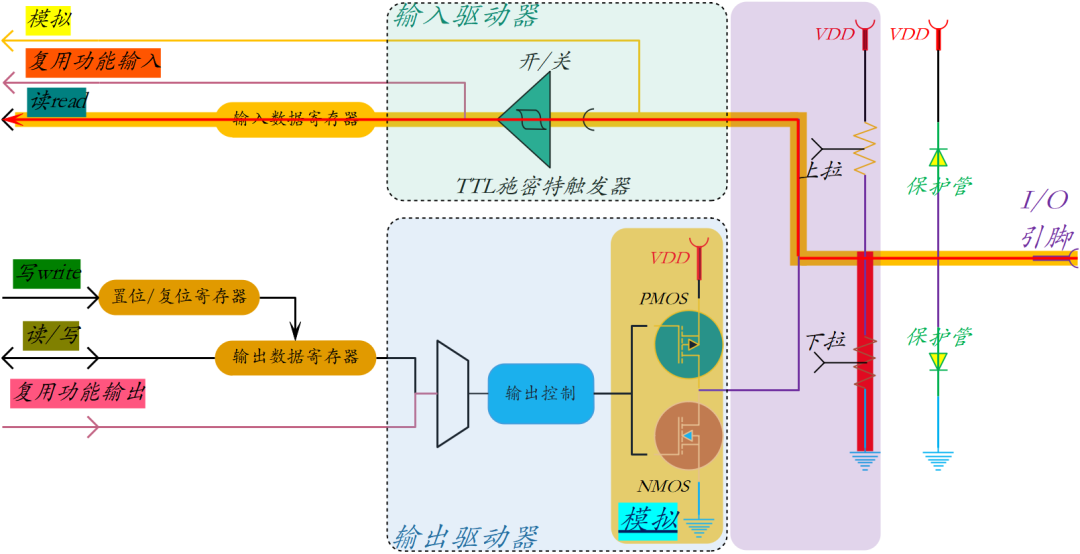

4.下拉输入模式

下拉输入模式为数字输入模式,可读取引脚电平,此时内部下拉电阻使能激活,IO口被下拉电阻连接到GND,当引脚悬空时默认低电平。在下拉输入模式时,施密特触发器会打开,此时输出驱动器被禁止。

图1-4:下拉输入模式路径

5.模拟输入模式

当配置为模拟输入时,输出驱动器关闭,施密特触发器关闭,引脚的模拟电平直接输入到芯片内部,一般是输入到ADC模块进行采样,此时一定要注意引脚电平的大小,不然会损坏芯片。所以模拟输入模式主要为片上ADC配置的,注意模拟输入电平和ADC的量程是否匹配。

图1-5:模拟输入模式路径

6.小结

在输入模式下可以读取引脚是高电平还是低电平或者电压值,用于读取按键输入,外接模拟电平信号输入,ADC电压采集,配合输出模式可以模拟通信协议(I2C,SPI等等)接收发送数据。

-

HAL库GPIO输入模式在cubemx中的配置2022-11-02 3030

-

一文详解GPIO的输出配置2023-06-14 3942

-

CC2530 GPIO口输入配置配置步骤2023-07-06 4796

-

STM32的8种GPIO输入输出模式2021-11-26 2401

-

GPIO配置2021-12-01 884

-

STM32低功耗模式下GPIO如何配置最节能?2021-12-07 1344

-

STM32-GPIO详解2021-12-24 870

-

STM32中GPIO_Mode--GPIO配置2021-12-28 896

-

关于STM32 GPIO的配置等问题2022-01-13 839

-

详解GPIO输入实验2023-07-02 2013

-

STM32单片机的GPIO输入、输出模式与配置方法2023-08-15 10401

-

STM32使用GPIO配置的5种方式2023-10-26 2568

-

如何配置GPIO为中断功能呢?2023-10-30 4622

-

如何配置GPIO引脚2025-01-09 2304

-

为什么GPIO配置总是出问题?2025-04-07 1917

全部0条评论

快来发表一下你的评论吧 !