使用具有射频锁相环相位同步特性的SDR简化天线校准

描述

本文着重介绍ADI公司的软件定义无线电(SDR)中的射频(RF)锁相环(PLL)相位同步特性。这个功能有助于降低天线校准的复杂性,特别是对于采用大型天线阵列的系统。关于同步的控制和配置,请参见用户指南1。本文着重介绍其应用和优势。

相位相干信号

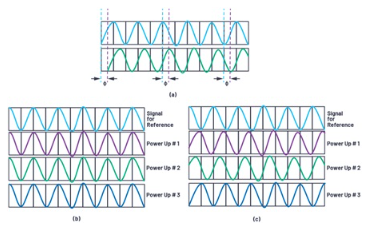

相干性是波的一种特性,定义了单个波或两个或多个波之间的物理量中存在的关系。在电子学中,物理系统处理连续波和时钟信号的相位、频率和振幅。一般来说,随着时间流逝,如果两个信号之间的差别始终保持恒定不变和稳定,那么这两个信号就是相位相干的。图1a显示了随着时间不断流逝,两个信号的相位。这两个信号表现出相干相位关系,因为它们之间的相位保持不变。图1b比较了系统中的基准信号在不同上电周期中的初始相位。从这个图中,还可以看出在每次上电后,两个信号之间的相干相位关系。但是,在图1c所示的示例中,相位是不相干的,因为在每次上电后,信号都以随机相位作为开始。

图1. 相干相位关系和不相干相位关系示例。

多通道和多天线系统中的相位缺陷和消除

相控阵和大规模MIMO系统具有多个天线和多个射频通道。从数字后端到天线阵列,在多平面上保持相位相干和时序同步,这是这类系统的主要要求。例如,在介质访问级别需要帧同步,数字接口需要相干性(例如,确定性延迟),在多个转换器或芯片对多个通道进行采样时需要同步,要生成射频,需要多个本地振荡器(LO)之间相位相干,以及,需要天线阵列的各元件之间保持确定性相位关系。因此,在不同阶段保持相干关系至关重要。但是,因为一些现实因素,这一任务非常具有挑战性,例如器件与器件之间的差异、印刷电路板上的线路、组件之间的非线性、耦合效应、分频器比率、硬件老化、时钟漂移、温度漂移,以及本地振荡器漂移。

如果一个系统中使用多个射频本地振荡器,还需要注意本地振荡器相位漂移会随通道和时间的变化而变化。使用不同的架构可以生成相干的射频LO信号。

射频LO分布:LO信号由一个共同的LO产生,然后分布在系统中。但因为频率较高,这实施起来并不简单,射频损耗和射频耦合使其变得相当困难。

参考时钟分布:为了避免射频损耗,会在本地生成LO信号。但是,由于锁相环或压控振荡器(VCO)之间存在差异,要同步单个生成的LO信号,还需要付出更多努力。

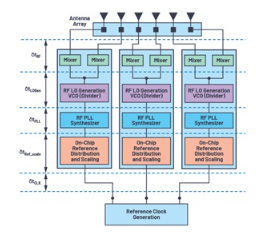

图2显示了一个多通道和多天线射频子系统架构示例,该架构是基于集成式收发器芯片。其中包括一个片上频率合成器(一个锁相环)和一个VCO,用于生成射频LO。参考时钟在收发器芯片外部生成,然后分别分配给每个芯片的器件时钟输入。在芯片上完成对参考时钟的进一步扩展和分配。图2分解显示从系统参考时钟到天线的传输路径。该路径可以分为不同的段,每个段都造成传输延迟。传输延迟的变化会引起系统相位差的变化,从而影响系统的相位相干性。

图2. 多通道和多天线系统中的相位缺陷来源。

我们采用校准技术来消除这种真实缺陷。通过使用校准方法,我们确定未知因素,然后加以校正。在相控阵和大规模MIMO系统中,由于相位差的存在,各个射频通道的频率响应各不相同。此外,它本质上是随时间变化的。通过出厂校准,可以补偿系统中可以测量的静态因素。使用初始校准,可以消除与部署相关的因素,在系统每次启动时,也可以运行这种校准。为了消除动态和时变因素的影响,需要定期对天线进行校准。除了温度漂移外,LO相位漂移也是这样一个动态因素,会随通道和时间变化。如果在运行期间执行这些校准,它们会消耗宝贵的系统资源,例如时间频率。因此,产生了一个优化问题:用最少的资源进行校准,以最大化系统性能。

使用射频锁相环相位同步特性简化校准

ADRV9009 是ADI公司的 RadioVerse® 产品系列中的一款双通道、高度集成的软件定义无线电。它提供两个发射和两个接收通道,分别将数字IQ位转换为射频和将射频转换为数字IQ位。它基于零中频架构,该架构能够最大限度降低系统功耗,并提供出色的发射机和接收机射频性能。此器件可在不使用外部组件的情况下,使用片上功能生成完整频率。其中包括三个片上频率合成器,射频LO合成器为其中之一。每个合成器都有一个集成式VCO和一个环路滤波器。在整个受支持的频率范围内生成频率时,这种高度集成和出色性能能提供很高的灵活性。

在数字端,ADRV9009采用JESD204B协议作为执行数字数据传输的串行接口2。它利用JESD SYSREF信号,从内部支持多芯片同步。因此,可以创建大规模相控阵和大规模MIMO系统。

除了多芯片同步,ADRV9009还提供射频锁相环同步特性,使内部生成的LO信号具有相位相干性,且与采用的参考时钟一致。基于这个特性,可在大规模系统中轻松实现以下这些功能:

上电时相位相干:在每个上电周期,实现恒定不变、确定性和稳定的相位值

运行期间相位相干:在启动之后跟踪相位值

多器件之间相位相干:进一步支持多芯片同步

校准算法需要占用数字硬件中的计算和存储器资源。例如,算法通常在基带处理链中实现,并利用FPGA/DSP资源。这个特性间接降低了系统校准所用的功耗和资源。因此,启用该特性可以优化整个系统的性能和效率。因为复杂的校准算法,系统从启动到达到稳定状态需要更长的时间。可以通过在启动时启用射频锁相环同步特性来最大限度缩短这个时间。会定期执行校准程序,以跟踪LO相位中的漂移,尤其是温度导致的漂移。否则,这些漂移会影响多天线系统的波束成型模式。借助射频锁相环同步跟踪特性,可以最小化校准频率,同时保持所需的波束成型性能。可以使用四种模式来控制相位同步特性:

模式1:禁用片上射频锁相环同步特性。

模式2:启用射频锁相环同步,仅用于初始化。

模式3:在初始化时执行射频锁相环同步,仅进行一次跟踪。

模式4:连续跟踪射频锁相环相位。

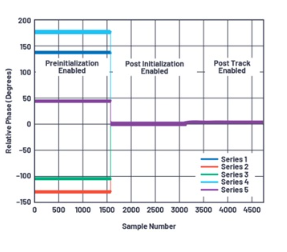

图3显示在多芯片和多通道环境下,在多次上电时测量得出的相位差结果。测量设置使用两个完全相同的评估板生成4个射频通道,其中一个是 ADRV9009-W/PCBZ。利用矢量网络分析仪,测量每个上电周期中发射机输出信号之间的相位差的变化。

图3. 通过射频锁相环相位同步周期,进行发射机输出相位比较1(射频调谐频率 = 1800 MHz)。

测量五次上电周期的值,并在不同运行模式下比较这些值。启动系统时,未启用射频锁相环同步特性。可以看出,在每个上电周期,相位都是随机的。在启用射频锁相环同步特性之后,所有5个相关相位值转换为公差为±2°的可重复值。启动连续跟踪之后,它以一定的延迟来保持该相关相位值。这种延迟导致相关相位增大1°至2°。所以,从图中可以看到少量漂移。利用此特性,可以在确定性公差内实现稳定的相位值。这会降低动态因素带来的影响,并简化系统的整个同步和校准过程。

结论

ADI公司提供的先进的高度集成软件定义无线电(包括ADRV9009双通道收发器)具备射频锁相环同步特性。如果使用此器件构建大型天线阵列系统,可以使用射频锁相环同步特性来简化天线校准。提供各种运行模式,可根据应用要求进行选择。可以使用软件API功能来轻松控制和配置该特性。ADRV9009用户指南1详细介绍了该特性的功能和使用方法。

审核编辑:郭婷

-

锁相环相位噪声的影响因素2024-07-30 5324

-

锁相环同步带与捕获带有区别吗?2024-01-31 3111

-

锁相环在相位检测中的应用2023-10-29 2176

-

模拟锁相环和数字锁相环区别2023-02-15 7005

-

LabVIEW锁相环(PLL)2022-05-31 8127

-

锁相环相位噪声与环路带宽的关系是什么2021-06-07 2690

-

PLL锁相环的特性、应用与其基本工作过程2017-05-22 13918

-

锁相环相位噪声与环路带宽的关系分析2012-11-22 24910

-

多速率锁相环相位同步方法的研究2011-12-28 1085

-

模拟锁相环,模拟锁相环原理解析2010-03-23 6341

-

模拟锁相环与载波同步实验2009-04-01 9691

-

锁相环的原理,特性与分析2008-08-15 11472

-

锁相环原理2007-08-21 5634

全部0条评论

快来发表一下你的评论吧 !