借助更多的选项响应正反馈

描述

负反馈什么时候会变成正反馈?当控制工程师想要实现不错的增益和相位裕度时。本博文概述第 4 代 SiC FET 如何为设计人员提供理想性能和多种器件选择,同时支持更高的设计灵活性,从而实现成本效益最优的功率设计。

这篇博客文章最初由 United Silicon Carbide (UnitedSiC) 发布,该公司于 2021 年 11 月加入 Qorvo 大家庭。UnitedSiC 是一家领先的碳化硅 (SiC) 功率半导体制造商,它的加入促使 Qorvo 将业务扩展到电动汽车 (EV)、工业电源、电路保护、可再生能源和数据中心电源等快速增长的市场。

反馈是件好事,控制工程师希望收到负反馈,以及良好的增益和相位裕度,而商人则更喜欢正反馈,比如:客户要求 750V 级 UnitedSiC 第 4 代 SiC FET 有更多的选项。UnitedSiC 的 18 毫欧和 60 毫欧器件在市场占据领先地位,但在有些应用中,更低电阻部件和更高中间值更有优势。这取决于具体应用和预算,导通电阻非常低的单个高端 SiC FET 占用空间非常小,装配起来也较简单,但将低成本部件并联也能得到相同的导通电阻,且通常也同样有效,尤其是有一些散热空间时。然而,这需要将器件并联,并需要更多的设计工作。

第 4 代 SiC FET 系列增添了更多部件

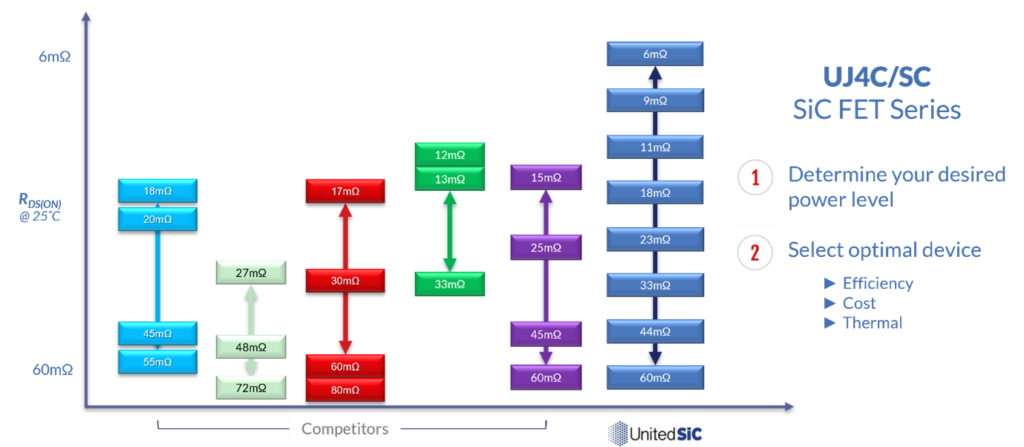

为实现这一灵活性,UnitedSiC 推出了导通电阻为 23、33 和 44 毫欧的第 4 代 750V SiC FET,以及 6、9 和 11 毫欧部件,这是在已推出的 18 和 60 毫欧器件的基础上做出的一次重大改进。如今,客户可以根据其特定的热力工况和运行条件进行混合搭配,以实现价格和性能的最佳组合,或许还可以根据应用需求或多或少地并联一些低成本部件,使其适用于不同设计,从而享受这些低成本部件的批发价格。

并联 SiC FET 很容易,而且栅极驱动功率非常低,使得并联产生的额外功率通常都无关紧要。由于这些器件的导通电阻具有正温度系数,所以自然能实现均流,此外还有一个额外的相关优势,即与单个 9 毫欧器件相比,两个并联的 18 毫欧器件的总传导损耗更低。这是因为与单个器件相比,这两个器件各流过一半的电流,产生的功率也只有一半,每个器件的温升也更低,而且导通电阻的增幅也会按比例减少。此外,随着结温的降低,可靠性也自然会提高,从而为已经很高的 SiC 最大值提供更多的裕量。UnitedSiC 基于网络的 FET-Jet 计算器现已推出第 2 个版本,可用于查看任意数量的并联 SiC FET 在各种应用和运行条件下的效果,并提供了一些实际损耗和温升的数据。

图 1:竞争激烈环境下 UnitedSiC 全新 750V SiC FET 系列新增产品

第 4 代 SiC FET 仍为行业领先技术

该系列的新增产品与旧有产品一样具有出色的品质因数,并采用了同样先进的第4 代制造工艺,比如:可减少基材传导损耗的晶圆减薄技术,以及可实现最低结-壳热阻和相应低结温的银烧结晶粒贴装技术。这些部件采用 TO-247 3 引脚封装,且在需要采用源极开尔文连接时,还可以使用 4 引脚封装。图1 总结了与SiC MOSFET 竞争产品相比,新型 750V SiC FET 的优势,并且不要忘了, SiC MOSFET的 额定电压仅为 650V。

UnitedSiC 750V SiC FET 系列提供更灵活广泛的部件选择,可用于许多应用。而且符合 AEC-Q101 汽车级认证要求,因此可用于牵引逆变器、车载和非车载充电器、DC/DC 转换器以及无线充电,以实现比 650V 额定部件更高的效率和电压裕度。在 AC 和 DC 固态断路器应用中,低传导损耗对提高效率和缩小尺寸至关重要,因此超低导通电阻具有重要价值。一般来说,在工业和 IT 功率转换产品中,第 4 代 SiC FET 还可以提高硬开关和软开关拓扑结构的性能。

请您继续提供反馈,UnitedSiC 已根据您的需求优化了环路补偿,以实现快速响应,提供更多的选项。

审核编辑:汤梓红

-

正反馈调节与负反馈调节的区别2025-01-18 11843

-

运放正反馈是不是比负反馈更加容易振荡啊?为什么啊?2024-09-05 935

-

正反馈调节与负反馈调节有何区别2024-08-30 16695

-

模电中正反馈和负反馈的区别2024-07-30 6218

-

为什么负反馈产生正电阻,正反馈产生负电阻?2023-09-20 3087

-

锁相环路中的反馈信号是正反馈还是负反馈呢?2023-04-13 1272

-

正反馈、负反馈傻傻分不清?2023-03-27 34812

-

如何判断放大电路中的正反馈和负反馈呢2021-10-08 3849

-

一文解析电流正反馈的电压负反馈调速系统2020-02-22 9600

-

运放电路中比较器的原理分析与正反馈介绍2019-04-19 25218

-

InstaSPIN-FOC正反馈为什么是bias-=2018-12-06 2319

-

正反馈回路和非最小相位系统根轨迹2009-07-27 4619

-

二阶带通正反馈滤波器2008-12-01 2133

全部0条评论

快来发表一下你的评论吧 !