终端端接在信号完整性中的意义

电子说

描述

终端端接对于信号完整性有着重要的意义,它和源端匹配一样都是解决信号完整性问题的重要手段。所以无论是高速的并行总线如DDR,还是高速串行总线如Serdes都会采用终端的端接。DDR的ODT功能就是典型的终端端接,而大多数Serdes采用的CML电平,在芯片内部的P、N两根线上都有50ohm的端接。

01

终端端接

源端匹配的作用就是:即使终端没有匹配,信号到达终端发生反射,返回的到源端的反射信号也会由于源端阻抗匹配而不会发生反射,从而消除了二次反射和多次反射的影响。

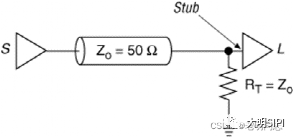

而终端端接则是让终端负载阻抗与传输线阻抗相匹配,使得初始电波进入到传输线直至到终端被接收器件接收一直处于匹配状态整个传输过程中都不会发生反射。

(a) (b)

终端端接有上图所示两种方式:(a)端接电阻RT 靠近负载端下拉到地;(b)需要两个端接电阻,R1 、R2 分别接到VCC和地。满足R1 ||R2 = Z0 或RT=Z0 即可实现阻抗匹配。

假设上面两种情况下源端阻抗和传输线匹配,接口的IO电压为VCC。那么进入传输线的初始电波只有1/2VCC。对于(a)接收的信号摆幅就是从0V到1/2VCC,其共模电平为VCC/4。对于(b)当R1=R2 时接收信号的摆幅就是1/4VCC到3/4 VCC,共模电平为1/2VCC 。

基于两种终端端接的上述特点,我们来分析两种情况的应用。

对于情况(a)来说无论是过驱动还是欠驱动情况,信号的低电平为0,高电平要小于VCC。是否能够应用这种匹配方式要看接收器件的电平接口VIL和VIH的值。比如,3.3V LVTTL电平的VIH = 2.0V,当欠驱动的情况下接收端的幅值肯定会低于1.65V,此时可能导致接收高电平错误。

对于(b)由于其共模电平为1/2VCC,接收信号高低电平以1/2VCC为中心,这种匹配方式适合用于SSTL或者HSTL这种基于比较器的结构的电平接口。DDR2、DDR3以及QDR的DQ信号内部的ODT端接就采用(b)所示的戴维南端接。

需要注意的是,端接的值并不一定非要和传输线阻抗完全匹配。端接阻值越小时接收器件接收的信号幅值也就越小,端接阻值越大时接收器接收信号幅值越大。端接阻值选择多大合适要通过仿真结合信号的噪声裕量来确定。

如下图所示为不同终端端接的仿真波形。(蓝色为ODT120,黄色ODT60,绿色为ODT40,红色为ODT20)。

如上所示,ODT20的情况由于端接20ohm比50ohm传输线阻抗要小得多,在终端发生负反射使信号的幅值减小,此时信号的噪声余量比较小。如果有其它的噪声例如串扰、电源噪声等就可能会使信号质量带来风险;ODT40和ODT60的情况端接阻抗与传输线阻抗最接近,阻抗不连续性不是很大,所不同的是ODT60情况发生正反射,ODT40发生负反射,因此ODT60要比ODT40情况信号幅值大一些噪声余量也要大一些;ODT120的情况下端接和传输线阻抗不匹配程度很大,但是信号幅值较ODT60进一步提高。但由于阻抗不连续性过大使其眼皮比较厚相比ODT60的情况噪声余量增加并不明显。

对于DDR信号的ODT配置的选择需要具体问题具体分析,当信号链路比较短的情况可以不用ODT功能,因为此时传输线效应并不明显阻抗不连续的影响不大;当信号线比较长时,能够体现传输线特性,如果源端匹配和链路其它匹配做的都很好的情况下,此时只有终端会发生一次反射也可以不用ODT功能。

当源端匹配做的不好或者链路上存在很多阻抗不连续点的情况下就需要启用ODT功能了,具体配置需要根据仿真结果来确定。另一方面并不是说开启ODT功能就一定能够得到比关闭ODT功能时更大的噪声余量和时序裕量,而且也不是所有的信号质量问题都能通过开启ODT来解决。

对于速率不算太高的DDR3来说,有时我们会发现好像ODT OFF时的结果都比ODT ON时要好。这是为什么呢?

首先接收端接收到的波形为入射电压和反射电压的叠加,如下所示:

入射电压一定的情况下,反射电压的大小正负取决于终端的反射系数。

DDR3的ODT结构如下图所示。这里的R1\\R2就相当于DDR3的ODT值。

DDR3的ODT 值有20、40、60、120ohm以及ODT off等值,不同的ODT配置造成的影响就是终端反射系数不同。、

ODT20,ρ= Vref / Vinc= (20-50)/(20 +50) = -0.428,负反射使接收信号幅值减小;

ODT40,ρ= Vref / Vinc= (40-50)/(40 +50) = -0.111,负反射使接收信号幅值减小;

ODT60,ρ= Vref / Vinc= (60-50)/(60 +50) = 0.091,正反射使接收信号幅值增大;

ODT120,ρ= Vref / Vinc= (120-50)/(120 +50) = 0.411,正反射使接收信号幅值增大;

ODT OFF,ρ= Vref / Vinc = (∞ - 50)/(∞ + 50) = 1,全反射使接收信号幅值加倍。

由此可见当链路比较短或者其它地方不存在反射的情况下,信号的幅值完全取决于末端的反射系数,即ODT的配置。当ODT OFF情况下信号的幅值最大上升下降边沿最陡因此其眼宽最宽。但是链路中的阻抗不匹配也会增加信号的过冲和振铃,当线路很长或者阻抗不连续点很多时就有可能ODT OFF的情况要比ODT ON要差。

-

IDT信号完整性产品:解决高速信号传输难题2026-03-04 620

-

高速电路中的信号完整性和电源完整性研究2024-09-25 486

-

为什么电路端接电阻能改善信号完整性?2023-10-24 2209

-

信号完整性分析科普2023-08-17 9236

-

高速电路信号完整性分析与设计—端接与拓扑2022-02-10 858

-

何为信号完整性?信号完整性包含哪些2021-12-30 2873

-

详解信号完整性与电源完整性2021-11-15 2557

-

信号完整性与电源完整性的仿真2021-09-29 1646

-

信号完整性设计中的5类典型问题(于博士信号完整性)2017-01-22 1244

-

示波器信号完整性的意义2016-03-02 2776

-

信号完整性与电源完整性的仿真分析与设计2015-01-07 7034

-

信号完整性与电源完整性仿真分析2011-11-30 2109

-

信号完整性原理分析2009-11-04 1287

-

什么是信号完整性2009-06-30 5874

全部0条评论

快来发表一下你的评论吧 !