直接在网表中插入RTL来快速做芯片功能ECO

EDA/IC设计

描述

重新综合时间太长?

近几年,芯片设计规模越来越大,这使得重跑一次综合需要长达数小时,甚至几天时间。

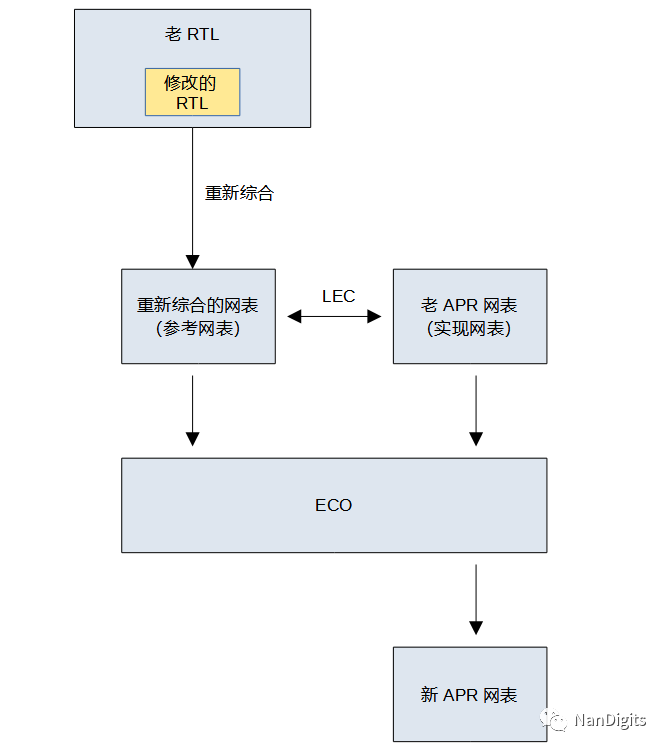

传统的自动功能ECO流程需要把修改后的所有RTL(包括修改过的和没有修改过的)重新综合成参考网表,如下图。即使是RTL层面很小的、非常简单的修改,也必须重走一遍综合流程。重新综合会消耗大量的时间,尤其对于大型项目,重新综合会严重影响芯片功能ECO的进度。

一种全新的解决方案

针对这种场景,我们想到了一种解决方案: 直接在需要ECO的网表 (比如APR网表) 里插入RTL代码 。

我们来看下面这个例子,比如ECO时需要对DFF的D端的net wr_data_7_做一些预处理。下图是原网表。

我们在网表里直接插入了RTL的always语句,对wr_data_7_进行了打拍和简单逻辑处理(新加的逻辑所需要的输入信号都可以在原网表中找到),把处理后的信号wr_data_7_new_d接到原DFF的D端,如下图中的箭头。这种在网表里直接插入和修改的RTL也叫做RTL补丁。

GOF ECO读入包含插入RTL补丁的网表,做递增式综合。递增式综合会根据RTL补丁的改动,对网表做必要的修改。所以,最终的ECO网表里就精确反映了逻辑补丁。当处理相对简单,单一的逻辑修改时,传统的方法是摘取这个修改的代码片段为一个新的module,对这个新模块进行综合,再把综合得到的网表片段(也叫逻辑补丁)插回原网表里,如下图。有一个要特别注意的是,插回网表时net名字可能冲突。

GOF ECO提供了一种全自动化的、可行的解决办法来在网表里直接插入RTL补丁,来帮助递增式综合。在递增式综合过程中,GOF ECO只针对RTL补丁,不影响网表的其余部分,这可以最小程度地影响原网表。采用这种方法,GOF ECO可以生成更优化的网表,同时也尽可能保留原网表的结构和格式。

这种方法不需要完整的重新综合,就可以把RTL修改的部分无缝的集成到原网表里。所以,只有设计中有修改的部分才会做递增式综合,这会显著地节省完整的重新综合所需要的时间。

利用递增式RTL补丁做功能ECO的方法,前端设计工程师也可高效地做功能修改,而不用担心影响项目进度。这种方法是最佳的ECO实现方案,它不仅能把插入的RTL递增式综合成网表补丁,还可以尽量保持原网表的完整性。

GOF ECO还提供了更多插入RTL的便捷方法

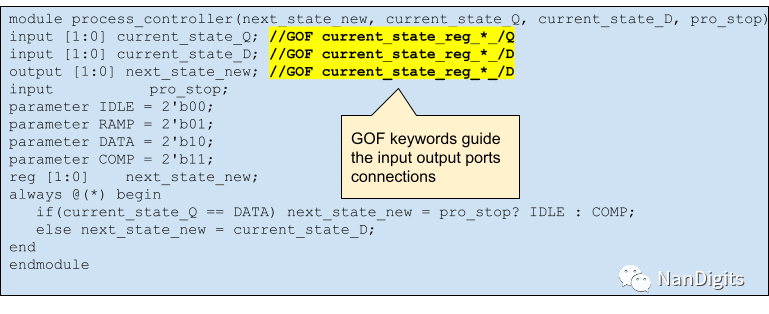

如下图,在写独立RTL补丁文件时,GOF ECO提供了一些便捷方法: 在module端口声明的后面用特殊的注释来指明连接关系 。这个例子中,通过注释指明了补丁模块信号与状态机如何连接。GOF ECO读到RTL补丁中的这些特殊注释后,会自动执行对应的修改和连接。

生成最终的ECO网表

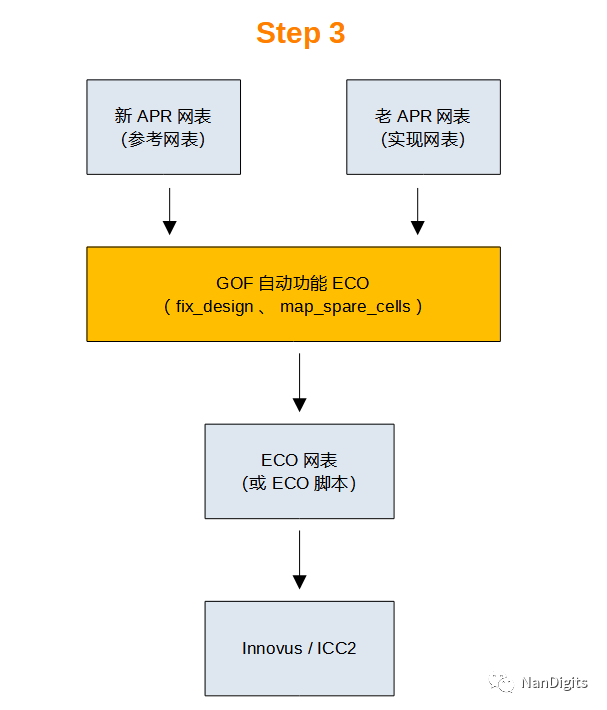

最后,我们利用Step2得到网表作为参考网表,对原APR网表进行自动功能ECO。从RTL补丁到网表补丁、再map成spare cells补丁,这样我们就得到最终的ECO网表或者ECO脚本(根据情况二选一即可)。

-

RTL8309SC ***原装进口 瑞昱 芯片 光耦IC 以太网控制芯片 电子元器件2016-06-03 3738

-

LabVIEW谁又没有交流群》直接在网上下载的LabVIEW8.5可以用吗2017-03-18 2593

-

有利于验证未测试功能的RTL缓冲器插入和故障分级技术2009-03-28 927

-

如何在CAD中插入光栅图片2012-10-22 22109

-

如何在Vivado中执行工程变更命令 (ECO)2018-11-21 5910

-

ECO技术在SoC芯片设计中的应用2021-04-07 1978

-

自动ECO参考网表来自动修改实现网表2021-09-08 4504

-

详解Xilinx FPGA的ECO功能2022-08-02 5395

-

直接在Google表格中的血压监测仪2022-11-10 1052

-

什么是DFT友好的功能ECO呢?2023-03-06 3780

-

解析什么是DFT友好的功能ECO?2023-05-05 3178

-

直接在网表中插入RTL来快速做芯片功能ECO2023-06-06 3696

-

时序(Timing)对功能ECO有多重要2023-07-05 2870

-

光纤直接插入芯片,速度和效率惊人!2023-12-21 2252

全部0条评论

快来发表一下你的评论吧 !