探讨一下菊花链拓扑结构

电子说

描述

对于点到点拓扑我们只需要注意选择合适的匹配方式,并优化好整个channel的阻抗即可,但是当一个网络上的器件超过两个时,信号可以选择的拓扑结构就会变得非常丰富了。此时如何根据信号特性以及器件的布局布线等约束选择合适的拓扑结构和匹配方式就变得尤为重要。对于PCB板的布线瓶颈处的布线拓扑选择就可能对PCB板的所需的布线层数起到决定性作用,这直接关系到产品的成本;而对于一些关键的高速总线接口的拓扑结构选择又关系到系统的性能指标。因此,在实际的产品开发中多负载拓扑结构的选择意义重大,可能直接关系到产品的成本、性能等竞争力。

01

菊花链拓扑简介

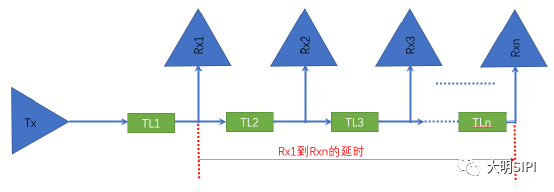

菊花链是比较常用的一种拓扑结构,它将各个负载端依次相连。

如上图所示,当Rx1到Rxn的互连线不能表现出传输线效应时,用菊花链拓扑是一个非常好的选择。也就是说当负载的位置相对比较集中,也就是最靠近驱动器的负载(Rx1)和最末端的负载(Rxn)之间的布线延时小于信号上升时间的1/6时,用菊花链拓扑结构会比较好。此时可以近似的认为Rx1和Rxn之间是集总的。因此,有好多低速的总线都是走的菊花链拓扑,如I2C、JTAG等总线,信号速率低、上升时间往往是ns级的,往往负载会很多,这个时候菊花链就是比较好的选择,一般也不会出什么问题。

一些老资格的硬件或者layout工程师往往认为这种低速信号可以随便走,不会出问题。的确,对于一个上升时间2~3ns的信号,如果布线延时不足0.5ns时不会有什么问题,但如果系统更大,布线更长的时候就可能出现问题,此时就需要SI仿真来解决问题。

更有甚者,PCB设计都没有变,老版本运行正常,而新版本的单板由于使用了工艺升级后的器件就问题频出,这又是什么原因呢?

其实,问题就出在芯片的工艺升级上了。同样一个驱动器老版本的使用28nm工艺,新版本使用14nm工艺,新的工艺驱动能力更强信号的上升时间更短。使得老版本上没有体现出传输线效应的互连线体现了传输线效应,从而导致了SI问题。

那么,还是让我们来仔细探讨一下菊花链拓扑吧。下图为菊花链拓扑结构的示意图,同时也对拓扑结构中各个点的信号特点进行了说明。

假设拓扑结构中驱动器的输出阻抗和传输线阻抗Z0匹配,驱动器的IO电压为VCC,此时T0点的入射电压幅值为VCC/2在链路的末端(负载3)发生全反射,反射电压的幅值也是VCC/2。在这种拓扑结构下我们可以发现各个负载所接收到的信号的特点。

(1)驱动器和传输线的阻抗匹配情况决定了传输线入射波的电压和反射情况。假设驱动器输出阻抗和传输线阻抗匹配,入射波只在末端发生一次反射;

(2)首先负载3处入射波和反射波之间没有延时因此得到的信号边沿单调。同时正是因为入射波和反射波完全重叠,导致如果驱动能力过强导致入射波和反射波都存在过冲的话,最末端的负载3的过冲也会是最大的,边沿斜率是最陡的。

(3)在负载2和负载1处则会由于入射波和反射波之间存在的延时而导致接收到的信号存在台阶或者回沟。由上面的示意图我们不难理解当驱动器和传输线阻抗匹配时在负载2和负载1处有可能出现台阶,欠驱动情况下可能只是使信号边沿变缓,而在过驱动情况下信号边沿就有可能会出现回沟了。TD2等于2倍的TL3的延时, TD1等于2倍的TL2+TD3的延时,TD0等于2倍的TL1+TL2+TD3即整个网络的总延时。由此可知越靠近源端的负载接收到的信号在边沿处存在的回沟或者台阶就越大。

另外在负载端是否会产生台阶或者回沟不仅和负载到拓扑最末端的延时有关,而且还和驱动器输出信号的上升下降时间有关。当负载到拓扑末端的延时小于信号上升时间的1/3时就不会在负载处观测到明显的台阶或者回沟,但是负载到拓扑末端的延时超过上升时间的1/3台阶或回沟就会变得明显起来。

使用3.3VLVCMOS的驱动器和负载进行仿真。设置TL1 = 2000mil,TL2、TL3都是长度为1500mil的50ohm传输线。信号线的延时按照170ps/inch进行估算,此时负载1到末端的延时TD1/2为510ps、负载2到末端的延时TD2/2为255ps。我们通过IBIS模型中的[Ramp]关键字得到驱动器输出上升时间为500ps左右,下降时间1ns左右(具体计算方法参见第七章IBIS模型介绍);通过IBIS模型的pullup、pulldown曲线来估算驱动器输出阻抗为20ohm。分别在过驱动、阻抗匹配、欠驱动三种情况下进行仿真分析

驱动器输出未加匹配电阻时即为过驱动情况,仿真结果如下:

三个负载处的接收波形如上所示。蓝色点虚线为负载1处的波形,其上升沿都存在1ns左右的回沟,下降沿隐约有些台阶但并不明显。这是由于驱动器输出的上升沿要比下降沿快,所以负载1到末端的延时和上升时间相当但却只有下降时间的一半。负载1处的波形过冲幅值是最小的;红色短划虚线为负载2处波形,只表现出了上升下降边沿比较缓并没有明显的台阶,其过冲比负载1处的稍微大一些;绿色实线为负载3处的波形,边沿单调且斜率最大,同时过冲也达到了最大值。由于过冲和振铃的存在使信号的噪声余量也有了明显地降低。下面再对阻抗匹配的情况进行仿真我们就可以知道阻抗匹配的重要性。

驱动器输出添加30ohm匹配电阻使输出阻抗匹配,仿真结果如下:

如上所示,此时所有负载端的过冲和振铃都消失了,而且负载1上升沿的回沟也变成了台阶。可见阻抗匹配在菊花链拓扑中也具有重要的作用。欠驱动的情况这里不再分析,有兴趣的读者可以自行验证。其实驱动器的输出阻抗一般都会比传输线阻抗要小,过驱动是普遍存在的情况,如果过冲振铃能够满足要求我们一般可以不考虑阻抗匹配了,当信号质量不可接受时,我们才会选择加串阻来解决阻抗匹配问题,并不会故意设计成欠驱动的情况。

显然菊花链拓扑所产生的回沟或台阶的危害性是非常大的。对于数据信号回沟或台阶会影响信号的时序裕量,对于时钟信号如果存在回沟,很可能会被接收器件识别成双时钟沿,此时钟再去采数据就会产生错误。因此,这种菊花链拓扑只能应用于低速总线中。

02

菊花链拓扑信号质量改善

如何来改善菊花链拓扑结构的信号质量,可以从下面几个方面考虑:

1、明确驱动器的上升下降时间后,可以考虑将离驱动器最近的负载到最末端的负载的延时控制在上升下降沿的1/3以内。如果是时钟信号只是上升沿采样那么我们只需关注上升时间即可。但这一点往往很难做到,像PCI、local BUS、JTAG、IIC等低速总线上的负载往往很多而且布局位置可能分布在PCB板各个位置,距离会比较远。

2、在菊花链的末端加戴维南端接消除拓扑末端的反射,进而可以消除靠近驱动端的负载的台阶或者回沟。这种拓扑结构也是DDR地址控制信号fly-by拓扑的雏形,使其有应用于高速并行总线的可能。

但是需要注意,通常在戴维南匹配中选择R1=R2且R1||R2=Z0,源端如果匹配的情况下接收信号的低电平为1/4VCC、高电平为3/4 VCC,高低电平到VIH和VIL的余量会大大地减小。因此,如果是CMOS或者LVTTL电平,使用戴维南匹配源端不必做阻抗匹配保持过驱动就可以了。

戴维南匹配示意图如下:

如上所示末端的戴维南匹配消除了末端反射,使得每个负载接收到的波形都和入射波形基本一致,且边沿单调没有台阶和回沟以及过冲。此时入射波的幅值就决定了负载端的电压幅值以及高低电平的噪声裕量,驱动器的驱动能力越强、输出阻抗越小负载接收到的信号幅值就会越大。

使用戴维南端接只是消除了拓扑最末端的反射,实际的拓扑中存在着很多阻抗不连续的点,我们很难将他们一一消除,这将付出非常大的代价。比如说每个负载处都会有负载的fanout过孔和很短的分支布线,当负载比较少只有2~3个时我们可以不必在意,但是如果整个拓扑的负载有很多甚至达到7、8个甚至10个以上那么这些过孔分支布线带来的影响就必须重视了。

我们需要研究在布线的分支处到底发生了什么。入射波在分支点处同样会发生反射。入射波在分支点处向右看过去的阻抗相当于负载处的Stub和TL2并联ZT=Z0||Z0=0.5*Z0,此时在分支点处发生反射系数为(0.5Z0-Z0)/(0.5Z0+Z0) = -1/3的负反射,这一反射只是在入射信号经过分支点处的瞬间发生过了分支点后的阻抗依旧是连续的。因此,这一反射会在信号的边沿产生一个微小的台阶或者回沟。

负载少时这种影响并不显着,当拓扑中的负载非常多时就会严重影响信号质量哪怕是再末端加戴维南匹配也不能完全消除反射。

3、在存在台阶或者回沟的负载端加串阻消除回沟或者台阶。

在点到点拓扑的分析中已经介绍了在末端加串阻能够消除过冲和振铃,同样也能够消除回沟和台阶,但这都是需要牺牲信号边沿斜率。在介绍菊花链拓扑时我们做的仿真中负载1上升沿存在严重的回沟,那么我们在负载1处加一个串联电阻Rs =100ohm,拓扑如下所示:

如上所示红色短划虚线所示为未加串阻Rs的波形,此时上升沿存在明显的回沟;蓝色点虚线所示为加200ohm串阻的波形上升沿的回沟已经消除只是稍有台阶;绿色实线所示将串阻Rs增大到了400ohm,此时台阶进一步减小。此外我们也可以观测到随着串阻的阻值增大负载1接收到的波形边沿越来越缓。

4、驱动器端加到地的电容Cp,增大输出信号的上升下降时间也可以改善负载端接收的波形;

对不同容值的Cp进行仿真,对比负载1的接收波形如下所示:

如上所示蓝色短划虚线所示为未加Cp时的波形,此时上升沿存在明显的回沟;红色点虚线所示为Cp=10pF时的波形,上升沿的回沟已经消除只是稍有台阶;绿色实线所示将Cp增大到20pF,此时台阶进一步减小。此外我们也可以观测到随着Cp的容值值增大负载1接收到的波形边沿越来越缓。负载的容值可以根据回沟的大小经过仿真来确定。

以上这些解决菊花链拓扑信号完整性问题的方法需要在具体的设计中灵活应用,如果始终不能解决问题那就需要考虑更换信号的拓扑结构。

-

为什么多片DDR菊花链拓扑连接时末端需要接很多的电阻2023-12-29 2173

-

DDR拓扑结构的详细解析2023-12-26 2976

-

菊花链通讯信号的波形?怎么样判断波形的质量?2023-08-03 23747

-

请问什么是菊花链的概念?2019-07-01 8583

-

请问不同蕊片可以设计成菊花链方式进行仿真吗?2018-12-24 1334

-

SDRAM的电源系统及拓扑结构2018-12-03 2735

-

高速PCB布线拓扑2018-11-27 2610

-

我的板子之前是按照fly-by拓扑(菊花链)布线,之后板子缩小打算用T行拓扑布线,有用过的大神知道可以直接更改吗?2018-05-28 5302

-

两种拓扑结构的区别和注意要点2018-04-28 18926

-

菊花链拓扑的结构是以及与星形拓扑结构的区别2017-11-10 114602

-

菊花链拓扑的结构是什么样子的?2017-11-08 35204

-

快点PCB原创∣聚焦SI问题之总线拓扑结构2016-10-14 3041

-

DAC菊花链的意义2016-09-02 5170

-

【分享】Altium 4层核心板(菊花链拓扑)案例2016-08-20 61221

全部0条评论

快来发表一下你的评论吧 !