树形拓扑结构的设计关键点

电子说

描述

树形拓扑也是一种非常常见的拓扑,DDR2的内存条中地址控制信号经常使用这种拓扑。虽然现在信号的速率越来越高,DDR5的速率已经达到了6400Mbps,早已不再使用树形拓扑。但学习树形拓扑,了解其中的设计关键点也有助于我们分析解决其它信号完整性问题。

01

树型拓扑介绍

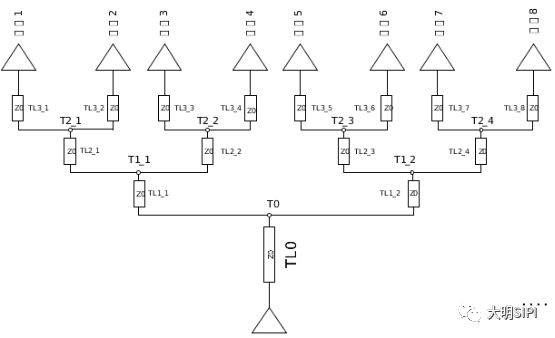

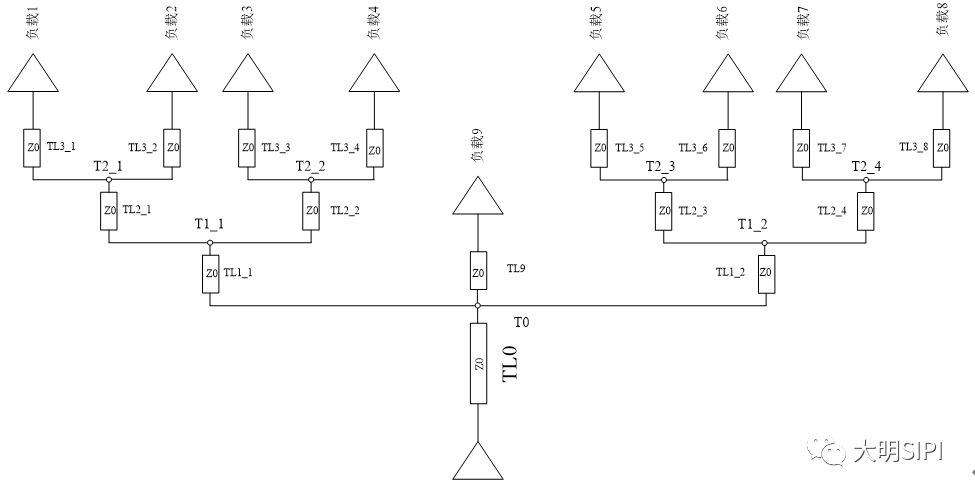

对于DDR2接口以及DDR2的DIMM设计中,地址控制信号通常使用的是树型拓扑。如下图所示即为树型拓扑的示意图,树型拓扑也是一种对称拓扑,相对于远端簇拓扑来说树型拓扑分支点处的阻抗突变要比较小。但是很明显树型拓扑的分支点要多很多,这就限制了树型拓扑的应用。

下面以上图所示的八个负载的拓扑为例对树型拓扑结构特点做一个简单的归纳:

(1)负载越多分支点越多,上图链路中有T0、T1_1\\T1_2、T2_1~T2_4一共七个分支点为阻抗不连续点;

(2)假设所有传输线阻都为Z0,每个分支点前后的阻抗突变固定。分支点前阻抗为 ,信号到达分支点后感受到的阻抗为两条分支线的并联阻抗,即:

,信号到达分支点后感受到的阻抗为两条分支线的并联阻抗,即:

可以计算得到在分支点处入射波反射系数均为- 。

。

(3)此外,从各个负载反射回源端的反射信号到达各个分支点会发生反射,且各个分支点之间也会有反射信号。如果T0到T1_1\\T1_2的延时、T1_1\\T1_2到T2_1T2_4的延时以及T2_1T2_4到各个负载的延时过大(超过信号上升时间的1/3,体现明显的传输线效应)都会导致信号质量的恶化。

(4)当T1_1和T1_2、T2_1~T2_4控制严格等长的情况下,拓扑结构对称各个负载接收波形一致性很好。

02

树型拓扑仿真分析

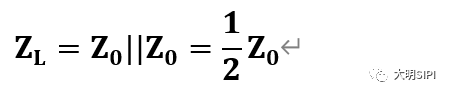

我们在ADS中搭建DDR2地址信号的仿真电路进行分析。驱动器和负载的选型与远端簇仿真分析相同。对拓扑结构中的线长做如下设置:(1)TL0=2000mil,(2) TL1_1\\TL1_2长度为1000mil;(3)TL2_1TL2_4长度为700mil;(4)TL3_1TL3_8长度为500mil。

图1.树型拓扑ADS仿真电路

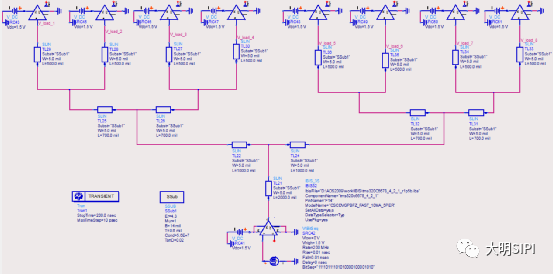

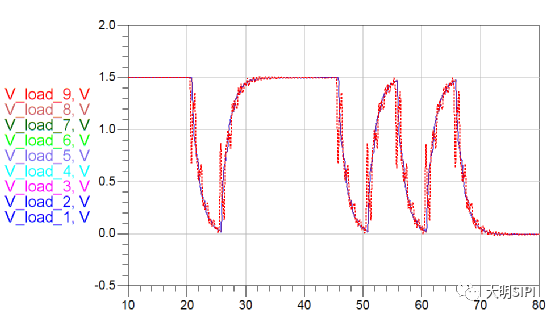

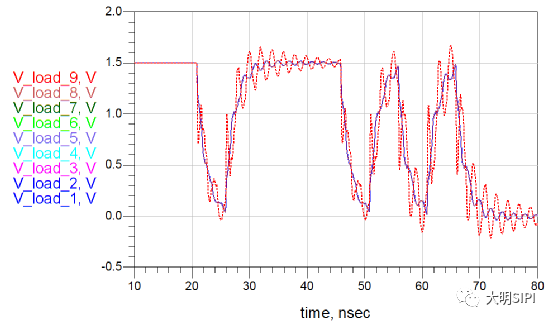

图2. 速率400Mbps,各个负载的仿真波形

信号边沿单调、但是由于负载过重负载端接收的信号边沿过缓,这是由于树型拓扑这种一分二、二分四的拓扑结构使得整个拓扑中布线的总长度会非常长也使布线引起的容性负载会非常大。如果PCB设计中允许双面布局我们可以将负载1和2、3和4、5和6、7和8分别进行正反对贴布局,也就是top面布负载1、3、5、7,bottom面布局负载2、4、6、8。这样的话可以极大地缩小布局面积和每一级分支的布线长度,减小布线的容性效益。

另外,同样需要注意分支布线的延时过大会在信号边沿产生回沟或者台阶影响数据信号的时序裕量和时钟信号的边沿单调性。尤其是TL3_1~TL3_8的布线长度对信号质量的影响非常大,有兴趣的读者可以自行验证。树型拓扑结构的设计规则也更加复杂,信号完整性工程师需要综合器件的布局和层叠设置等因素给出信号质量满足设计要求的拓扑结构,并对线路各个部分的阻抗、分支长度等作出详细的约束规则,否则很容易导致设计的失败。

02

树型拓扑的变型

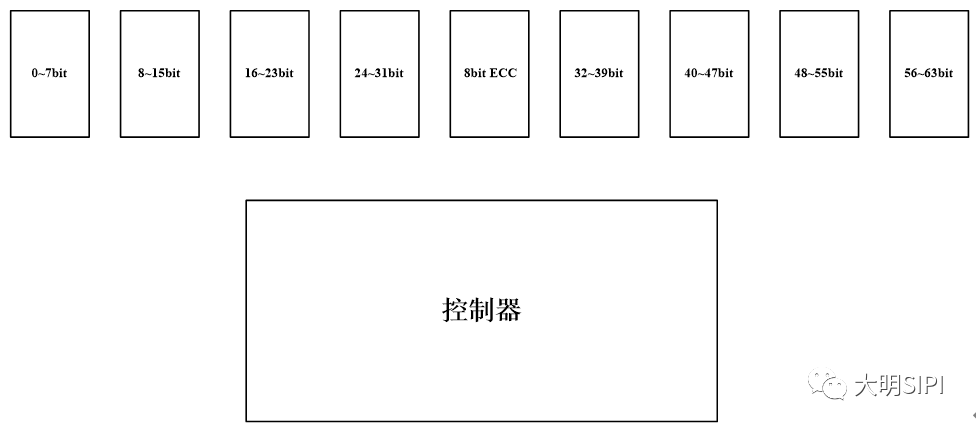

树型拓扑的一分二、二分四的拓扑结构使得负载的数量必须是2、4、8、16等值,也就是 2的n次方(n为正整数)。但在实际的应用中通常会遇到负载的个数不是 的情况。比如说带有ECC功能的DDR2接口。对于一个64位的DDR2总线需要8片8位的DDR2颗粒组成,但如果要增加ECC功能就需要再增加一片DDR,此时整个拓扑的负载个数就是9个。那么我们应该为地址控制信号选择什么样的拓扑结构以使信号质量达到最优。在控制器和内存颗粒的布局时,我们通常是将ECC DDR2颗粒布局在最中间的位置。如下所示:

的情况。比如说带有ECC功能的DDR2接口。对于一个64位的DDR2总线需要8片8位的DDR2颗粒组成,但如果要增加ECC功能就需要再增加一片DDR,此时整个拓扑的负载个数就是9个。那么我们应该为地址控制信号选择什么样的拓扑结构以使信号质量达到最优。在控制器和内存颗粒的布局时,我们通常是将ECC DDR2颗粒布局在最中间的位置。如下所示:

此时我们在布线时最容易选择的一种拓扑结构就是将ECC芯片的fanout过孔作为地址控制信号树型拓扑的第一个分支点。这种拓扑结构看起来似乎很是最合理的,相对于树型拓扑改动很小,并不会改变原有的布线层叠设置,不会因为多出的一片DDR导致布线层数的增加,而且拓扑对称性好。但事实上这种拓扑是否能够满足信号完整性要求呢?

图3.一驱九的DDR2拓扑

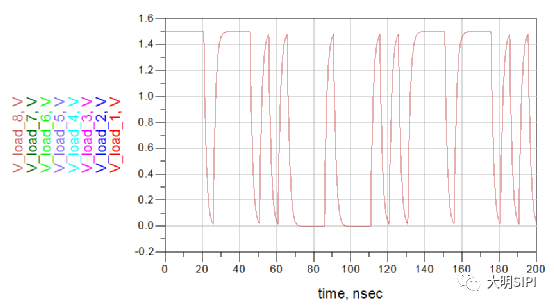

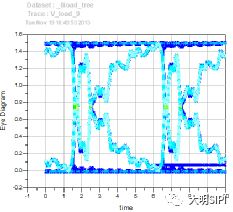

在图.3树型拓扑的基础上按照图.3树型拓扑变型所示的方式增加一个ECC DDR负载9,设置TL9布线长度为100mil进行仿真(仅为fanout线长度)。仿真的结果显示负载1~8的接收波形完全一致能够满足信号质量的要求,但是负载9的接收波形无论是信号的边沿还是高低电平处都存在着很多的回沟振荡严重影响信号的噪声裕量和时序裕量。

图4.树型拓扑变型仿真结果(TL9 = 100mil)

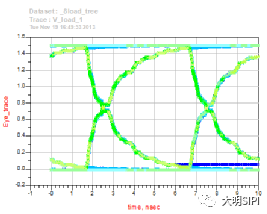

图5.(左)负载9的接收眼图;(右)负载1的接收眼图

负载1~8的波形非常一致而且信号质量非常好这并不难理解,但为什么负载9接收的信号质量最差呢?

其实无论拓扑中有没有负载9在第一个分支点T0处信号波形都是很差的,我们可以在8个负载的树型拓扑结构中进行验证观测一下T0点的信号波形。究其原因就是因为T0点作为第一个分支点是拓扑的主干路上的分支点,所有负载、以及其它分支点处发生的反射都会汇聚到这一点,从而对这一点附近的负载接收信号的信号质量产生影响。

如果这样的话是否可以考虑将TL9的长度设置为2300mil(TL3+TL2+TL1)这样负载9到分支点的延时从表面上来看就和其它负载一致了。我们再来看一下仿真结果,点虚线为负载9接收波形、实线为其它负载接收波形。

图6.树型拓扑变型仿真结果(TL9 = 2300mil)

调整TL9长度后并没有使负载9的信号质量好转,反而使其它负载的信号质量也恶化了。由此我们可以得出结论:将ECC芯片放在拓扑结构的中间并不合适,我们需要重新设计地址控制线的拓扑结构。

有人可能会提出我们可以采用一分三、三分九的拓扑这样应该可以解决现在的问题。但需要注意这样做会导致PCB设计难度甚至PCB板成本的提高,如果有兴趣可以自行验证一下。

-

LABVIEW递归获取列表显示到树形结构2025-08-07 5162

-

树形结构2012-11-29 16572

-

labview树形结构问题2012-12-05 14318

-

labview树形结构值编辑 求教2016-08-07 8863

-

树形结构输出数值2017-05-19 2084

-

labview树形结构2017-08-11 5984

-

拓扑结构,拓扑结构有哪些类型?2010-03-22 13288

-

ddr3菊花链拓扑结构是什么2017-11-08 26047

-

什么是电路拓扑结构_多种pfc电路的拓扑结构介绍2018-01-23 56091

-

PROFINET网络支持星型、树型、总线型、环形和混合型网络拓扑结构2018-07-10 25535

-

ZigBee模块通信协议的树形拓扑组网结构2022-06-10 4030

-

DDR PCB设计布线时,拓扑结构的选择2022-11-27 2747

-

网络拓扑结构哪三种2023-03-07 7058

-

ZigBee模块无线通信组网结构技术之Mesh拓扑网状2023-05-30 690

-

蓝牙低功耗树形结构网络2024-09-26 337

全部0条评论

快来发表一下你的评论吧 !