SoC设计之功耗—IR drop

嵌入式技术

描述

SoC电源/地网络给整个芯片供电,一个设计合理的电源/地网络要保证整个芯片的性能和可靠性。如果在电源/地网络上引入了噪声,可能导致电路逻辑上的错误或速度延迟。这个电源噪声就是我们今天要讨论的IR drop,也叫voltage drop。

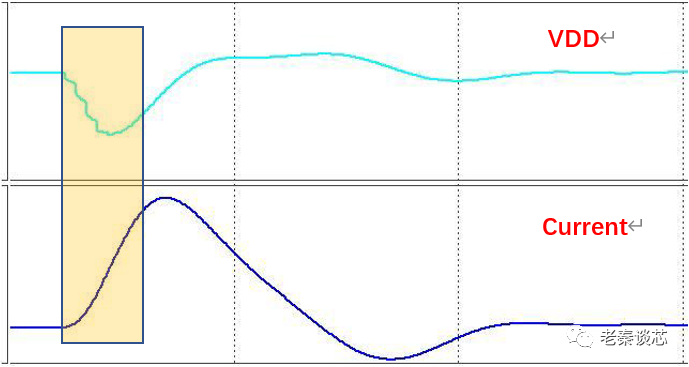

我们先从原理上看IR drop是如何产生的。首先,当芯片上各种功能电路同时工作时,稳压电源模块无法实时响应负载对于电流需求(demand current)的快速变化,芯片上的电源电压VDD发生跌落,从而产生电源噪声。考虑到电源和地之间的耦合效应,VSS也会相应的抬高一点。

图1 IR drop和demand current

随着制成工艺的不断升级,金属连线的宽度越来越窄,致使电阻值越来越高。如果一个器件离供电点很远,其等效阻值必然会比较大。由于电源网络是全局网络,平均长度大,承载着很大的电流,因此IR drop会比较严重。

图2 电源网络等效示意图

电源噪声究竟会带来什么危害呢。芯片内部有成千上万的晶体管,这些晶体管组成内部的门电路、组合逻辑、寄存器、计数器、延迟线、状态机、以及其他逻辑功能。随着芯片的集成度越来越高,内部晶体管数量越来越大。芯片的外部引脚数量有限,为每一个晶体管提供单独的供电引脚是不现实的。芯片的外部电源引脚提供给内部晶体管一个公共的供电节点,因此内部晶体管状态的转换必然引起电源噪声在芯片内部的传递。

对内部各个晶体管的操作通常由内核时钟或片内外设时钟同步,但是由于内部延时的差别,各个晶体管的状态转换不可能是严格同步的,当某些晶体管已经完成了状态转换,另一些晶体管可能仍处于转换过程中。芯片内部处于高电平的门电路会把电源噪声传递到其他门电路的输入部分。如果接受电源噪声的门电路此时处于电平转换的不确定态区域,那么电源噪声可能会被放大,并在门电路的输出端产生矩形脉冲干扰,进而引起电路的逻辑错误。一般情况下,5%的电压降会导致15%以上的延迟。如果IRdrop发生在时序紧张的路径上,那么后果会更加严重。

除了对芯片本身工作状态产生影响外,电源噪声还会对其他部分产生影响。比如电源噪声会影响晶振、PLL、DLL的抖动特性,A/D转换电路的转换精度等。由于最终产品工作温度的变化以及生产过程中产生的不一致性,如果是由于电源噪声产生的问题,电路将非常难调试。

为了保证输出电压的稳定,需要在封装、PCB上使用去耦电容和合理的电源平面与地平面对。从目前电源完整性分析的角度看,业内普遍认为在PCB上可以处理到最高到几百兆赫兹电源完整性问题,更高频率的电源完整性问题需要在芯片和封装设计时解决。其次,在SoC内部,电源/地网络采用mesh网格设计。

芯片内部IR drop问题可以通过仿真手段加以分析,目前主流做法分为静态分析和动态分析。静态分析时,一般只考虑寄生电阻即可;动态分析时还要考虑寄生电容和寄生电感的影响。为了避免广告嫌疑,此处就不多说了。

一般foundry厂家会提供电压降的signoff标准,比如静态5%以内,动态10%以内。以上数字只是举例用,具体的标准要结合不同foundry不同工艺来看。在实际SoC设计中引起IR drop的原因有很多,有全局的,比如floor plan不合理,或者电源网络密度不够等等;也有局部的,比如某一小区域内clock buffer太多,decap很少等等。相对应的修复IR drop的方法也就有很多,要结合仿真结果,具体问题具体分析了。

-

缓解高性能存算一体芯片IR-drop问题的软硬件协同设计2025-07-11 1604

-

芯片的IR drop是什么意思呢?2023-12-06 3825

-

嵌入式系统之功耗最低化2023-11-16 357

-

什么是DC IR Drop?DC IR Drop仿真有何意义?2023-09-28 7536

-

Vivado设计套件用户指南之功耗分析和优化2023-09-14 736

-

谈谈芯片设计中的IR-drop2023-06-16 10358

-

Sigrity PowerDC是如何计算IR Drop Margin?2023-05-12 3526

-

IR Drop与封装分析2023-04-21 4730

-

IR Drop对芯片性能及功能的影响2023-04-03 6266

-

480.SOC芯片的数字低功耗方法小凡 2022-10-04

-

SoC的低功耗设计2018-02-07 1051

-

SoC低功耗设计2012-08-13 3402

-

什么是ADM (Add/Drop Multiplexer)2010-02-22 3374

全部0条评论

快来发表一下你的评论吧 !