使用ISERDES接收高速串行数据

接口/总线/驱动

描述

高速信号传输过程中,并行传输因为线路同步难,抗干扰性差等缺点逐渐被串行技术取代;通过提高传输速率的方法,串行传输也可以实现很高的传输速度。

但是,在内部处理信号时,数据信号往往是多bit信号,而传输过程中需要用到单bit串行传输技术,所以,中间需要有一个转换器,实现并串转换,这就需要用到SERDES技术。

从Virtes-4系列FPGA开始,Xilinx公司的FPGA支持LVDS电平和内置的SERDES原语,所以本文适用Virtes-4及后续系列FPGA。

本文将介绍ISERDES的IP核生成,ISERDES原语介绍,Bitslip使用以及最终的仿真结果。

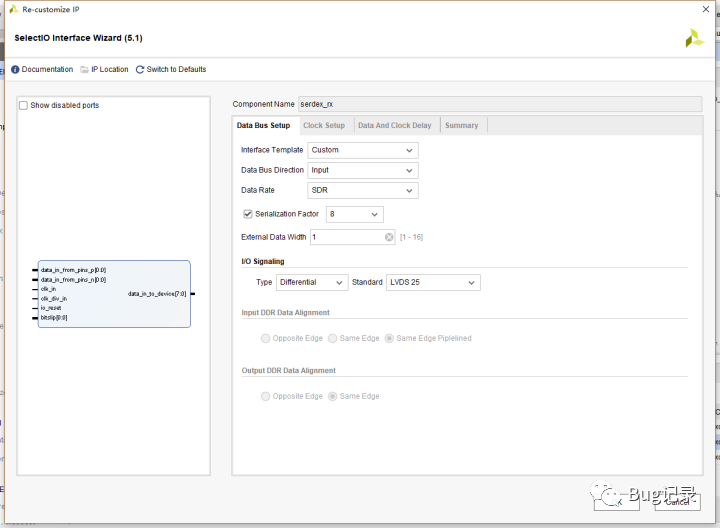

这次我们可以使用IP核简化ISERDES原语的配置,找到SelectIO IP核的配置,然后使用简化设置,如下:

数据总线设置

简单来说,

-

Interface Template:接口模板,本次数据传输并不符合预设的协议,所以选择Custom

-

Data BUS Direction:接收数据-> input

-

Data Rate: 数据总线是SDR还是DDR,

-

Serialization Factor: 串化因子,也就是需要把串行信号转换成多少bit的并行数据;

SDR Rate:可设为2,3,4,5,6,7,8; DDR Rate:可设为4,6,8,10,14;

-

External Data Width: 外部输入数据的位宽,默认设1

-

I/O signaling:设置差分还是单端以及IO电压标准

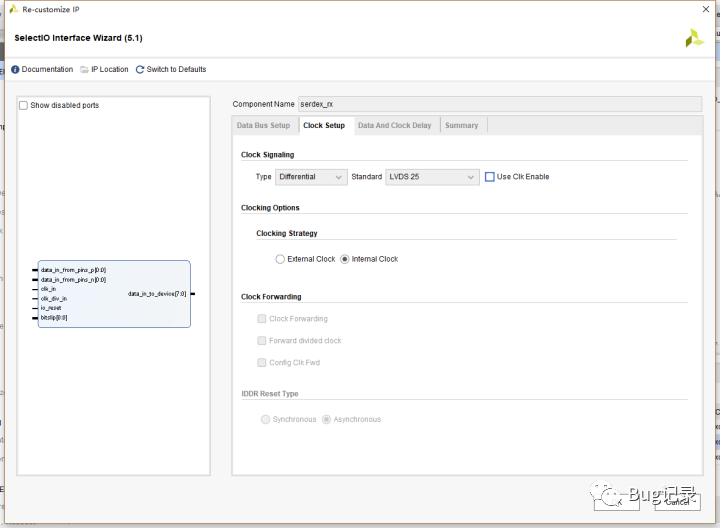

时钟设置

简单来说,

- Clock Signaling:时钟信号是差分还是单端以及IO电压标准

- Clock Strategy: External Clock:IP核内部产生并行时钟 Internal Clock:IP核需要手动输入并行时钟 在xilinx的UG471文档的P152中,提到了ISERDES的时钟要求,可以说是要求串行钟和并行钟要求相位对齐,需要注意

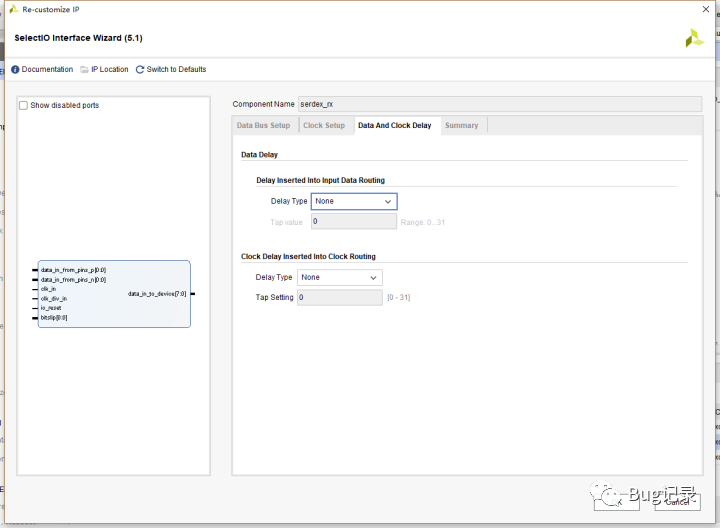

数据和延时设置

数据延时部分,这个地方先不做设置。

Summary

生成IP核之后,可以找到IP核最底层的verilog文件,它的内部实现的核心部分是ISERDES2,为此我们需要知道ISERDES2的参数内容;

ISERDES2的属性中,重点关注的是以下几个:

- DATA_RATE: 数据速率还是SDR还是DDR

- DATA_WIDTH:参考上面数据总线设置的内容

- INTERFACE_TYPE:接口类型,默认使用"NETWORKING"

- NUM_CE: 时钟使能数量,默认使用2

- SERDES_MODE:当使用级联ISERDES时,数据从Master ISERDES输入,使用一个ISERDES设为"MASTER",两个ISERDES级联使用,另一个为"SLAVE";详细可见下面讲到级联时的内容

其他的属性可以保持默认

UG471 Figure 3-2

ISERDES2重要端口设置:

- Q1-Q8: 数据输出;注意当级联时,"SLAVE" ISERDES的Q3-Q8为并行数据的第8-13位;

- SHIFTOUT:级联时使用,详见下文

- SHIFTIN:级联时使用,详见下文

- D:从IOB来的数据

- DDLY:从Idelay2来的数据,D端口从输入引脚接入后没经过处理,DDLY经过Idelay2处理;

- CLK,CLKB:串行时钟,快钟,CLKB是CLK取反处理

- CE1,CE2:快慢钟的使能

- RST:原语复位,高复位

- CLKDIV:并行钟,慢钟

- BITSLIP:bit移位功能,详见下文

时钟部分说明:

SDR下:假设接收的串行数据时钟为256MHz,解串因子为8,则CLKDIV为32MHz;

CLKDIV = CLK/DATA_WIDTH

DDR: CLKDIV = 2 * CLK/DATA_WIDTH

注意CLK和CLKDIV要相位对齐;

在NETWORKING模式下,ISERDES输出要晚于输入2个CLKDIV周期;

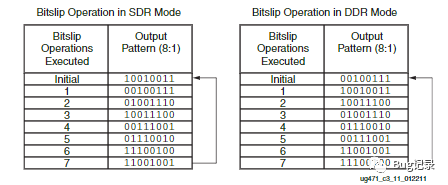

BITSLIP功能说明:

数据串转并的过程中,如果没有确定好数据边界,解串的数据也不是正确的,这个时候就需要使用BITSLIP功能:

在SDR和DDR下,bitslip移位的位数并不一样:

UG471 Figure 3-11

SDR下,一个bitslip脉冲使数据左移一位;DDR下,一个bitslip脉冲使数据右移一位或左移三位;

BITSLIP时序 UG471 Figure 3-12

可以从上图看出,BITSLIP在CLKDIV时钟下,一个完整的脉冲可以使输出数据产生相应的变化;

所以在某些传输过程中,可以先开始传输预设值,等待接收方调整Idelay和BITSLIP解出正确的预设值后,开始传输真正的数据。

ISERDES级联使用:

SDR Rate下,一个ISERDES能够解串的最大数据宽度为8;在某些ADC中,其并行数据宽度大于8位,这个时候可以使用上ISERDES的级联功能:

级联示意图 UG471 Figure 3-8

- 首先 设置一个ISERDES的SERDES_MODE属性为"MASTER",另一个为"SLAVE";

- 设置"MASTER"和"SLAVE" ISERDES2的DATA_WIDTH数据宽度为同一个数(10或14);

- 将"MASTER"的SHIFTOUT1,2连接至"SLAVE"的SHIFTIN1,2

DATA_WIDTH为10时,"SLAVE"的Q3-4为第8-9位;DATA_WIDTH为14时,"SLAVE"的Q3-8为第8-13位。

仿真结果:

找到预设值才开始传输真正的数据

注意,独立使用VCS,VERDI仿真ISERDES时,需要使用某些设置才能仿真成功

总结:

- ISERDES2可以使用SelectIO IP核设置简化原语设置流程; 但ISERDES2原语设置会更加精细

- BITSLIP功能很有用,需要用它找到数据的正确边界

-

测量串行数据信号:选择合适的示波器带宽2024-07-19 1592

-

【verilog每日一练】位拼接符的应用:如何实现串行数据的接收与输出2023-08-07 2360

-

使用OSERDES发送高速串行数据2023-06-16 2275

-

高速CAN通讯总线接收到无效串行数据是何原因?怎么解决呢?2023-05-09 2547

-

使用ISERDES接收高速串行数据2022-08-20 6772

-

怎么实现基于FPGA的具有流量控制机制的高速串行数据传输系统设计?2021-05-25 1939

-

Sync_Header Bits如何从串行数据中获取正确的Header Bits?2020-07-23 2658

-

高速串行数据挑战与TDR阻抗测试和高速串行链路的分析2017-10-12 1148

-

基于8051的Proteus仿真-串行数据转换为并行数据2016-09-01 627

-

并行数据转换为串行数据.hex2015-11-10 999

-

多FPGA系统中自定义高速串行数据接口设计2011-03-21 4053

-

80SJNB Advanced 均衡和串行数据分析方法2008-11-26 4074

全部0条评论

快来发表一下你的评论吧 !