m序列的verilog实现以及使能信号解决跨时终域问题

电子说

描述

根据《通信原理》一书可知,m序列是最长线性反馈移位寄存器的简称,它产生的伪随机序列的周期与其反馈移存器级数有关;

m序列的属性有很多,比如:

- 周期性,它的周期与它的反馈寄存器的级数有关,周期为2的级数N次方-1,比如级数为4,则周期为2^4-1,即15;

- 均衡性,一个周期内'1'的个数比'0'多一个;

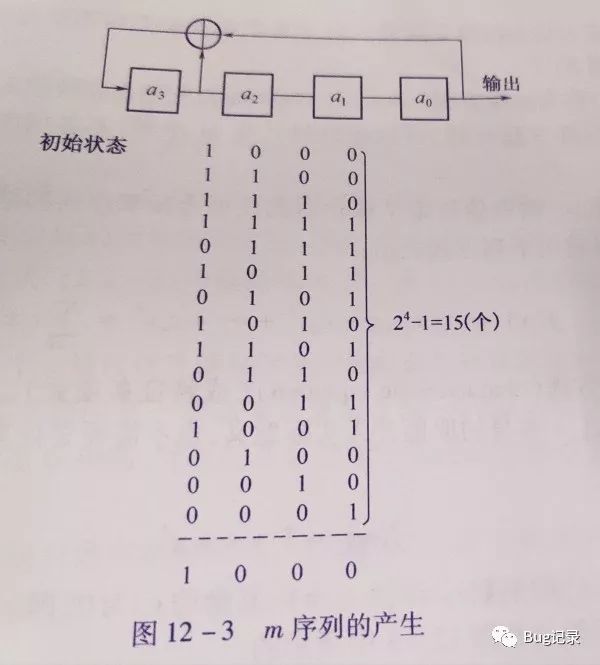

假设一个4级m序列的初始状态为(a3,a2,a1,a0) = (1,0,0,0),特征多项式为23;

移位一次,a3与a0模2相加产生新的输入a4=1^0 = 1,则新的状态为(a3,a2,a1,a0) = (1,1,0,0),输出为0;

依次移位15次后又回到初始状态(1,0,0,0)。所以4级反馈移存器的周期为15。

从书上拍下的图 图1

从书上拍下的m序列框架图 图2

从图2可以清晰的看出m序列的框架原理,只需要N位寄存器,并整体左移/右移,不断地做异或运算,产生新的值,;

以图1为例,使用特征多项式23,也就是'010 011',原始状态为'1000';参照图2的框照图,可以知道n = 4, c1 = c0 = c4 = 1, c2 = c3 = 0;

m序列的实现大致如下:

图3 m序列产生always块

可以看到,当en为高的时候,data_count会更新相应的值,同时data_out会产生新的输出值;

en信号在这里作为一个使能信号,它的作用是为了解决高速时钟下低速运行的问题;

以m序列的产生为例,假设需要产生符号速率1Mbps的伪随机序列,而FPGA的晶振为50MHz,而初学者为了在50MHz下按照1MHz的频率运行,通常会用两种方法:

- 使用各种分频的方法将50MHz分频出1MHz;

- 使用PLL等IP核将50MHz输入之后锁定输出1MHz;

而这两种方法都会产生两种时钟域(1MHz,50MHz),两个时钟域之间的数据通信通常又会牵扯到跨时钟域同步,亚稳态等问题;

那么有没有一种方法能够在50MHz下按照1MHz的频率运行?有,使用使能信号控制频率运行。

使能信号的作用就相当于一个定时器闹钟,定时会拉高一次,提醒电路该运行一次了,然后电路进入空闲状态等待下一次使能信号拉高;

这么做的好处有以下几点:

- 减少了其他的时钟,FPGA设计需要遵循尽可能少的时钟域原则;异步时钟域之间的信号同步,亚稳态问题都可以避免;

- 降低了设计难度,不需要使用IP核,不需要考虑跨时钟域的处理;

- 便于FPGA实现,因为FPGA内部的寄存器本来就有使能en端,实现起来方便;

使能信号的产生原理也很简单,使用计数器不断地计数,同时使能信号保持低电平;当计数到固定值时,使能信号拉高,计数器归零;

设计内容如下:

图3

这里INTERVAL是一个常量,可以在实例化的时候修改这个常量值;

其实这个常量值可以设为输入端口,这样可以在运行的过程中在线修改使能信号的周期,更为方便;

最后的VCS仿真图如下:

图4 仿真图

得出来的数字与图1完全对应,仿真成功!

总结:

- m序列实现原理较为简单,看图2的框图,通过这个框图实现verilog,进而实现相关的数字电路;

- 为了避免跨时钟域问题,在高速时钟下想要低速运行时,可以使用使能信号降低电路的运行频率,避免跨时钟域问题,好处可以参见上面的内容;

-

跨时钟域控制信号传输设计方案2020-10-16 1562

-

关于跨时钟域信号的处理方法2022-10-09 8556

-

quartus仿真双口RAM 实现跨时钟域通信2017-05-02 4389

-

怎么实现m序列信号发生器的设计?2021-05-10 2038

-

看看Stream信号里是如何做跨时钟域握手的2022-07-07 7011

-

FPGA电路实现:m序列及应用2023-11-06 973

-

跨时钟域信号的几种同步方法研究2012-05-09 1347

-

使用Matlab和Verilog实现fibonacci序列包括源代码和testbench2021-09-16 920

-

基于FPGA的跨时钟域信号处理——MCU2021-11-01 753

-

单位宽信号如何跨时钟域2023-04-13 2315

-

跨时钟域电路设计:单位宽信号如何跨时钟域2023-08-16 2475

全部0条评论

快来发表一下你的评论吧 !