应用工程师咨询:开关和多路复用器

描述

Mary McCarthy 和 Anthony Collins

问。 ADI公司未指定其ADG系列开关和多路复用器的带宽。有原因吗?

A.ADG系列开关和多路复用器具有非常高的输入带宽,达到数百兆赫兹。但是,带宽规格本身并没有多大意义,因为在这样的高频下,关断隔离和串扰会明显降低。例如,在1 MHz时,开关通常具有70 dB的关断隔离和–85 dB的串扰。关断隔离和串扰每十倍频程降低 20 dB。这意味着在10 MHz时,关断隔离降低到50 dB,串扰增加到–65 dB。在100 MHz时,关断隔离将降至30 dB,而串扰将增加到–45 dB。因此,仅仅考虑带宽是不够的——必须考虑关断隔离和串扰,以确定应用是否可以承受这些规格在所需高频下的下降。

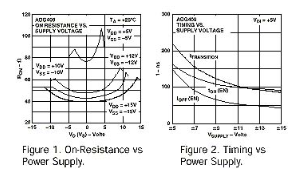

Q. 哪些开关和多路复用器可以使用低于数据手册中规定的电源工作?

A.所有ADG系列开关和多路复用器均采用低至+5 V或±5 V的电源供电。受电源电压影响的规格包括时序、导通电阻、电源电流和漏电流。降低电源电压可降低电源电流和漏电流。例如,ADG411的IS(关闭)和我D(关闭)是 ±20 nA,我D(开)在 +40°C 时为 ±125 nA,采用 ±15V 电源供电。当电源电压降至±5 V时,IS(关闭)和我D(关闭)降至 ±2.5 nA,而我D(开)在 +5°C 时降至 ±125 nA。 电源电流,IDD我党卫军和我L,采用 ±5V 电源时 +125°C 时最大 15 mA。使用 ±5V 电源时,电源电流降至 1 μA(最大值)。导通电阻和时序随着电源的减少而增加。下图显示了ADG408的时序和导通电阻如何随电源电压的变化而变化。

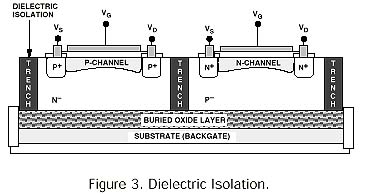

Q. 一些ADG系列开关采用DI工艺制造。这是什么?

A.DI是介电隔离的缩写。在DI工艺中,在每个CMOS开关的NMOS和PMOS晶体管之间放置一个绝缘层(沟槽)。消除了标准开关中晶体管之间的寄生结,从而形成了完全防闩锁的开关。在结隔离(不使用沟槽)中,PMOS和NMOS晶体管的N和P孔形成一个二极管,该二极管在正常工作时反向柯林斯偏置。然而,在过压或断电条件下,当模拟输入超过电源时,二极管正向偏置,与两个晶体管形成类似可控硅整流器(SCR)的电路,导致电流被显着放大,最终导致闩锁。该二极管在介质隔离开关中不存在,因此部件防闩锁。

Q. 故障保护多路复用器和通道保护器如何工作?

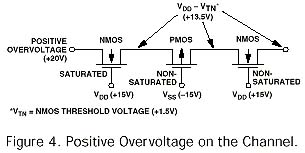

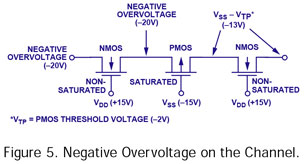

A.故障保护多路复用器或通道保护器的通道由两个NMOS和两个PMOS晶体管组成。其中一个PMOS晶体管不在直接信号路径中,而是用于将第二个PMOS的源极连接到其后栅。这具有降低阈值电压的效果,从而增加了正常工作的输入信号范围。出于同样的原因,连接 NMOS 设备的源和后门。在正常工作期间,故障保护器件作为标准多路复用器运行。当通道输入发生故障情况时,这意味着输入已超过由电源轨电压设置的某个阈值电压。阈值电压与电源轨的关系如下:对于正过压,阈值电压由下式给出在DD–在田纳西哪里在田纳西是NMOS晶体管的阈值电压(通常为1.5 V)。对于负过压,阈值电压由下式给出在党卫军–在胡志明市哪里在胡志明市是PMOS器件的阈值电压(通常为2 V)。当输入电压超过这些阈值电压时,通道上没有负载,通道的输出被箝位在阈值电压。

Q. 当存在过电压时,器件如何工作?

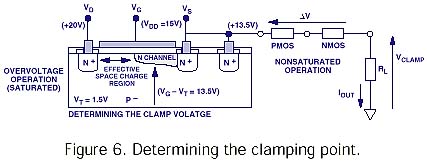

A.接下来的两个图显示了信号路径晶体管在过压条件下的工作条件。这一个演示了当对通道施加正过压时,N、P和N系列晶体管如何工作。第一个NMOS晶体管进入饱和模式,因为其漏极上的电压超过(在DD–在田纳西).NMOS 设备源处的电位等于 (在DD–在田纳西).其他 MOS 器件处于非饱和工作模式。

当对通道施加负过压时,当漏极电压超过(在党卫军–在胡志明市).与正过压一样,其他MOS器件也是非饱和的。

Q. 负载如何影响钳位电压?

A.当通道加载时,通道输出将箝位在阈值之间的电压值。例如,负载为 1 kΩ,V 时DD= 15 V,正过压,输出将箝位在DD–在田纳西– ΔV,其中 ΔV 是由于非饱和 MOS 器件通道上的 IR 压降造成的。在下面显示的示例中,钳位NMOS输出端的电压为13.5 V。其余两个MOS器件的导通电阻通常为100 Ω。因此,电流为13.5 V/(1 kΩ + 100 Ω) = 12.27 mA。这会在NMOS和PMOS两端产生1.2 V的压降,从而产生12.3 V的钳位电压。故障条件下的电流由输出上的负载决定,即在钳/RL.

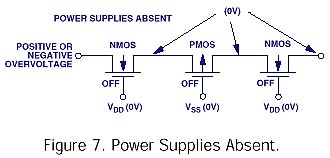

问。 故障保护多路复用器和通道保护器在电源缺电时是否正常工作。

A.是的。当电源轨关闭或暂时断开时,这些器件仍能正常工作。当 VDD和 V党卫军等于0 V,所有晶体管都关闭,如图所示,电流限制在亚纳安级。

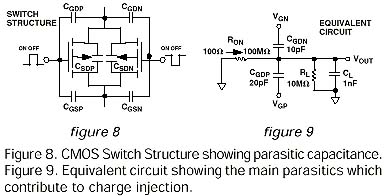

Q. 什么是“电荷注入”?

A.模拟开关和多路复用器中的电荷注入是由构成模拟开关的NMOS和PMOS晶体管相关的杂散电容引起的电平变化。下图模拟了模拟开关的结构以及与这种实现相关的杂散电容。该结构基本上由并联的NMOS和PMOS器件组成。这种布置为双极性输入信号产生熟悉的“浴缸”电阻曲线。等效电路显示了影响电荷注入效应的主要寄生电容C粤港网(NMOS 栅极到排水管)和 C国内生产总值(PMOS栅极到排水)。与PMOS器件相关的栅极漏极电容约为NMOS器件的两倍,因为要使两个器件具有相同的导通电阻,PMOS器件的面积约为NMOS的两倍。因此,相关杂散电容约为市场上典型开关的NMOS器件的两倍。

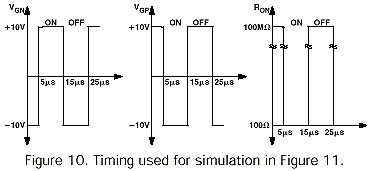

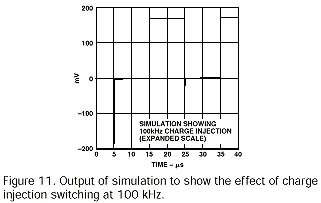

当开关打开时,正电压施加到NMOS的栅极,负电压施加到PMOS的栅极。由于杂散栅极-漏极电容不匹配,因此向漏极注入不等量的正电荷和负电荷。结果是从开关输出端去除电荷,表现为负向电压尖峰。由于模拟开关现在导通,因此负电荷通过开关的导通电阻(100 Ω)快速放电。这可以在5 μs的仿真图中看到。然后,当开关关闭时,向NMOS的栅极施加负电压,在PMOS的栅极施加正电压。结果是电荷添加到开关的输出端。由于模拟开关现在处于关闭状态,因此注入正电荷的放电路径为高阻抗(100 MΩ)。结果是负载电容存储此电荷,直到开关再次打开。仿真图清楚地表明了这一点,C上的电压L(由于电荷注入)在170 mV保持恒定,直到开关在25 μs再次导通。此时,将等量的负电荷注入输出端,从而降低C上的电压L至 0 V。在35 μs时,开关再次打开,该过程以这种循环方式继续。

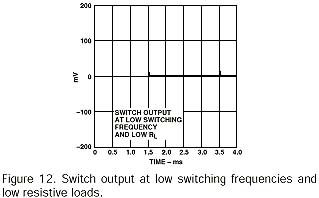

在较低的开关频率和负载电阻下,开关输出将包含正毛刺和负毛刺,因为注入的电荷在下一次开关转换之前泄漏。

Q. 如何提高模拟开关的电荷注入性能?

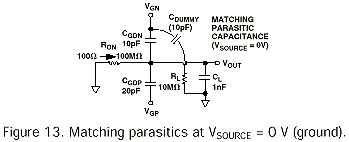

A.如上所述,电荷注入效应是由NMOS和PMOS器件的寄生栅极-漏极电容不匹配引起的。因此,如果这些寄生效应可以匹配,那么电荷注入效应将很小。这正是ADI公司CMOS开关和多路复用器所做的。通过在NMOS器件的栅极和漏极之间引入一个虚拟电容来实现匹配。

不幸的是,匹配仅在一组特定条件下完成,即当两个器件的源上的电压为0 V时。其原因是寄生电容C粤港网和 C国内生产总值,不是恒定的;它们随源电压而变化。当NMOS和PMOS的源电压变化时,它们的沟道深度会发生变化,并且随之而来的是C粤港网和 C国内生产总值.由于在 V 处的这种匹配源= 0 V 对于 V 的其他值,电荷注入效应将很明显源.

注意:电荷注入通常在数据手册中指定在这些匹配条件下,即V源= 0 V。在这些条件下,大多数开关的电荷注入通常相当好,最大值为2至3 pC。但是,对于V的其他值,电荷注入将增加源,在一定程度上取决于各个交换机。许多数据手册将显示电荷注入与源电压的函数关系图。

问:如何在应用程序中最大程度地减少这些影响?

A.电荷注入的影响是由于注入固定量的电荷而对开关输出的电压毛刺。毛刺幅度是开关输出负载电容以及开关开启和关断时间的函数。负载电容越大,输出端的电压毛刺越小,即Q = C × V,或V = Q/C,Q是固定的。当然,可能并不总是能够增加负载电容,因为它会降低通道的带宽。然而,对于音频应用,增加负载电容是减少那些不必要的“爆裂”和“咔嗒声”的有效方法。

选择导通和关断时间较慢的开关也是降低开关输出端毛刺幅度的有效方法。相同的固定量电荷在较长的时间段内注入,因此具有更长的泄漏时间段。结果是毛刺更宽,但幅度大大降低。这种技术在某些音频开关产品中得到了非常有效的应用,例如SSM-2402 / SSM-2412,其中导通时间设计为10 ms量级。

值得一提的另一点是,电荷注入性能与开关的导通电阻直接相关。一般来说,R 越低上,电荷注入性能越差。其原因纯粹是由于相关的几何形状,因为 R上通过增加 NMOS 和 PMOS 器件的面积来减少,从而增加 CGDN 和 C国内生产总值.所以权衡 R上在许多应用中,减少电荷注入也可能是一种选择。

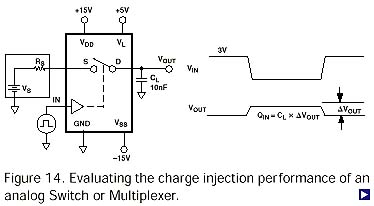

Q. 如何评估模拟开关或多路复用器的电荷注入性能?

A.评估开关电荷注入性能的最有效方法是使用类似于如下所示的设置。通过以相对较高的频率(<10 kHz)打开和关闭开关,并观察示波器上的开关输出(使用高阻抗探头),将观察到类似于图11所示的迹线。注入负载的电荷量由下式给出ΔV外× CL.哪里ΔV外是输出脉冲幅度。

审核编辑:郭婷

-

模拟开关和多路复用器的性能与应用2019-01-25 18420

-

模拟开关和多路复用器的解答2011-10-13 7620

-

PXI高密度多路复用器应用于飞机雷电防护试验2015-02-04 5809

-

你真的了解的模拟多路复用器和开关的原理和应用吗?2021-03-11 5105

-

开关和多路复用器的常见故障是什么?怎么解决?2021-06-15 3703

-

组合逻辑基础之多路复用器设计2022-08-04 4312

-

模拟开关和多路复用器的基础参数2022-11-08 1093

-

模拟开关和多路复用器2010-07-05 1151

-

复用器的多路复用2010-01-07 1434

-

模拟开关和多路复用器基础知识2017-09-19 1355

-

基础教程:模拟开关和多路复用器基础知识2018-06-04 9291

-

开关和多路复用器产品选型指南2021-03-21 1075

-

模拟开关和多路复用器基础参数简介2022-01-19 7042

-

如何改进开关/多路复用器LTspice模型2022-03-01 5086

-

模拟开关和多路复用器基础参数介绍2022-10-31 1109

全部0条评论

快来发表一下你的评论吧 !